# LATCH and DRIVER for FIP COMOS LSI

### DESCRIPTION

JEC

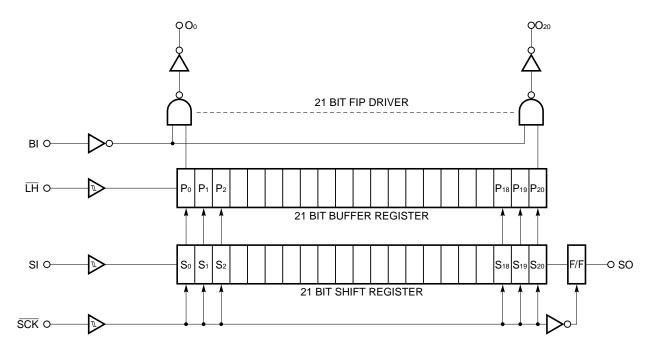

The  $\mu$ PD6323 is a latch and driver CMOS IC for FIP (Fluorescent Indicator Panel). For multiplex wiring, the  $\mu$ PD6323 is supplied with the serial interface circuit, 21 bit shift register, 21 bit data latch and 21 outputs. The serial data transfer from the data source to the  $\mu$ PD6323 is accomplished with 3 signals.

#### FEATURES

- Direct Connection to Battery enable.

- Wide Supply Voltage VDD = 8.0 to 14 (V)

- Serial Input 21 bit Shift Register Incorporated.

- Data Control by Transmission Clock (External) and Latch.

- Suitable for Static Display by Buffer Register.

- Brightness Control Enable: External Duty Control.

- Output Characteristics Vout = 40 V,

$I_{out} = 5.0 \text{ mA}.$

- Serial Interface Format: Compatible with NEC microcomputer.

- Difference of µPD6323C/BC

| PARAMETER          | SYMBOL      | μPD6323C | μPD6323BC           |

|--------------------|-------------|----------|---------------------|

| Output Voltage     | Voo to Vo20 | –25 V    | -40 V               |

| Low Supply Voltage | Vdd (L)     | —        | 4 ∨ <sup>Note</sup> |

**Notes 1.** Function Operate

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE                      |

|-------------|------------------------------|

| μPD6323C    | 28 pin Plastic DIP (400 mil) |

| μPD6323BC   | 28 pin Plastic DIP (400 mil) |

## **BLOCK DIAGRAM**

## PIN CONNECTION (Top View)

| SCK 1  | 0 | 28 Vdd             |

|--------|---|--------------------|

| BI 2   |   | 27 LH              |

| O0 3   |   | 26 SI              |

| O1 4   |   | 25 O11             |

| O2 5   |   | 24 O12             |

| O₃ 6   |   | 23 O13             |

| O4 7   |   | 22 O14             |

| O₅ 8   |   | 21 O15             |

| O6 9   |   | 20 O16             |

| O7 10  |   | 19 O17             |

| O8 11  |   | 18 O <sub>18</sub> |

| O9 12  |   | 17 O19             |

| O10 13 |   | 16 O <sub>20</sub> |

| Vss 14 |   | 15 SO              |

|        |   |                    |

### FUNCTION

| PIN No. | SYMBOL          | FUNCTION                             | INPUT/OUTPUT | EXPLANATION                                                                       |

|---------|-----------------|--------------------------------------|--------------|-----------------------------------------------------------------------------------|

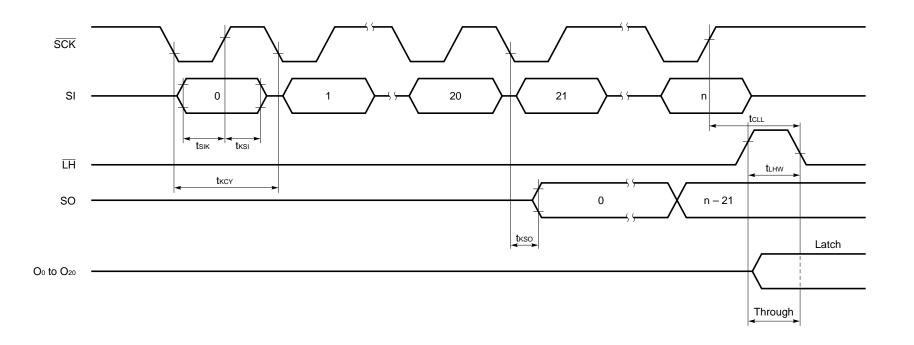

| 1       | SCK             | Serial Clock Input                   | INPUT        | The SI data are read and stored in the 21 bit shift register                      |

|         |                 |                                      |              | at the rising edge of $\overline{\text{SCK}}.$ DATA output from SO at the         |

|         |                 |                                      |              | dropping edge of SCK.                                                             |

| 2       | BI              | Blanking Input                       | INPUT        | When "L" level signal is supplied to the B1, O0 to O20 are                        |

|         |                 |                                      |              | active.                                                                           |

|         |                 |                                      |              | "H": Oo to O20 are disabled.                                                      |

|         |                 |                                      |              | Dimmer function is possible by external duty control.                             |

| 3       | O0              | Segment and Driver for               | OUTPUT       | Outputs are, Pch MOS Open Drain.                                                  |

| 4       | O1              | FIP                                  |              | These 11 Outputs are the Outputs of 11 bit output data                            |

| 5       | O2              | (O <sub>0</sub> to O <sub>10</sub> ) |              | latch, which can drive FIP directly.                                              |

| 6       | O3              |                                      |              |                                                                                   |

| 7       | O4              |                                      |              | • VDD                                                                             |

| 8       | O <sub>5</sub>  |                                      |              |                                                                                   |

| 9       | O <sub>6</sub>  |                                      |              |                                                                                   |

| 10      | O7              |                                      |              |                                                                                   |

| 11      | O8              |                                      |              |                                                                                   |

| 12      | O <sub>9</sub>  |                                      |              | ¥ 00000020<br>Vss                                                                 |

| 13      | O10             |                                      |              | 135                                                                               |

| 14      | Vss             | GND                                  |              | Connection to GND.                                                                |

| 15      | SO              | Serial Data Output                   | OUTPUT       | Serial data output at the dropping edge of $\overline{\text{SCK}}$ .              |

|         |                 |                                      |              | In case "n" pieces of $\mu$ PD6323AC are serial connected, so                     |

|         |                 |                                      |              | it is possible to connect one to next SI.                                         |

| 16      | O <sub>20</sub> | Segment and driver for               | OUTPUT       | Outputs are, Pch MOS Open Drain.                                                  |

| 17      | O19             | FIP                                  |              | These 10 outputs are the Outputs of 10 bit output data                            |

| 18      | O <sub>18</sub> | (O11 to O20)                         |              | latch, which can drive FIP directly.                                              |

| 19      | O17             |                                      |              |                                                                                   |

| 20      | O <sub>16</sub> |                                      |              |                                                                                   |

| 21      | O15             |                                      |              |                                                                                   |

| 22      | O14             |                                      |              |                                                                                   |

| 23      | O <sub>13</sub> |                                      |              |                                                                                   |

| 24      | O12             |                                      |              |                                                                                   |

| 25      | O11             |                                      |              |                                                                                   |

| 26      | SI              | Serial data Input                    | INPUT        | Serial Data Input. The SI data are read and stored in the                         |

|         |                 |                                      |              | 21 bit shift register at the rising edge of $\overline{SCK}$ .                    |

| 27      | ĹΗ              | Latch and Hold Input                 | INPUT        | When "H" level signal is supplied to the $\overline{LH}$ , the data of 21         |

|         |                 |                                      |              | bit shift register are normally transferred to the 21 bit                         |

|         |                 |                                      |              | output data latch. At the time of the rising edge of $\overline{\text{LH}}$ ; the |

|         |                 |                                      |              | data of 21 bit output data latch are held.                                        |

|         |                 |                                      |              | "L": The data of 21 bit output data latch are protected.                          |

| 28      | Vdd             | Supply Voltage at VDD                |              | V <sub>DD</sub> = 8.0 to 14 (V)                                                   |

|         |                 | terminal                             |              |                                                                                   |

\* To prevent latch up breakdown, the power should be turned ON in order VDD, logic input. It should be turned OFF in opposite order. This relationship should be followed during transition period as well.

### ABSOLUTE MAXIMUM RATINGS (TA = 25 $^{\circ}$ C)

| PARAMETER                      | SYMBOL      | RATINGS               | UNIT |

|--------------------------------|-------------|-----------------------|------|

| Supply Voltage at VDD terminal | Vdd         | 18                    | V    |

| Input Voltage                  | VIN         | -0.3 to VDD           | V    |

| Output Voltage (µPD6323C)      | Voo to Vo20 | -25 <sup>Note 1</sup> | V    |

| Output Voltage (µPD6323AC/BC)  | Voo to Vo20 | _40 <sup>Note 1</sup> | V    |

| Output Current                 | 100 to 1020 | -5.0                  | mA   |

| Operating Temperature          | ТА          | -40 to +85            | °C   |

| Storage Temperature            | Tstg        | -55 to +125           | °C   |

Notes 1. These Voltages are referenced to the  $V_{DD}$ .

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                                                                     | SYMBOL           | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------------------------------------------------|------------------|------|------|------|------|

| Operating Temperature                                                         | TA               | -40  |      | +85  | °C   |

| Operating Supply Voltage                                                      | Vdd              | 8.0  |      | 14   | V    |

| Output Voltage (µPD6323C)Note 2                                               | Voo to Vo20      |      | -19  | -24  | V    |

| Output Voltage (µPD6323AC/BC) <sup>Note 2</sup>                               | Voo to Vo20      |      | -19  | -35  | V    |

| Output Current                                                                | 100 to 1020      |      | -2.0 | -5.0 | mA   |

| Input Voltage High                                                            | Vih              | 3.5  |      | Vdd  | V    |

| Input Voltage Low                                                             | VIL              | Vss  |      | 1.0  | V    |

| SCK Frequency                                                                 | fscк             |      |      | 500  | KHz  |

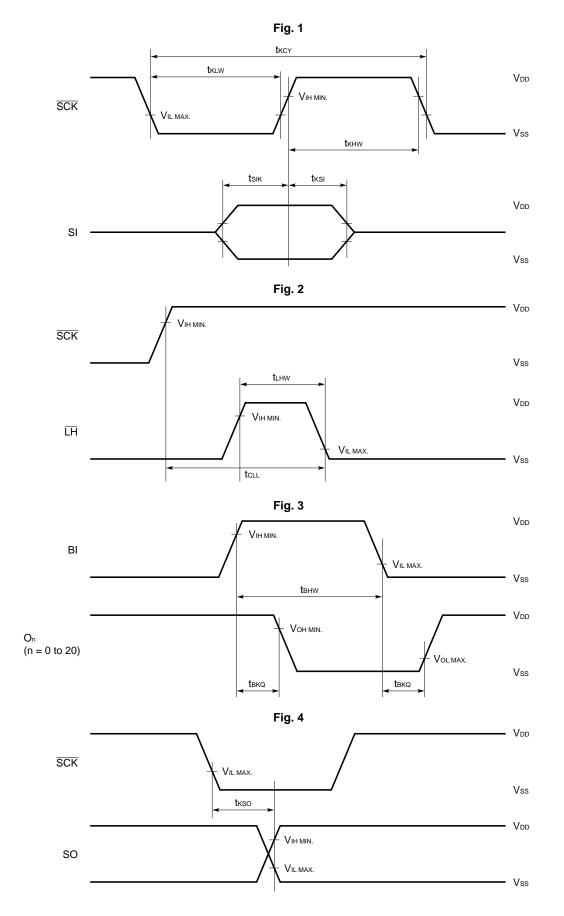

| SCK Cycle Time <sup>Note 3</sup>                                              | tксу             | 2.0  |      |      | μs   |

| SCK High Level Pulse WidthNote 3                                              | tкнw             | 0.9  |      |      | μs   |

| SCK Low Level Pulse Width Note 3                                              | tklw             | 0.9  |      |      | μs   |

| SI Setup Time to SCK 1 Note 3                                                 | tsıк             | 0.4  |      |      | μs   |

| SI Hold Time <sup>Note 3</sup>                                                | tksi             | 0.4  |      |      | μs   |

| $\overline{\text{SCK}} \to \overline{\text{LH}}$ Valid Time <sup>Note 4</sup> | toll             | 1.8  |      |      | μs   |

| LH High Level Pulse Width <sup>Note 4</sup>                                   | t <sub>LHW</sub> | 1.89 |      |      | μs   |

| BI High Level Pulse Width <sup>Note 5</sup>                                   | tвнw             | 0.4  |      |      | μs   |

Notes 2. These Voltages are referenced to the  $V_{DD}$ .

3. See Fig. 1.

4. See Fig. 2.

5. See Fig. 3.

## ELECTRICAL CHARACTERISTICS (Recommended operating conditions)

| PARAMETER                                              | SYMBOL | MIN.      | TYP. | MAX. | UNIT | TEST CONDITIONS                          |

|--------------------------------------------------------|--------|-----------|------|------|------|------------------------------------------|

| Input Leakage Current                                  | lı.    |           |      | ±10  | μA   | VIN = VSS OF VIN = VDD                   |

| SO Output Voltage High                                 | Vsoн   | Vdd - 1.0 |      | Vdd  | V    | Isoн = -1.0 mA                           |

| SO Output Voltage Low                                  | Vsol   | Vss       |      | 0.5  | V    | IsoL = 1.0 mA                            |

| Output Voltage High                                    | Vo     | Vdd - 1.5 |      | Vdd  | V    | lo = -5.0 mA                             |

|                                                        |        |           |      |      |      | Oo to O20 Output                         |

| Output Leakage Current                                 | IOLL   |           |      | 10   | μA   | V <sub>DD</sub> to V <sub>O</sub> = 40 V |

|                                                        |        |           |      |      |      | Oo to O20 Output                         |

| Supply Current at VDD Terminal                         | IDD    |           |      | 2.0  | mA   | All Input = [High]                       |

|                                                        |        |           |      |      |      | All Output = Open                        |

| Supply Voltage at VDD Terminal to                      | Vdd(H) | 3.0       |      |      | V    | Drop VDD on latch                        |

| Keep DATA                                              |        |           |      |      |      | DATA (MIN.)                              |

| Input Capacitance                                      | CIN    |           |      | 15   | pF   | f = 1.0 MHz                              |

| $\overline{SCK} \downarrow \to SO Valid Time^{Note 6}$ | tкso   |           |      | 0.5  | μs   |                                          |

| $BI \to Q_n \text{ Valid Time}^{\textbf{Note 5}}$      | tвко   |           |      | 1.8  | μs   |                                          |

| Low Supply Voltage (µPD6323BC)                         | VDD(L) | 4.0       |      |      | V    | Function Operate                         |

Notes 6. See Fig. 4.

#### SWITCHING CHARACTERISTICS

TIMING CHART

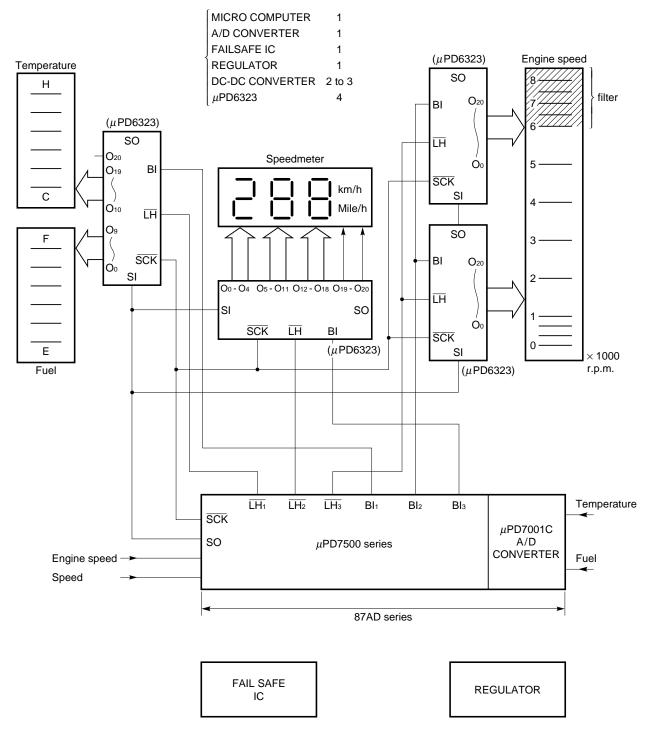

### **APPLICATION CIRCUIT**

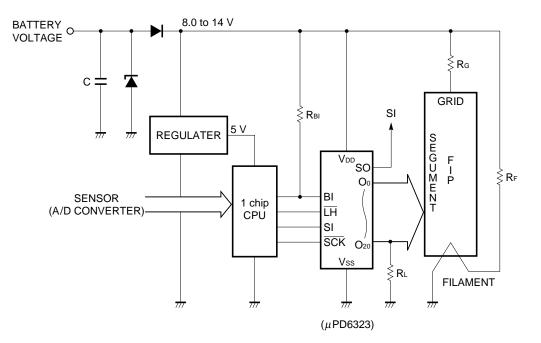

#### (1) AUTOMOTIVE DASHBOARD SYSTEM SYSTEM CONSTRUCTION

Each data of Engine speed, speed, temperature and fuel is divided to each group by  $\overline{LH}$  control. Each data is transferred by SI and  $\overline{SCK}$  control.

FIP dimmer control is capable by BI's duty control.

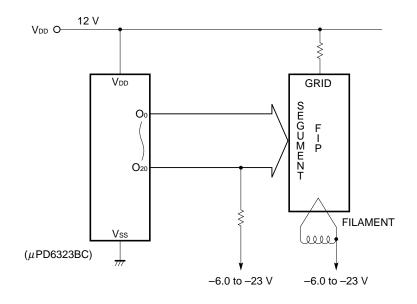

(2) 12 V FIP DRIVER CIRCUIT

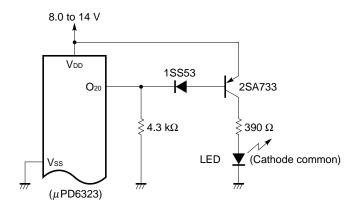

(3) HIGH VOLTAGE (18 to 35 V) FIP DRIVER CIRCUIT

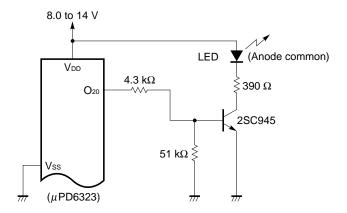

### (4) LED DRIVER CIRCUIT

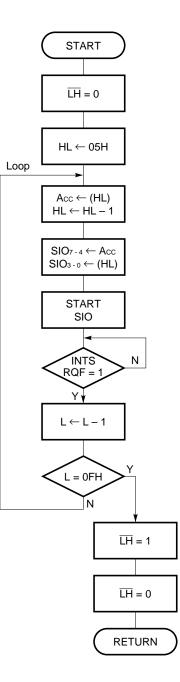

#### (5) EXAMPLE OF SOFTWARE

Using of serial I/O of  $\mu$ -COM 75 series Subroutine of 24 bit data transfer

| SI OUT : | ANP    | 6, 7            |

|----------|--------|-----------------|

|          | LHLI   | 05H             |

| LOOP :   | LAM    | HL <sup>-</sup> |

|          | TAMSIO |                 |

|          | SIO    |                 |

|          | SKI    | 2               |

|          | JCP    | \$–2            |

|          | DLS    |                 |

|          | JCP    | LOOP            |

|          | ORP    | 6, 8            |

|          | ANP    | 6, 7            |

|          | RT     |                 |

| RAM   | TRANSFER BIT |                       |                 |                       |  |

|-------|--------------|-----------------------|-----------------|-----------------------|--|

| (ADD) | 3            | 2                     | 1               | 0                     |  |

| 00H   | O3           | <b>O</b> <sub>2</sub> | O1              | <b>O</b> <sub>0</sub> |  |

| 01H   | <b>O</b> 7   | <b>O</b> 6            | <b>O</b> 5      | O4                    |  |

| 02H   | O11          | O10                   | O9              | O8                    |  |

| 03H   | O15          | O14                   | O <sub>13</sub> | O <sub>12</sub>       |  |

| 04H   | O19          | O18                   | O17             | O16                   |  |

| 05H   | O23          | O22                   | <b>O</b> 21     | O <sub>20</sub>       |  |

Allot port

P63 - LH

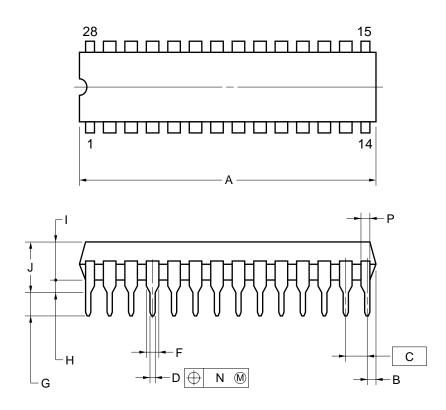

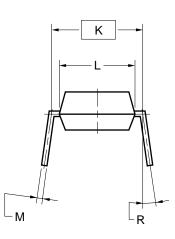

#### PACKAGE DIMENSION

$\mu$ PD6323C/BC

## 28PIN PLASTIC DIP (400 mil)

#### NOTES

- 1) Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| А    | 35.56 MAX.             | 1.400 MAX.                |

| В    | 1.27 MAX.              | 0.050 MAX.                |

| С    | 2.54 (T.P.)            | 0.100 (T.P.)              |

| D    | 0.50±0.10              | $0.020^{+0.004}_{-0.005}$ |

| F    | 1.1 MIN.               | 0.043 MIN.                |

| G    | 3.5±0.3                | 0.138±0.012               |

| Н    | 0.51 MIN.              | 0.020 MIN.                |

| I    | 4.31 MAX.              | 0.170 MAX.                |

| J    | 5.72 MAX.              | 0.226 MAX.                |

| К    | 10.16 (T.P.)           | 0.400 (T.P.)              |

| L    | 8.6                    | 0.339                     |

| М    | $0.25^{+0.10}_{-0.05}$ | $0.010^{+0.004}_{-0.003}$ |

| Ν    | 0.25                   | 0.01                      |

| Р    | 0.9 MIN.               | 0.035 MIN.                |

| R    | 0~15°                  | 0~15°                     |

|      |                        | P28C-100-400-1            |

#### **RECOMMENDED SOLDERING CONDITIONS**

The following conditions (see table below) must be met when soldering this product. Please consult with our sales offices in case other soldering process is used, or in case soldering is done under different conditions.

### TYPES OF THROUGH HOLE MOUNT DEVICE

μPD6323C/BC

| Soldering process | Soldering conditions                 | Symbol |

|-------------------|--------------------------------------|--------|

| Wave soldering    | Solder temperature: 260 °C or below, |        |

|                   | Flow time: 10 seconds or below       |        |

#### Reference

"Quality Grades On NEC Semiconductor Devices" (IEI-1209)

"NEC Semiconductor Device Reliability/Quality Controls" (IEI-1206)

"Semiconductor Device Mounting Technology Manual" (IEI-1207)

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

M4 94.11