## MOS INTEGRATED CIRCUIT $\mu$ PD16454A

The  $\mu$ PD16454A is a single-chip controller/driver for dot matrix LCD, enabling the display of up to 48 alphanumerical and kana characters and symbols (24 characters × 2 lines) each of which is composed of 5 × 7 dots. On-chip charge pump-type DC/DC converter that enables the  $\mu$ PD16454A to operate on a single 5-V power supply and the chip design aiming at tape carrier package (TCP) mounting make the  $\mu$ PD16454A ideal for portable equipment and all kinds of data terminals for which downsizing is an important consideration.

#### FEATURES

NEC

- $5 \times 7$  dot matrix LCD display controller/driver

- 24 characters × 2 lines, 1/14 duty display

- Interface with CPU 4 bits wise

- On-chip ROM and RAM

- Display data RAM (8 × 48 bits)

- Character generator RAM (8 user-defined characters;  $5 \times 7 \times 8$  bits)

- Character generator ROM (160 characters;  $5 \times 7 \times 160$  bits)

- On-chip LCD driver

- 120 segment signals

- 14 common signals

- Single 5-V power supply

- Doubling DC/DC booster generating 10 V for driving LCDs

- Total power dissipation: 2 mA max.

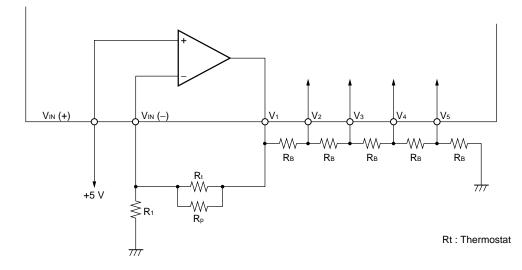

- On-chip temperature compensation circuit

- TCP mounting enabled

#### **ORDERING INFORMATION**

| Part number         | Available as |

|---------------------|--------------|

| $\mu$ PD16454AN-XXX | TCP (TAB)    |

| μPD16454AP          | Chip         |

TPC formats are created on a custom-made basis. For additional information, contact an NEC sales representative.

For purchases of chips only, additional documents on quality are required. Contact an NEC sales representative.

CLK

RS (

E

4

DB<sub>0</sub> to DB<sub>3</sub>  $\diamondsuit$

RESET

TEST

C (+)

C (–)

Vdd Vcc1

Vcc2 GND1

GND<sub>2</sub>

VIN (+)

Vin (-)

V1 V2

V4 V5

Vз

BF 🗘

μPD16454A

#### PIN FUNCTION

| Symbol      | Pin No.            | Input/Output | Connect to   | Function                                                                                                                      |

|-------------|--------------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| RS          | 138                | Input        | CPU          | Register selection signal<br>'0' instruction register (IR)<br>'1' data register (DR)                                          |

| E           | 139                | Input        | CPU          | Data reading signal                                                                                                           |

|             |                    |              |              | Reads data at the falling edge.                                                                                               |

| TEST        | 140                | Input        |              | Test pin<br>'1' = test mode<br>'0' or open = normal operation                                                                 |

| BF          | 145                | Output       | CPU          | When busy flag is '1', indicates that internal part of LCD is currently operating.<br>In test mode, functions as test output. |

| DB0 to 3    | 141 to 144         | Input/Output | CPU          | Data input signals<br>In test mode, function as output pin.                                                                   |

| RESET       | 137                | Input        | CPU          | Reset is performed with reset signal '0'                                                                                      |

| CLK         | 146                | Input        | CPU          | LCD-driving clock                                                                                                             |

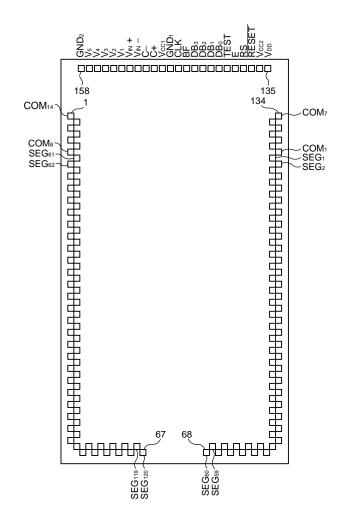

| COM1 to 14  | 128 to 134, 7 to 1 | Output       | LCD          | Common signals                                                                                                                |

| SEG1 to 120 | 127 to 68, 8 to 67 | Output       | LCD          | Segment signal outputs                                                                                                        |

| V1 to 5     | 153 to 157         |              | Power supply | LCD-driving supply voltages                                                                                                   |

| Vcc1        | 148                |              | Power supply | Power supply for logic circuits                                                                                               |

| Vcc2        | 136                |              | Power supply | Power supply for logic circuits                                                                                               |

| Vdd         | 135                |              | Power supply | Boosted power supply                                                                                                          |

| GND1        | 147                |              | Power supply | Ground for logic circuit                                                                                                      |

| GND2        | 158                |              | Power supply | Ground for high-voltage circuit                                                                                               |

| Vin (+)     | 151                |              | Power supply | Reference voltage supply                                                                                                      |

| Vin (-)     | 152                |              |              | LCD-driving supply voltage adjustment input                                                                                   |

| C (+)       | 149                |              | Capacitor    | Capacitor connection pin for booster                                                                                          |

| C (-)       | 150                |              | Capaditor    | Capacitor connection pin for booster                                                                                          |

#### **PIN CONFIGURATION (Pad Configuration)**

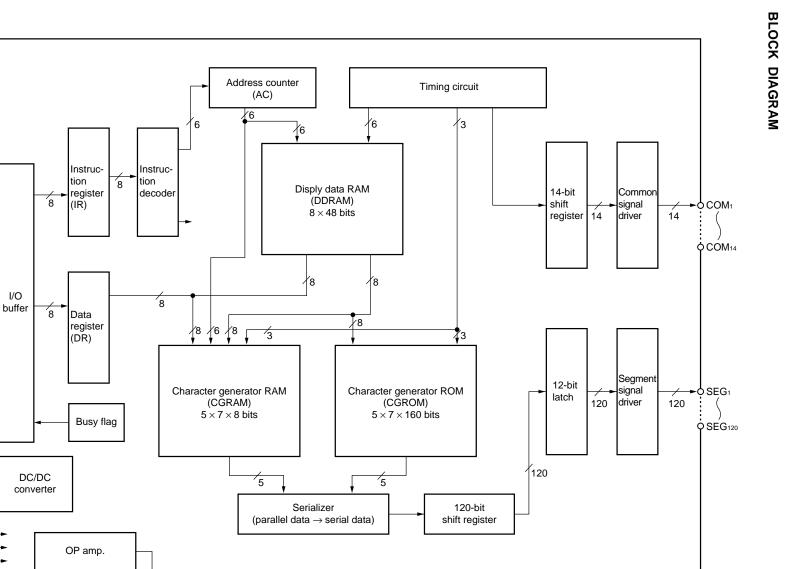

#### **BLOCK FUNCTIONS**

#### (1) Registers (IR, DR)

This LCD contains both an 8-bit instruction register (IR) and an 8-bit data register (DR).

The IR register stores display clear instruction codes and display data RAM (DDRAM) and character generaotor RAM (CGRAM) addresses.

The DR register temporarily stores data to be transferred to DDRAM and CGRAM. The IR and DR registers are selected with the register selector (RS) bit.

| RS | Register selector |

|----|-------------------|

| 0  | IR                |

| 1  | DR                |

#### (2) Busy flag (BF)

When BF = '1', this indicates that the LCD's internal circuit is currently operating. Therefore, after ascertaining that BF = '0', it is necessary to read the next instruction or display data.

#### (3) Address counter (AC)

The AC is a counter that sets addresses in DDRAM and CGRAM. When an address-setting instruction is written to the IR, the address value is set from the IR to the address counter. At the same time, which of DDRAM and CGRAM is selected is also determined.

After display data is written in DDRAM or CGRAM, the address counter's address value is automatically incremented by 1. Nevertheless, since data in CGRAM consists of 7 bytes characters, the address value is incremented by 2 only when display data has been written to the 7th line.

#### (4) Display data RAM (DDRAM)

DDRAM is a RAM that stores display data consisting of 8-bit character codes. The capacity is  $8 \times 48$  bits so that 48 characters can be stored. The correspondence between DDRAM addresses and display position on LCD is shown in Fig. 1.

#### Fig.1 Correspondence of DDRAM address and display position on LCD

| 1st      | digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

|----------|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1st line | 00    | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 2nd line | 18    | 19 | 1A | 1B | 1C | 1D | 1E | 1F | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 2A | 2B | 2C | 2D | 2E | 2F |

|          |       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

DDRAM address (hexadecimal)

#### (5) Character generator ROM (CGROM)

CGROM is a ROM that generates  $5 \times 7$ -dot character patterns from 8-bit character codes, and can generate 160 different characters in total. The correspondence of CGROM addresses and character patterns to the ASCII code is shown in Fig.2.

### Fig.2 Correspondence of CGROM address data (character codes) and character patterns (00110010 $\rightarrow$ "2")

|     |    |          |         | CGF    | ROM add   | dress |    |    |           |    |    | RO | / output | data |    |

|-----|----|----------|---------|--------|-----------|-------|----|----|-----------|----|----|----|----------|------|----|

| A10 | A9 | A8       | A7      | A6     | A5        | A4    | A3 | A2 | A1        | A0 | 04 | 03 | 02       | 01   | 00 |

|     | С  | haracter | code (D | DRAM o | utput dat | ta)   |    | Li | ne positi | on | 04 | 03 | 02       | 01   | 00 |

|     |    |          |         |        |           |       |    | 0  | 0         | 0  | 0  | 1  | 1        | 1    | 0  |

|     |    |          |         |        |           |       |    | 0  | 0         | 1  | 1  | 0  | 0        | 0    | 1  |

|     |    |          |         |        |           |       |    | 0  | 1         | 0  | 0  | 0  | 0        | 0    | 1  |

| 0   | 0  | 1        | 1       | 0      | 0         | 1     | 0  | 0  | 1         | 1  | 0  | 0  | 0        | 1    | 0  |

|     |    |          |         |        |           |       |    | 1  | 0         | 0  | 0  | 0  | 1        | 0    | 0  |

|     |    |          |         |        |           |       |    | 1  | 0         | 1  | 0  | 1  | 0        | 0    | 0  |

|     |    |          |         |        |           |       |    | 1  | 1         | 0  | 1  | 1  | 1        | 1    | 1  |

Character code and character pattern correspondence is shown in Fig.3.

| Upper 4 bits |                  |       |       |      |      |      |          |         |       |      |      |

|--------------|------------------|-------|-------|------|------|------|----------|---------|-------|------|------|

| Lower 4 bits | 0000             | 0010  | 0011  | 0100 | 0101 | 0110 | 0111     | 1010    | 1011  | 1100 | 1101 |

| XXXX0000     | CG<br>RAM<br>(1) |       |       |      |      | •    |          |         | ••••• |      |      |

| XXXX0001     | (2)              |       |       |      |      |      |          |         |       |      | Ĺ    |

| XXXX0010     | (3)              | ::    |       |      |      |      | <b></b>  | •       |       | Ņ    |      |

| XXXX0011     | (4)              |       |       |      | :    | :    | ·        |         |       |      | •    |

| XXXX0100     | (5)              |       | 4     |      |      |      | ·<br>•   | •       |       | ••   | •    |

| XXXX0101     | (6)              |       |       |      |      |      | <b>.</b> |         |       | •••• |      |

| XXXX0110     | (7)              |       |       |      | Ļ    | •    | Ļ        |         |       | •••  |      |

| XXXX0111     | (8)              | •     | •     |      |      | •    |          |         |       |      |      |

| XXXX1000     | (1)              |       |       |      |      |      | :::      |         |       |      | Ļ    |

| XXXX1001     | (2)              |       | •     |      |      |      | ·        | •       |       |      |      |

| XXXX1010     | (3)              | :     | ##    |      |      |      |          |         |       |      |      |

| XXXX1011     | (4)              |       | :     |      |      |      |          | ;:      |       |      |      |

| XXXX1100     | (5)              |       |       |      |      |      |          | •       |       |      |      |

| XXXX1101     | (6)              | ••••• | ••••• |      |      |      |          |         |       | ·`•: |      |

| XXXX1110     | (7)              |       |       | ••   | •••  | i"i  |          |         |       |      | •••  |

| XXXX1111     | (8)              |       |       |      |      | :::: |          | • • • • | •     |      |      |

Fig.3. Character Code and Character Pattern Correspondence

#### (6) Character generator RAM (CGRAM)

CGRAM is a RAM that the user can use to freely define character patterns. Eight types of  $5 \times 7$ -dot character pattern definitions are possible. The CGRAM address values (character codes) of A10 to A3 in Fig.2 are 00H to 17H (8 types). Other values (line position, output data, etc.) are the same as in Fig.2.

#### (7) Timing circuit

The timing circuit generates timing signals to activate internal circuits. Retrieve timing of RAM needed for display and internal operation timing through access from the CPU are performed on a time-share basis and thus do not interfere with each other. Therefore, to change display characters on the LCD panel, even if DDRAM has been accessed, characters other than those that have been accessed do not flicker.

#### (8) LCD-related circuit

The LCD driver circuit consists of 14 common signal drivers and 120 segment signal drivers. Each driver is automatically controlled by an internal control circuit, and outputs a driving waveform corresponding to the character pattern.

Serial data is always sent from the character pattern of the display data corresponding to the last DDRAM address, and the character pattern of the display data corresponding to the first DDRAM address (00H) is latched when inpout in the 120-bit shift register. LCD display positions are shown in Fig.1 of section (4) Display data RAM (DDRAM).

#### Interface with CPU (data transfer)

This LSI interfaces (transfers data) with CPU in 4-bit units (DB0 to DB3), but the internal register circuits (IR and DR) have 8-bit paths, therefore making it necessary to transfer 4-bit data twice.

Assuming that the 8 bits of data are numbered D0 to D7, this data is transferred in the following sequence: first the upper 4 bits (D4 to D7), then the lower 4 bits (D0 to D3). The busy flag check is performed before the upper 4 bits are transferred, and is not necessary before transferring the 4 lower bits.

If data is transferred without checking BF, taking 10 CLK cycles or more is necessary between previous 8-bit data transfer and next transfer (CLK = 1/fc).

#### INSTRUCTIONS

The instructions for this LSI are shown in Table 1 below.

|  | Table 1 | Instruction List |  |

|--|---------|------------------|--|

|--|---------|------------------|--|

| Instruction               |    |    |    |    | Code  |                           |       |         |    | Description                                                                                                                             |

|---------------------------|----|----|----|----|-------|---------------------------|-------|---------|----|-----------------------------------------------------------------------------------------------------------------------------------------|

| manuchon                  | RS | D7 | D6 | D5 | D4    | D3                        | D2    | D1      | D0 | Description                                                                                                                             |

| Display On/Off            | 0  | 0  | 0  | 0  | 0     | 1                         | D     | *       | *  | Full display On/Off<br>D : '1' (ON), '0' (OFF)                                                                                          |

| CGRAM<br>Address Set      | 0  | 0  | 0  |    | С     | GRAM                      | addre | SS      |    | CGRAM address set.<br>Transfer of subsequent data is of CGRAM.                                                                          |

| DDRAM<br>Address Set      | 0  | 1  | *  |    | D     | DRAM                      | addre | SS      |    | DDRAM address set.<br>Transfer of subsequent data is of DDRAM<br>data.                                                                  |

| CGRAM/DDRAM<br>Data Write | 1  |    |    | -  | use C | e data<br>GRAM<br>re igno |       | occupie | es | Data is written in CGRAM or DDRAM.<br>The internal address counter (AC) is<br>automatically incremented by one following<br>data write. |

**Remark** \* in the above table indicates that the value may be either 0 to 1.

#### Initialization using the reset signal (RESET)

When the reset signal ( $\overline{\text{RESET}}$ ) is activated ( $\overline{\text{RESET}}$  = 0) for 10 CLK cycles (CLK = 1/fc) or more, initialization is performed as follows.

(1) Display ON/OFF

Set to OFF (D = 0)

(2) DDRAM address set

Set to DDRAM address 00H

When data write is performed under this condition, data is written to DDRAM address 00H.

#### ABSOLUTE MAXIMUM RATINGS (Ta = +25 °C, GND1 = GND2 = 0 V)

| Parameter                      | Symbol          | Ratings                      | Unit |

|--------------------------------|-----------------|------------------------------|------|

| Logic Supply Voltage           | Vcc             | -0.3 to +7.0                 | V    |

| Driver Input Voltage           | Vı              | -0.3 to Vcc +0.3             | V    |

| Logic Output Voltage           | Vo1             | –0.3 to Vcc +0.3             | V    |

| Driver Supply Voltage          | Vdd             | –0.3 to +15                  | V    |

| Driver's Driver Input Voltage  | $V_2$ to $V_5$  | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Driver's Driver Output Voltage | V1              | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Driver Output Voltage          | V <sub>O2</sub> | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature            | Tstg            | -40 to +125                  | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                     | Symbol | MIN. | TYP. | MAX. | Unit |

|-------------------------------|--------|------|------|------|------|

| Logic Supply Voltage          | Vcc    | 4.75 | 5    | 5.25 | V    |

| Operating Ambient Temperature | Topt   | -30  | 25   | 85   | °C   |

#### DC CHARACTERISTICS (Ta = -30 to +85 °C, Vcc = 5 V 5 ± 5%)

| Parameter                                   | Symbol | Conditions                                                                                                    | MIN.    | TYP. | MAX.    | Unit |

|---------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------|---------|------|---------|------|

| High-Level Input Voltage 1                  | VIH1   | E, RESET, CLK, input excluded                                                                                 | 0.7 Vcc |      |         | V    |

| Low-Level Input Voltage 1                   | VIL1   |                                                                                                               |         |      | 0.3 Vcc | V    |

| High-Level Input Voltage 2                  | VIH2   | E, RESET, CLK input                                                                                           | 0.8 Vcc |      |         | V    |

| Low-Level Input Voltage 2                   | VIL2   |                                                                                                               |         |      | 0.2 Vcc | V    |

| Hysteresis voltage                          | Vн     |                                                                                                               |         | 0.1  |         | V    |

| High-Level Output Voltage                   | Vон    | Іон = −1 mA                                                                                                   | 0.9 Vdd |      |         | V    |

| Low-Level Output Voltage                    | Vol    | lo∟ = 1 mA                                                                                                    |         |      | 0.1 Vcc | V    |

| High-Level Input Leak Current               | Іін1   | TEST excluded, VIN = Vcc                                                                                      |         |      | 1       | μΑ   |

| High-Level Input Leak Current               | Іін2   | TEST, VIN = Vcc                                                                                               |         |      | 6       | mA   |

| Low-Level Input Lead Current                | ١L     | Vin = 0 V                                                                                                     | -1      |      |         | μΑ   |

| Common Output Impedance                     | Rсом   | Io  = 50 µA                                                                                                   |         | 1.5  | 58      | kΩ   |

| Segment Output Impedance                    | Rseg   | Io  = 50 µA                                                                                                   |         | 1.5  | 76      | kΩ   |

| Logic Supply Voltage<br>(Total consumption) | lcc    | $R_1 = 33 k\Omega$ $R_P = 27 k\Omega$ $R_B = 22 k\Omega$ $f_C = 250 \text{ kHz}$                              |         | 1    | 2       | mA   |

| Driver Supply Voltage<br>(Boosted voltage)  | Vdd    | R <sub>1</sub> = 33 kΩ<br>R <sub>P</sub> = 27 kΩ<br>R <sub>B</sub> = 22 kΩ<br>External capacitor of 1 $\mu$ F | 1.9 Vcc |      | 2 Vcc   | V    |

| High-Level Output Voltage (V1 pin)          | Voh2   | $I_{OH} = -1 \text{ mA}$<br>$V_{IN} (+) = V_{DD}$<br>$V_{IN} (-) = 0 \text{ V}$                               | 0.9 Vdd |      |         | V    |

| Low-Level Output Voltage (V1 pin)           | Vol2   | $I_{OL} = 10 \ \mu A$<br>$V_{IN} (+) = 0 \ V$<br>$V_{IN} (-) = V_{DD}$                                        |         |      | 0.1 Vdd | V    |

\* TYP. is reference value at Ta = +25 °C.

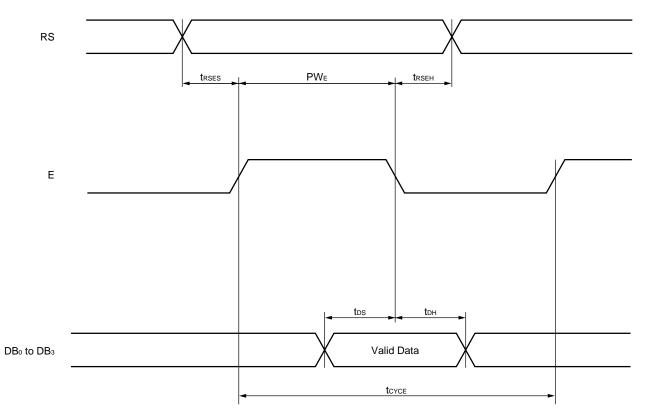

#### AC CHARACTERISTICS (Ta = -30 to +85 °C, Vcc = 5 V ± 5%)

| Parameter           | Symbol        | Conditions | MIN.  | TYP. | MAX. | Unit |

|---------------------|---------------|------------|-------|------|------|------|

| Operating Frequency | fc            |            | 160   | 250  | 500  | kHz  |

| Enable Cycle Time   | <b>t</b> CYCE |            | 1 000 |      |      | ns   |

| Enable Pulse Width  | PWE           |            | 450   |      |      | ns   |

| RS • E Setup Time   | trses         |            | 100   |      |      | ns   |

| RS • E Hold Time    | trseн         |            | 100   |      |      | ns   |

| Data Setup Time     | tos           |            | 100   |      |      | ns   |

| Data Hold Time      | tон           |            | 100   |      |      | ns   |

\* TYP. is reference value at  $T_a = +25 \ ^{\circ}C$ .

#### AC CHARACTERISTIC WAVEFORM

#### Write Operation

#### OSCILLATION FREQUENCY and LCD FRAME FREQUENCY CORRESPONDENCE

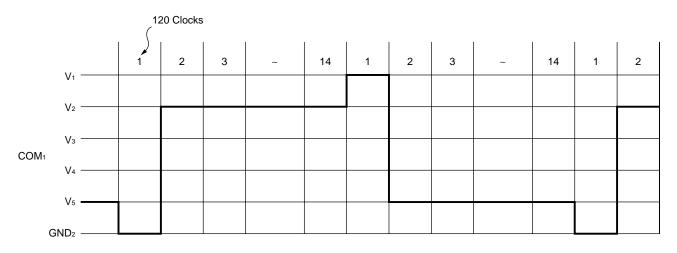

The correspondence between the oscillation frequency of 250 kHz and the LCD frame frequency is shown in Fig.4 below.

#### Fig.4 Oscillation Frequency and LCD Frame Frequency Correspondence

1 frame = 4  $\mu$ s × 120 × 14 = 6 720  $\mu$ s = 6.72 ms

| Signal | Display Mode | +                | _              |

|--------|--------------|------------------|----------------|

| СОМ    | Lit          | GND <sub>2</sub> | V1             |

|        | Not lit      | V2               | V <sub>5</sub> |

| SEG    | Lit          | GND <sub>2</sub> | V1             |

|        | Not lit      | V4               | V3             |

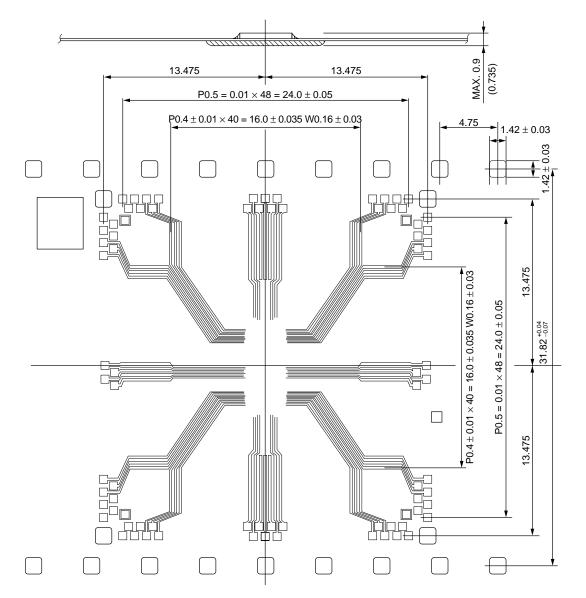

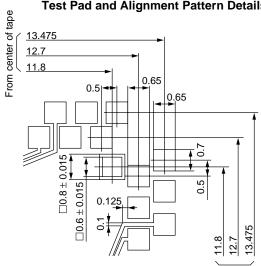

REFERENCE 1 : STANDARD TCP DRAWING (µPD16454AN-051)

Note 1. Measurements between brackets are for referency only.

- **2.** Non-specified tolerances are  $\pm 0.05$  mm.

- 3. This drawing is viewed from wire-patterned face.

From center of tape

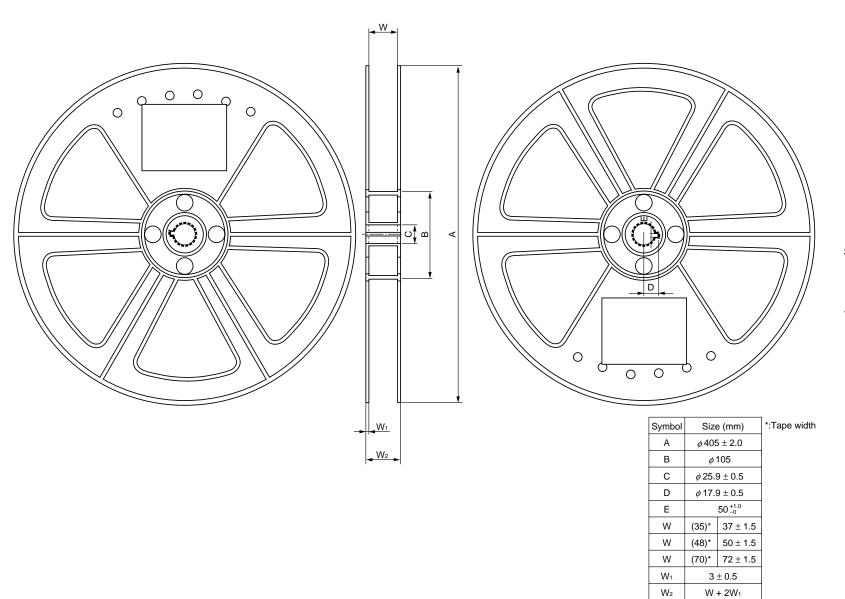

# REFERENCE 2 : TCP SHIPPING RELL ( $\phi$ 405 mm)

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5