**UC3842**

#### **DESCRIPTION**

The UC3842 is available in an 8-Pin mini-DIP the necessary features to implement off-line, fixed-frequency current-mode control schemes with a minimal external parts count. This technique results in improved line regulation, enhanced load response characteristics, and a simpler, easier to design control loop. Topological advantages include inherent pulse-by-pulse current limiting.

Protection circuitry includes built-in undervoltage lock-out and current limiting. Other features include fully-latched operation, a 1% trimmed bandgap reference, and start-up current less than 1mA.

These devices feature a totem-pole output designed to source and sink high peak current from a capacitive load, such as the gate of a power MOSFET. Consistent with N-channel power devices, the output is low in the OFF-state.

### **FEATURES**

- Low start-up current (≤1mA)

- Automatic feed-forward compensation

- Pulse-by-pulse current limiting

- Enhanced load response characteristics

- Undervoltage lock-out with hysteresis

- Double pulse suppression

- High current totem-pole output

- Internally-trimmed bandgap reference

- 400kHz operation, guaranteed min

#### PIN CONFIGURATIONS

#### **APPLICATIONS**

- Off-line switched mode power supplies

- DC-to-DC converters UC3842

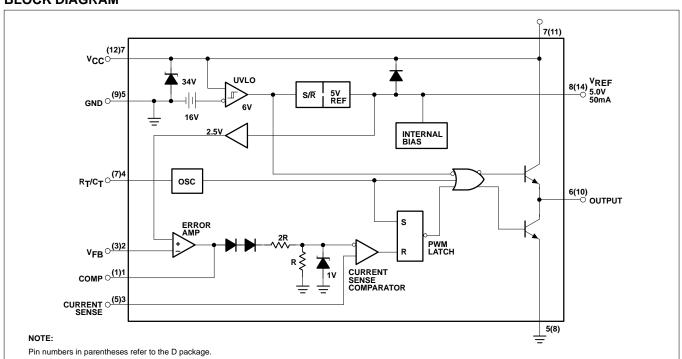

#### **BLOCK DIAGRAM**

UC3842

### **ORDERING INFORMATION**

| DESCRIPTION                               | TEMPERATURE RANGE | ORDER CODE | DWG#  |

|-------------------------------------------|-------------------|------------|-------|

| 8-Pin Plastic Dual In-Line Package (DIP)  | 0 to +70°C        | UC3842N    | 0404B |

| 14-Pin Plastic Small Outline (SO) Package | 0 to +70°C        | UC3842D    | 0405B |

# ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL            | PARAMETER                                                                                              | RATING      | UNIT          |

|-------------------|--------------------------------------------------------------------------------------------------------|-------------|---------------|

| V <sub>CC</sub>   | Supply voltage (I <sub>CC</sub> <30mA)                                                                 |             | Self-Limiting |

| Vcc               | Supply voltage (low impedance source)                                                                  | 30          | V             |

| I <sub>OUT</sub>  | Output current <sup>2, 3</sup>                                                                         | ±1          | А             |

|                   | Output energy (capacitive load)                                                                        | 5           | μJ            |

|                   | Analog inputs (Pin 2, Pin 3)                                                                           | -0.3 to 6.3 | V             |

|                   | Error amp output sink current                                                                          | 10          | mA            |

| $P_{D}$           | Power dissipation at $T_A \le 70^{\circ}C$<br>(derate 12.5mW/°C for $T_A > 70^{\circ}C$ ) <sup>2</sup> | 1           | W             |

| T <sub>STG</sub>  | Storage temperature range                                                                              | -65 to +150 | °C            |

| T <sub>SOLD</sub> | Lead temperature (soldering, 10sec max)                                                                | 300         | °C            |

### NOTES:

- All voltages are with respect to Pin 5; all currents are positive into the specified terminal.

See section in application note on "Power Dissipation Calculation".

This parameter is guaranteed, but not 100% tested in production.

UC3842

# DC AND AC ELECTRICAL CHARACTERISTICS

$0 \hspace{-0.5mm} \le \hspace{-0.5mm} T_J \hspace{-0.5mm} \le \hspace{-0.5mm} 70^{\circ} C \text{ for UC3842; V}_{CC} \hspace{-0.5mm} = \hspace{-0.5mm} 15 \text{V; R}_T \hspace{-0.5mm} = \hspace{-0.5mm} 10 \text{kW; C}_T \hspace{-0.5mm} = \hspace{-0.5mm} 3.3 \text{nF, unless otherwise specified.}$

| SYMBOL              | PARAMETER                                 | TEST CONDITIONS                                         |      | UC3842 |      |       |

|---------------------|-------------------------------------------|---------------------------------------------------------|------|--------|------|-------|

| STMBOL              |                                           |                                                         | Min  | Тур    | Max  | UNIT  |

| Referenc            | e section                                 |                                                         |      |        |      |       |

| V <sub>OUT</sub>    | Output voltage                            | T <sub>J</sub> =25°C, I <sub>O</sub> =1mA               | 4.90 | 5.00   | 5.10 | ٧     |

|                     | Line regulation                           | 12≤V <sub>IN</sub> ≤25V                                 |      | 6      | 20   | mV    |

|                     | Load regulation                           | 1≤I <sub>O</sub> ≤20mA                                  |      | 6      | 25   | mV    |

|                     | Temp. stability <sup>1</sup>              |                                                         |      | 0.2    | 0.4  | mV/°C |

|                     | Total output variation <sup>1</sup>       | Line, load, temp.                                       | 4.82 |        | 5.18 | V     |

| V <sub>NOISE</sub>  | Output noise voltage <sup>1</sup>         | 10Hz≤f≤10kHz, T <sub>J</sub> =25°C                      |      | 50     |      | μV    |

|                     | Long-term stability <sup>1</sup>          | T <sub>J</sub> =125°C, 1000 Hrs.                        |      | 5      | 25   | mV    |

|                     | Output short-circuit                      | T <sub>J</sub> =25                                      | -30  | -100   | -130 | mA    |

|                     | Output short-circuit                      | -55 <t<sub>J≤0°C</t<sub>                                | -30  | -100   | -180 | mA    |

| Oscillato           | r section                                 |                                                         |      |        |      |       |

|                     | Initial accuracy                          | T <sub>J</sub> =25°C                                    | 47   | 52     | 57   | kHz   |

|                     | Voltage stability                         | 12≤V <sub>CC</sub> ≤25V                                 |      | 0.2    | 1    | %     |

|                     | Temp. stability <sup>1</sup>              | T <sub>MIN</sub> ≤T <sub>J</sub> ≤T <sub>MAX</sub>      |      | 5      |      | %     |

|                     | Amplitude                                 | V <sub>PIN 4</sub> peak-to-peak                         |      | 1.7    |      | V     |

| Error am            | p section                                 |                                                         |      |        |      |       |

|                     | Input voltage                             | V Pin 1=2.5V                                            | 2.42 | 2.50   | 2.58 | V     |

| I <sub>BIAS</sub>   | Input bias current                        |                                                         |      | -0.3   | -2   | μА    |

| A <sub>VOL</sub>    |                                           | 2≤V <sub>O</sub> ≤4V                                    | 65   | 90     |      | dB    |

|                     | Unity gain bandwidth <sup>1</sup>         | T <sub>J</sub> =25°C                                    | 0.7  | 1      |      | MHz   |

|                     | Unity gain bandwidth                      | T <sub>MIN</sub> <t<sub>J<t<sub>MAX</t<sub></t<sub>     | 0.5  |        |      | MHz   |

| PSRR                | Power supply rejection ratio              | 12≤V <sub>CC</sub> ≤25V                                 | 60   | 70     |      | dB    |

| I <sub>SINK</sub>   | Output sink current                       | V <sub>PIN 2</sub> =2.7V, V <sub>PIN 1</sub> =1.1V      | 2    | 6      |      | mA    |

| I <sub>SOURCE</sub> | Output source current                     | V <sub>PIN 2</sub> =2.3V, V <sub>PIN 1</sub> =5V        | -0.5 | -0.8   |      | mA    |

|                     | V <sub>OUT</sub> High                     | V <sub>PIN 2</sub> =2.3V, R <sub>L</sub> =15k to ground | 5    | 6      |      | V     |

|                     | V <sub>OUT</sub> Low                      | V <sub>PIN 2</sub> =2.7V, R <sub>L</sub> =15k to Pin 8  |      | 0.7    | 1.1  | V     |

| Current s           | sense section                             | •                                                       | -    |        |      |       |

|                     | Gain <sup>2, 3</sup>                      |                                                         | 2.85 | 3      | 3.15 | V/V   |

|                     | Maximum input signal <sup>2</sup>         | V <sub>PIN 1</sub> =5V                                  | 0.9  | 1      | 1.1  | V     |

| PSRR                | Power supply rejection ratio <sup>2</sup> | 12≤V <sub>CC</sub> ≤25V                                 |      | 70     |      | dB    |

| I <sub>BIAS</sub>   | Input bias current                        |                                                         |      | -2     | -10  | μΑ    |

| 20                  | Delay to output <sup>1</sup>              |                                                         |      | 150    | 300  | ns    |

UC3842

### DC AND AC ELECTRICAL CHARACTERISTICS

$0≤T_J≤70$ °C for UC3842; V<sub>CC</sub>=15<sup>4</sup>; R<sub>T</sub>=10kΩ; C<sub>T</sub>=3.3nF, unless otherwise specified

| SYMBOL          | PARAMETER                                                              | TEST CONDITIONS                            | UC3842 |      |      |      |

|-----------------|------------------------------------------------------------------------|--------------------------------------------|--------|------|------|------|

|                 |                                                                        |                                            | Min    | Тур  | Max  | UNIT |

| Output s        | ection                                                                 |                                            | •      |      |      |      |

| V <sub>OL</sub> | Output Low-Level                                                       | I <sub>SINK</sub> =20mA                    |        | 0.1  | 0.4  | V    |

|                 |                                                                        | I <sub>SINK</sub> =200mA                   |        | 1.5  | 2.2  |      |

| V <sub>OH</sub> | Output High-Level                                                      | I <sub>SOURCE</sub> =20mA                  | 13     | 13.5 |      |      |

|                 |                                                                        | I <sub>SOURCE</sub> =200mA                 | 12     | 13.5 |      | V    |

| t <sub>R</sub>  | Rise time                                                              | C <sub>L</sub> =1nF                        |        | 50   | 150  | ns   |

| t <sub>F</sub>  | Fall time                                                              | C <sub>L</sub> =1nF                        |        | 50   | 150  | ns   |

| Undervo         | Itage lockout section                                                  |                                            |        |      |      |      |

|                 | Start threshold                                                        |                                            | 14.5   | 16   | 17.5 | V    |

|                 | Min. operating voltage after turn on                                   |                                            | 8.5    | 10   | 11.5 | V    |

| PWM sec         | ction                                                                  |                                            |        |      |      |      |

|                 | Maximum duty cycle                                                     |                                            | 93     | 97   | 100  | %    |

|                 | Minimum duty cycle                                                     |                                            |        |      | 0    |      |

| Total sta       | ndby current                                                           |                                            |        |      |      |      |

|                 | Start-up current                                                       |                                            |        | 0.5  | 1    | mA   |

| I <sub>CC</sub> | Operating supply current                                               | V <sub>PIN 2</sub> =V <sub>PIN 3</sub> =0V |        | 11   | 17   | mA   |

|                 | V <sub>CC</sub> zener voltage                                          | I <sub>CC</sub> =25mA                      |        | 34   |      | V    |

| Maximur         | n operating frequency section                                          |                                            | -      | -    |      |      |

|                 | Maximum operating frequency for all functions operating cycle-by-cycle |                                            | 400    |      |      | kHz  |

1103

# NOTES:

- 1. These parameters, although guaranteed, are not 100% tested in production.

- 2. Parameter measured at trip point of latch with  $V_{PIN\ 2}=0$ .

- 3. Gain defined as:  $A = \frac{\Delta V_{PIN~1}}{\Delta V_{PIN~3}}~;~0~\leq~V_{PIN~3}~\leq~0.8V$

## **UNDERVOLTAGE LOCKOUT**

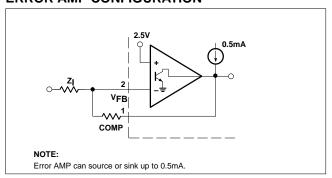

## **ERROR AMP CONFIGURATION**

UC3842

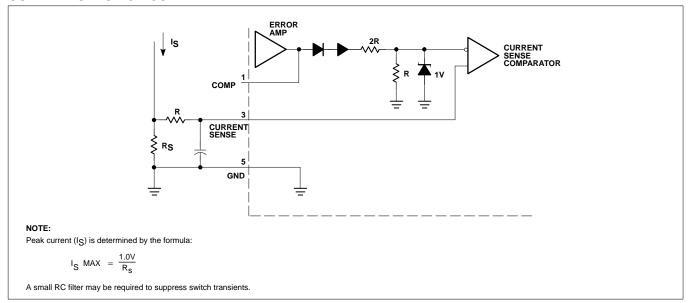

### **CURRENT SENSE CIRCUIT**

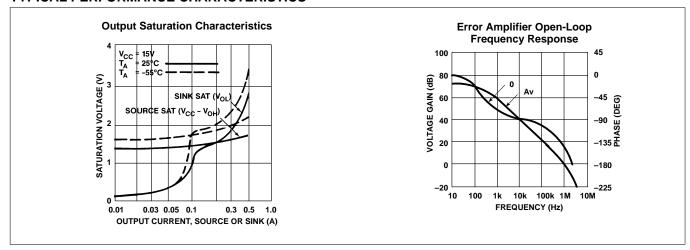

## TYPICAL PERFORMANCE CHARACTERISTICS

UC3842

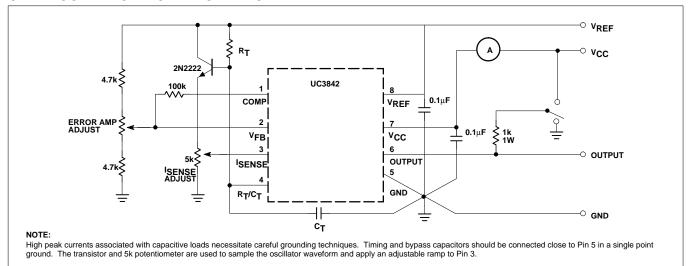

#### **OPEN-LOOP LABORATORY TEST FIXTURE**

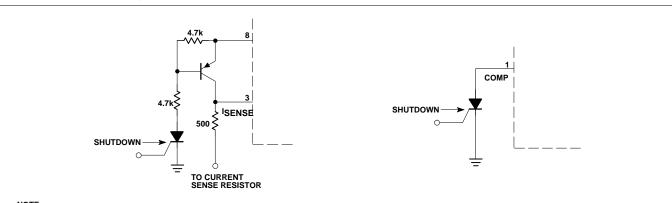

### **SHUTDOWN TECHNIQUES**

#### NOTE:

Shutdown of the UC3842 can be accomplished by two methods; either raise Pin 3 above 1V or pull Pin 1 below a voltage two diode drops above ground. Either method causes the output of the PWM comparator to be high (refer to Block Diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at Pins 1 and/or 3 is removed. In the examples shown, an externally-latched shutdown may be accomplished by adding an SCR which will be reset by cycling V<sub>CC</sub> below the lower UVLO threshold (10V). At this point all internal bias is removed, allowing the SCR to reset.

UC3842

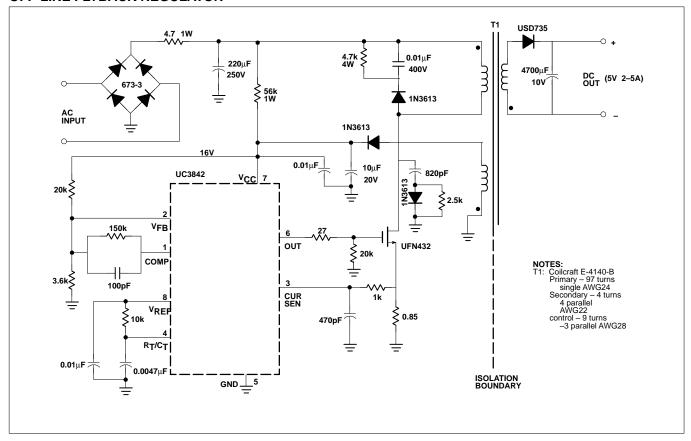

#### **OFF-LINE FLYBACK REGULATOR**

### **SPECIFICATIONS**

Input line voltage: 90V<sub>AC</sub> to 130V<sub>AC</sub>

Input frequency: 50 or 60Hz

Switching frequency: 40kHz±10%

Output power: 25W maximum

Output voltage:  $5V\pm5\%$ Output current: 2 to 5ALine regulation: 0.01%/VLoad regulation:  $8\%/A^*$

Efficiency @ 25 W,

$V_{IN}$ =90 $V_{AC}$ : 70%  $V_{IN}$ =130 $V_{AC}$ : 65% Output short-circuit current: 2.5A average

### NOTE:

This circuit uses a low-cost feedback scheme in which the DC voltage developed from the primary-side control winding is sensed by the UC3842 error amplifier. Load regulation is therefore dependent on the coupling between secondary and control windings, and on transformer leakage inductance. For applications requiring better load regulation, a UC1901 Isolated Feedback Generator can be used to directly sense the output voltage.

UC3842

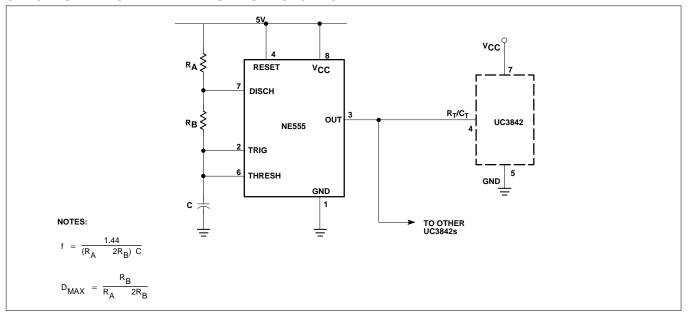

# SYNCHRONIZATION AND MAXIMUM DUTY CYCLE CLAMP

1107

August 31, 1994