## **CT2 I/Q Modulator and Clock Circuitry**

#### Description

U3770M is a quadrature modulator realized with MATRA MHS' advanced 0.8 micron CMOS process. The IC is especially designed for CT2 application in con-junction with TELEFUNKEN's RF/IF signal

processor U2760B and a CT2 baseband controller (i.e., AMD PhoX<sup>TM</sup> controller Am79C4xx). Together with TELEFUNKEN's PLL IC U2783B and the GaAs front end U7001BG, a complete CT2 chip set is available.

#### Features

- Programmable 0.8/1.6 MHz quadrature modulated carrier generation

- More than 30 dB LO and sideband suppression

- 18.432 MHz CMOS level clock generation

- Supply voltage range 2.7 to 3.3 V

- Low power consumption, typical 6 mW

- SO16 package or die form

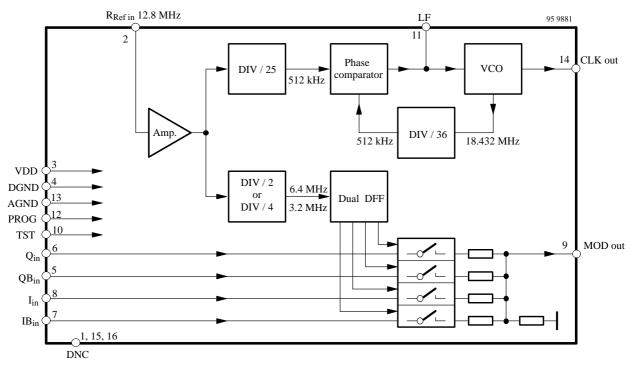

#### **Block Diagram**

U3770M

#### **Functional Description**

U3770M has been designed to reduce power consumption and cost of CT2 devices. An innovative CMOS I,Q modulator with an extremely low current provides all the advantages of I,Q modulation:

- No requirement for FM deviation tuning

- Eliminates the Gaussian filter

- Simplifies the power ramping control

The modulated output carrier can be programmed to be 0.8 MHz or 1.6 MHz by the PROG control pin.

The typical supply voltage is 3 V @ 2 mA.

To reduce overall system cost, an internal PLL generates a 18.432 MHz clock signal from the system 12.8 MHz reference oscillator. This way, only one crystal oscillator is needed in the complete CT2 device.

Internally, the 12.8 MHz reference signal is fed into a shaping amplifier and then into two logic dividers, to generate a 512 kHz and a programmable 3.2 or 6.4 MHz clock. This clock is divided by 4 by two D flip-flops. The flip-flop outputs drive the four analog switches in quadrature. A pair of analog switches make a local oscillator (LO) suppression mixer. By summing the other pair outputs, we obtain both LO and sideband suppression, of more than -30 dBc.

The 512 kHz clock drives a frequency synthesizer. The VCO runs at a fixed frequency of 18.432 MHz. The VCO control voltage (LF pin) controls the VCO frequency.

#### **Pin Description**

| Pin    | Symbol              | Function                                    |

|--------|---------------------|---------------------------------------------|

| 2      | F <sub>Ref in</sub> | External 12.8 MHz reference frequency input |

| 3      | VDD                 | Supply voltage                              |

| 4      | DGND                | Digital ground                              |

| 5      | QB <sub>in</sub>    | Analog switches input                       |

| 6      | Qin                 | Analog switches input                       |

| 7      | IB <sub>in</sub>    | Analog switches input                       |

| 8      | I <sub>in</sub>     | Analog switches input                       |

| 9      | MOD <sub>out</sub>  | Modulator output signal                     |

| 10     | TST                 | Test input, must be connected to            |

|        |                     | GND (only factory use)                      |

| 11     | LF                  | PLL loop filter                             |

| 12     | PROG                | PROG = 0, 1.6 MHz mode                      |

|        |                     | PROG = 1, 0.8 MHz mode                      |

| 13     | AGND                | Analog ground                               |

| 14     | CLKout              | Digital CMOS clock output                   |

|        |                     | 18.432 MHz                                  |

| 1, 15, | DNC                 | Do not connect                              |

| 16     |                     |                                             |

#### **Absolute Maximum Ratings**

Stresses at or above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in this data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                | Symbol              | Value                   | Unit |

|---------------------------|---------------------|-------------------------|------|

| Supply voltage            | V <sub>DD</sub>     | 6                       | V    |

| Modulator input voltages  | I<br>IB<br>Q<br>QB  | -0.5 to V <sub>DD</sub> | V    |

| Reference frequency input | F <sub>Ref in</sub> | -0.5 to V <sub>DD</sub> | V    |

| Ambient temperature       | T <sub>amb</sub>    | -40 to +85              | °C   |

| Storage temperature       | T <sub>stg</sub>    | -65 to +150             | °C   |

| Junction temperature      | Tj                  | $T_j < T_{amb} + 10$    | °C   |

#### **Operating Range**

| Parameters           | Symbol           | Value               | Unit |

|----------------------|------------------|---------------------|------|

| Supply voltage       | V <sub>DD</sub>  | $3 \pm 10\%$        | V    |

| Ambient temperature  | T <sub>amb</sub> | -5 to +70           | °C   |

| Junction temperature | Тj               | $T_j < T_{amb} + 5$ | °C   |

| Storage temperature  | T <sub>stg</sub> | -40 to +125         | °C   |

#### **Electrical Characteristics**

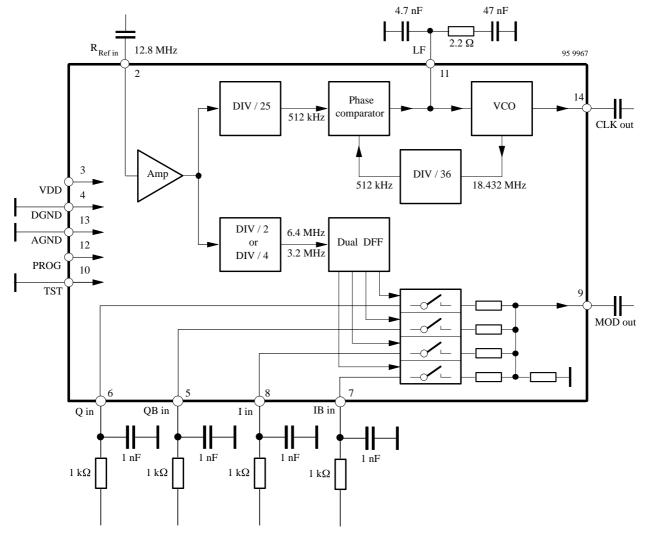

Test conditions (unless otherwise specified) related to test circuit

$V_S = 3 V$ ,  $V_{BIi}$ ,  $V_{BIi}$  and  $V_{BQi}$ ,  $V_{BQi} = 1 V_{PP}$  single ended, oscillator frequency  $F_{Ref in} = 12.8 \text{ MHz}$ ,  $T_{amb} = -5 \text{ to } +70^{\circ}\text{C}$

| Parameters                   | Test Conditions / Pins | Symbol                | Min. | Тур.   | Max. | Unit             |

|------------------------------|------------------------|-----------------------|------|--------|------|------------------|

| Supply voltage range         | Pin 3                  | V <sub>DD</sub>       | 2.7  | 3      | 3.3  | V                |

| Supply current <sup>1)</sup> | Pin 3                  | I <sub>DD</sub>       |      | 2      |      | mA               |

| F <sub>Ref in</sub>          | Pin 2                  |                       |      |        |      |                  |

| Input voltage                |                        | V <sub>F Ref in</sub> | 150  |        |      | mV <sub>PP</sub> |

| Input impedance              |                        | Z <sub>F Ref in</sub> | 100  |        |      | kΩ               |

| I, Q inputs                  | Pins 5, 6, 7 and 8     |                       |      |        |      |                  |

| Input voltage                | Single ended           | V <sub>Iin, Qin</sub> |      | 1      |      | V <sub>PP</sub>  |

| Input impedance              | Single ended           | Z <sub>Iin, Qin</sub> |      | 20     |      | kΩ               |

| Input frequency              |                        | F <sub>Iin, Qin</sub> |      | 18     |      | kHz              |

| External bias voltage        |                        | V <sub>IB, QB</sub>   |      | 1.5    |      | V                |

| MOD <sub>out</sub>           |                        |                       |      |        |      |                  |

| Output level <sup>2)</sup>   | Unloaded               | V <sub>Mod out</sub>  |      | 70     |      | mVRMS            |

| LO and sideband suppres-     |                        | LO sub                |      | -30    |      | dBc              |

| sion                         |                        | SB sub                |      |        |      |                  |

| Output impedance             |                        | Z <sub>Mod out</sub>  |      | 5      |      | kΩ               |

| CLK <sub>out</sub> Pin 14    |                        |                       |      |        |      |                  |

| Output frequency             |                        | F <sub>CLK out</sub>  |      | 18.432 |      | MHz              |

| Output level                 |                        | V <sub>CLK out</sub>  |      | CMOS   |      |                  |

| Output load                  |                        | Z <sub>CLK out</sub>  |      |        | 50   | pF               |

Note 1)  $C_L = 50 \text{ pF on Pin } 14$

Note 2) The output signal contains some harmonics, to be filtered by an external low-pass filter

# U3770M

TEMIC MATRA MHS

### **Test Circuit**

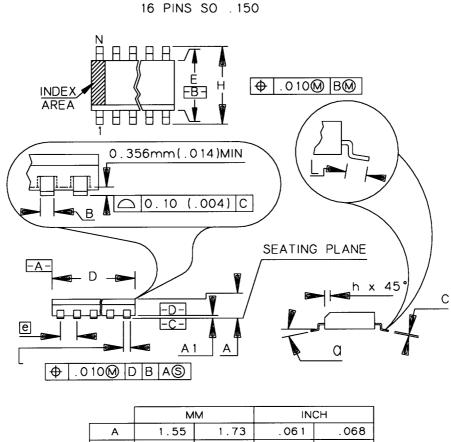

#### **Dimensions in mm**

Package: SO 16

|     | MM    |      |        |        |  |

|-----|-------|------|--------|--------|--|

| A   | 1.55  | 1.73 | . 06 1 | .068   |  |

| A 1 | 0.127 | 0.25 | . 004  | .0098  |  |

| В   | 0.35  | 0.49 | .014   | .019   |  |

| С   | 0.19  | 0.25 | .0075  | . 0098 |  |

| D   | 9.80  | 9.98 | . 386  | . 393  |  |

| E   | 3.81  | 3.99 | . 150  | . 157  |  |

| е   | 1.27  | BSC  | . 050  | BSC    |  |

| н   | 5.84  | 6.20 | . 230  | . 244  |  |

| h   | 0.25  | 0.41 | .010   | . 0 16 |  |

| L   | 0.41  | 0.89 | . 0 16 | .035   |  |

| N   | 16    |      | 16     |        |  |

| ٥   | 0°    |      | 8°     |        |  |

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423

Rev. A2: 15.01.1996