# TMS320F2803x Piccolo Local Interconnect Network (LIN) Module

# **User's Guide**

Literature Number: SPRUGE2B May 2009–Revised March 2014

### **Contents**

| Prefa | ice       |                                                     | 6         |

|-------|-----------|-----------------------------------------------------|-----------|

| 1     | Introduc  | ction and Features                                  | 8         |

|       | 1.1       | Purpose                                             | . 8       |

|       | 1.2       | Features                                            | . 8       |

|       | 1.3       | Block Diagram                                       | . 9       |

|       | 1.4       | Standards                                           | 10        |

| 2     | Operation | on                                                  | 11        |

|       | 2.1       | Message Frame                                       | 11        |

|       | 2.2       | Synchronizer                                        | 12        |

|       | 2.3       | Baud Rate                                           | 12        |

|       | 2.4       | Header Generation                                   |           |

|       | 2.5       | Extended Frames Handling                            | 17        |

|       | 2.6       | Timeout Control                                     | 18        |

|       | 2.7       | TXRX Error Detector (TED)                           | 19        |

|       | 2.8       | Message Filtering and Validation                    | 21        |

|       | 2.9       | Receive Buffers                                     | 23        |

|       | 2.10      | Transmit Buffers                                    | 24        |

| 3     | Interrup  | ts                                                  | 25        |

| 4     | Low-Po    | wer Mode                                            | 27        |

|       | 4.1       | Entering Sleep Mode                                 | 28        |

|       | 4.2       | Wakeup                                              | 28        |

|       | 4.3       | Wakeup Timeouts                                     | 29        |

| 5     | Emulati   | on Mode                                             | <b>29</b> |

| 6     | SCI/BLI   | N Control Registers                                 | 30        |

|       | 6.1       | SCI Global Control Register 0 (SCIGCR0)             | 37        |

|       | 6.2       | SCI Global Control Register (SCIGCR1)               | 37        |

|       | 6.3       | SCI Global Control Register (SCIGCR2)               | 42        |

|       | 6.4       | SCI Set Interrupt Register (SCISETINT)              | 43        |

|       | 6.5       | SCI Clear Interrupt Register (SCICLEARINT)          | 47        |

|       | 6.6       | SCI Set Interrupt Level Register (SCISETINTLVL)     | 51        |

|       | 6.7       | SCI Clear Interrupt Level Register (SCICLEARINTLVL) | 54        |

|       | 6.8       | SCI Flags Register (SCIFLR)                         |           |

|       | 6.9       | SCI Interrupt Vector Offset 0 (SCIINTVECT0)         | 64        |

|       | 6.10      | SCI Interrupt Vector Offset 1 (SCIINTVECT1)         |           |

|       | 6.11      | SCI Format Control Register (SCIFORMAT)             |           |

|       | 6.12      | Baud Rate Selection Register (BRSR)                 | 66        |

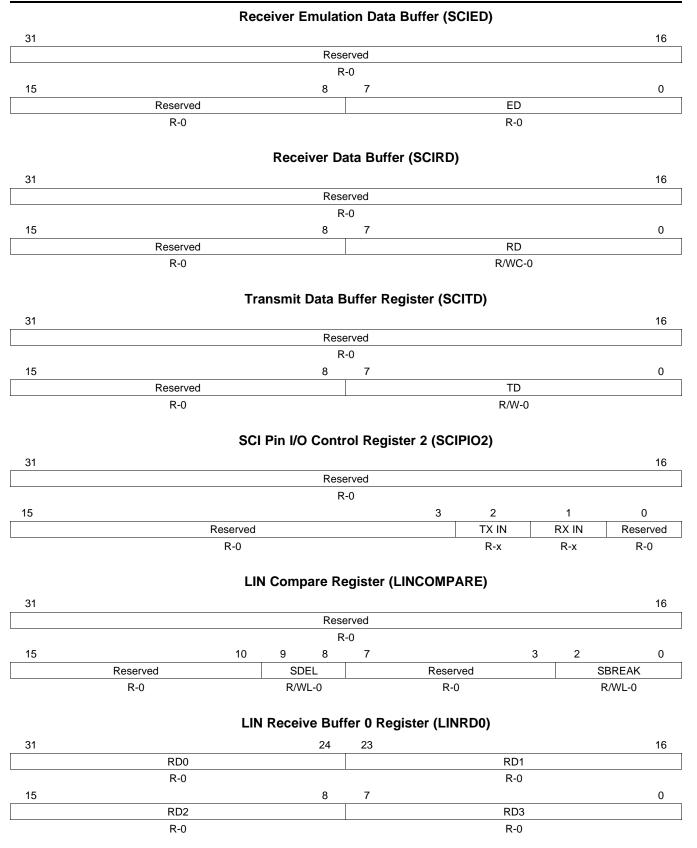

|       | 6.13      | SCI Data Buffers (SCIED, SCIRD, SCITD)              | 67        |

|       | 6.14      | SCI Pin I/O Control Register 2 (SCIPIO2)            | 69        |

|       | 6.15      |                                                     | 70        |

|       | 6.16      |                                                     | 70        |

|       | 6.17      | LIN Receive Buffer 1 Register (LINRD1)              | 71        |

| www.ti | i.com    |                                                  |    |

|--------|----------|--------------------------------------------------|----|

|        | 6.18     | LIN Mask Register (LINMASK)                      | 72 |

|        | 6.19     | LIN Identification Register (LINID)              | 72 |

|        | 6.20     | LIN Transmit Buffer 0 Register (LINTD0)          | 73 |

|        | 6.21     | LIN Transmit Buffer 1 Register (LINTD1)          | 73 |

|        | 6.22     | Maximum Baud Rate Selection Register (MBRS)      | 74 |

|        | 6.23     | I/O Design For Test Control (IODFTCTRL) Register | 75 |

| 7      | BLIN SC  | CI vs. Standard SCI                              | 77 |

| Appe   | ndix A F | Revision History                                 | 80 |

### List of Figures

| 1  | SCI/BLIN Block Diagram                                              | 10 |

|----|---------------------------------------------------------------------|----|

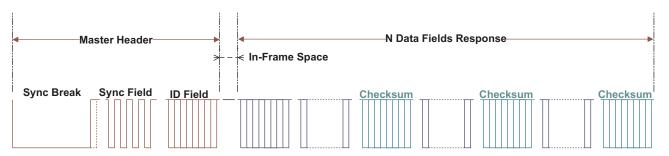

| 2  | LIN Protocol Message Frame Format: Master Header and Slave Response | 11 |

| 3  | Header Fields: Synch Break, Synch, and ID                           | 11 |

| 4  | Response Format of LIN Message Frame                                | 12 |

| 5  | Message Header in Terms of T <sub>bit</sub>                         | 14 |

| 6  | ID Field                                                            |    |

| 7  | Measurements for Synchronization                                    | 15 |

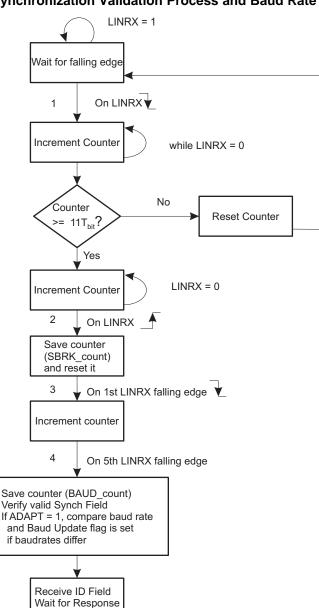

| 8  | Synchronization Validation Process and Baud Rate Adjustment         | 16 |

| 9  | Optional Embedded Checksum in Response for Extended Frames          |    |

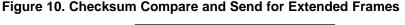

| 10 | Checksum Compare and Send for Extended Frames                       |    |

| 11 | TXRX Error Detector                                                 | 20 |

| 12 | Classic Checkbyte Generation at Transmitting Node                   | 21 |

| 13 | LIN 2.0-Compliant Checkbyte Generation at Transmitting Node         | 21 |

| 14 | ID Reception, Filtering and Validation                              |    |

| 15 | Receive Buffers                                                     | 24 |

| 16 | Transmit Buffers                                                    | 25 |

| 17 | General Interrupt Scheme                                            | 26 |

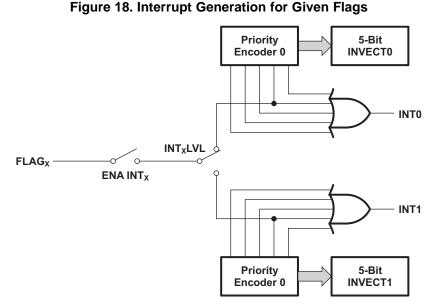

| 18 | Interrupt Generation for Given Flags                                |    |

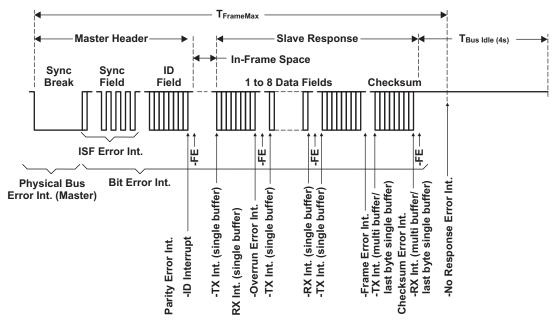

| 19 | LIN Message Frame Showing LIN Interrupt Timing and Sequence"        | 27 |

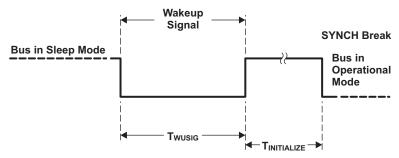

| 20 | Wakeup Signal Generation                                            | 29 |

| 21 | SCI Global Control Register 0 (SCIGCR0)                             | 37 |

| 22 | SCI Global Control Register (SCIGCR1)                               | 37 |

| 23 | SCI Global Control Register (SCIGCR2)                               | 42 |

| 24 | SCI Set Interrupt Register (SCISETINT)                              |    |

| 25 | SCI Clear Interrupt Register (SCICLEARINT)                          | 48 |

| 26 | SCI Set Interrupt Level Register (SCISETINTLVL)                     | 51 |

| 27 | SCI Clear Interrupt Level Register (SCICLEARINTLVL)                 | 55 |

| 28 | SCI Flags Register (SCIFLR)                                         | 58 |

| 29 | SCI Interrupt Vector Offset 0 (SCIINTVECT0)                         | 65 |

| 30 | SCI Interrupt Vector Offset 1 (SCIINTVECT1)                         | 65 |

| 31 | SCI Format Control Register (SCIFORMAT)                             | 66 |

| 32 | Baud Rate Selection Register (BRSR)                                 | 67 |

| 33 | Receiver Emulation Data Buffer (SCIED)                              | 68 |

| 34 | Receiver Data Buffer (SCIRD)                                        | 68 |

| 35 | Transmit Data Buffer Register (SCITD)                               | 69 |

| 36 | SCI Pin I/O Control Register 2 (SCIPIO2)                            | 69 |

| 37 | LIN Compare Register (LINCOMPARE)                                   | 70 |

| 38 | LIN Receive Buffer 0 Register (LINRD0)                              | 71 |

| 39 | LIN Receive Buffer 1 Register (LINRD1)                              | 71 |

| 40 | LIN Mask Register (LINMASK)                                         | 72 |

| 41 | LIN Identification Register (LINID)                                 | 72 |

| 42 | LIN Transmit Buffer 0 Register (LINTD0)                             | 73 |

| 43 | LIN Transmit Buffer 1 Register (LINTD1)                             | 74 |

| 44 | Maximum Baud Rate Selection Register (MBRS)                         | 74 |

| 45 | I/O Design For Test Control (IODFTCTRL) Register                    | 75 |

### List of Tables

| 1  | Response Length with SCIFORMAT(18–16) Programming                      | 12              |

|----|------------------------------------------------------------------------|-----------------|

| 2  | Timeout Values in T <sub>bit</sub> Units                               | 18              |

| 3  | SCI/BLIN Interrupts                                                    | 26              |

| 4  | LIN Registers                                                          | 30              |

| 5  | SCI Global Control Register 0 (SCIGCR0) Field Descriptions             | 37              |

| 6  | SCI Global Control Register (SCIGCR1) Field Descriptions               | 37              |

| 7  | SCI Receiver Status Flags                                              | 42              |

| 8  | SCI Transmitter Status Flags                                           | 42              |

| 9  | SCI Global Control Register (SCIGCR2) Field Descriptions               | 42              |

| 10 | SCI Set Interrupt Register (SCISETINT) Field Descriptions              | 44              |

| 11 | SCI Clear Interrupt Register (SCICLEARINT) Field Descriptions          | 48              |

| 12 | SCI Set Interrupt Level Register (SCISETINTLVL) Field Descriptions     | 52              |

| 13 | SCI Clear Interrupt Level Register (SCICLEARINTLVL) Field Descriptions | 55              |

| 14 | SCI Flags Register (SCIFLR) Field Descriptions                         | 58              |

| 15 | SCI Interrupt Vector Offset 0 (SCIINTVECT0) Field Descriptions         | <b>65</b>       |

| 16 | SCI Interrupt Vector Offset 1 (SCIINTVECT1) Field Descriptions         | 65              |

| 17 | SCI Format Control Register (SCIFORMAT) Field Descriptions             | 66              |

| 18 | Baud Rate Selection Register (BRSR) Field Descriptions                 | 67              |

| 19 | P and M values for standard bit-rates                                  | 67              |

| 20 | Receiver Emulation Data Buffer (SCIED) Field Descriptions              | <b>68</b>       |

| 21 | Receiver Data Buffer (SCIRD) Field Descriptions                        | <mark>68</mark> |

| 22 | Transmit Data Buffer Register (SCITD) Field Descriptions               | 69              |

| 23 | SCI Pin I/O Control Register 2 (SCIPIO2) Field Descriptions            | 69              |

| 24 | LIN Compare Register (LINCOMPARE) Field Descriptions                   | 70              |

| 25 | LIN Receive Buffer 0 Register (LINRD0) Field Descriptions              | 71              |

| 26 | LIN Receive Buffer 1 Register (LINRD1) Field Descriptions              | 71              |

| 27 | LIN Mask Register (LINMASK) Field Descriptions                         | 72              |

| 28 | LIN Identification Register (LINID) Field Descriptions                 | 72              |

| 29 | LIN Transmit Buffer 0 Register (LINTD0) Field Descriptions             | 73              |

| 30 | LIN Transmit Buffer 1 Register (LINTD1) Field Descriptions             | 74              |

| 31 | Maximum Baud Rate Selection Register (MBRS) Field Descriptions         | 74              |

| 32 | I/O Design For Test Control (IODFTCTRL) Register Field Descriptions    | 75              |

| 33 | SCI vs. LIN-SCI Programming                                            | 77              |

This document describes the Local Interconnect Network (LIN) Module.

#### **About This Manual**

The TMS320C2000<sup>™</sup> is part of the TMS320<sup>™</sup> family.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h or with a leading 0x. For example, the following number is 40 hexadecimal (decimal 64): 40h or 0x40.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation**

The following books describe the TMS320x28x and related support tools that are available on the TI website:

SPRS584 — TMS320F28032, TMS320F28033, TMS320F28034, TMS320F28035 Piccolo Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications for the 2803x devices.

<u>SPRZ295</u> — TMS320F28032, TMS320F28033, TMS320F28034, TMS320F28035 Piccolo MCU Silicon Errata describes known advisories on silicon and provides workarounds.

#### CPU User's Guides-

SPRU430 — TMS320C28x CPU and Instruction Set Reference Guide describes the central processing unit (CPU) and the assembly language instructions of the TMS320C28x fixed-point digital signal processors (DSPs). It also describes emulation features available on these DSPs.

#### Peripheral Guides—

- <u>SPRUGL8</u> TMS320x2803x Piccolo System Control and Interrupts Reference Guide describes the various interrupts and system control features of the 2803x microcontrollers (MCUs).

- <u>SPRU566</u> TMS320x28xx, 28xxx DSP Peripheral Reference Guide describes the peripheral reference guides of the 28x digital signal processors (DSPs).

- <u>SPRUGO0</u> TMS320x2803x Piccolo Boot ROM Reference Guide describes the purpose and features of the boot loader (factory-programmed boot-loading software) and provides examples of code. It also describes other contents of the device on-chip boot ROM and identifies where all of the information is located within that memory.

- <u>SPRUGE6</u> TMS320x2803x Piccolo Control Law Accelerator (CLA) Reference Guide describes the operation of the Control Law Accelerator (CLA).

- <u>SPRUGE2</u> TMS320x2803x Piccolo Local Interconnect Network (LIN) Module Reference Guide describes the operation of the Local Interconnect Network (LIN) Module.

- <u>SPRUFK8</u> TMS320x2803x Piccolo Enhanced Quadrature Encoder Pulse (eQEP) Reference Guide describes the operation of the Enhanced Quadrature Encoder Pulse (eQEP).

- <u>SPRUGL7</u> TMS320x2803x Piccolo Enhanced Controller Area Network (eCAN) Reference Guide describes the operation of the Enhanced Controller Area Network (eCAN).

- <u>SPRUGE5</u> TMS320x2802x, 2803x Piccolo Analog-to-Digital Converter (ADC) and Comparator Reference Guide describes how to configure and use the on-chip ADC module, which is a 12-bit pipelined ADC.

- SPRUGE9 TMS320x2802x, 2803x Piccolo Enhanced Pulse Width Modulator (ePWM) Module Reference Guide describes the main areas of the enhanced pulse width modulator that include digital motor control, switch mode power supply control, UPS (uninterruptible power supplies), and other forms of power conversion.

- <u>SPRUGE8</u> TMS320x2802x, 2803x Piccolo High-Resolution Pulse Width Modulator (HRPWM) describes the operation of the high-resolution extension to the pulse width modulator (HRPWM).

- <u>SPRUGH1</u> TMS320x2802x, 2803x Piccolo Serial Communications Interface (SCI) Reference Guide describes how to use the SCI.

- <u>SPRUFZ8</u> TMS320x2802x, 2803x Piccolo Enhanced Capture (eCAP) Module Reference Guide describes the enhanced capture module. It includes the module description and registers.

- <u>SPRUG71</u> TMS320x2802x, 2803x Piccolo Serial Peripheral Interface (SPI) Reference Guide describes the SPI - a high-speed synchronous serial input/output (I/O) port - that allows a serial bit stream of programmed length (one to sixteen bits) to be shifted into and out of the device at a programmed bit-transfer rate.

- <u>SPRUFZ9</u> TMS320x2802x, 2803x Piccolo Inter-Integrated Circuit (I2C) Reference Guide describes the features and operation of the inter-integrated circuit (I2C) module.

#### Tools Guides—

- <u>SPRU513</u> TMS320C28x Assembly Language Tools v5.0.0 User's Guide describes the assembly language tools (assembler and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the TMS320C28x device.

- SPRU514 TMS320C28x Optimizing C/C++ Compiler v5.0.0 User's Guide describes the TMS320C28x<sup>™</sup> C/C++ compiler. This compiler accepts ANSI standard C/C++ source code and produces TMS320 DSP assembly language source code for the TMS320C28x device.

- SPRU608 TMS320C28x Instruction Set Simulator Technical Overview describes the simulator, available within the Code Composer Studio for TMS320C2000 IDE, that simulates the instruction set of the C28x<sup>™</sup> core.

### Local Interconnect Network (LIN) Module

This document describes the buffered local interconnect network (BLIN) module. Since this module can also operate like a conventional serial communications interface (SCI) port, it is referred to as the SCI/BLIN module in this document. In the SCI (UART) mode, it is functionally compatible to the standalone SCI module in the TMS320x2803x device. However, since the SCI/BLIN module uses a different register/bit structure, code written for this module cannot be directly ported to the standalone SCI module and vice versa.

#### 1 Introduction and Features

The SCI/BLIN is compliant to the LIN 2.0 protocol specified in the LIN Specification Package. This module uses the SCI as its core and augments the SCI's hardware features for LIN compatibility. This module can be configured to operate in either LIN mode or the SCI (UART) mode. The SCI mode is also referred to as *compatibility mode* in this document.

#### 1.1 Purpose

The SCI/BLIN provides a communications structure at the hardware and software level. It provides a low-cost solution where the bandwidth and fault tolerance of a controller area network (CAN) are not required.

#### 1.2 Features

The following are the features of the SCI/BLIN module:

- Compatibility with LIN 1.3 or 2.0 protocols (LIN Specification Package 2002)

- Two external pins: LINRX and LINTX

- Functionally compatible with the standalone SCI of C2000 devices

- Multi-buffered receive and transmit units

- Identification masks for message filtering

- Automatic master header generation

- Programmable synchronization break field

- Synchronization field

- Identifier field

- Slave automatic synchronization

- Synchronization break detection

- Optional baud rate update

- Synchronization validation

- 2<sup>28</sup> programmable transmission rates

- Wakeup on LINRX dominant level from transceiver

- Automatic wakeup support

- Wakeup signal generation

- Expiration times on wakeup signals

- Automatic bus idle detection

- Error detection

- Bit error

TEXAS INSTRUMENTS

#### www.ti.com

- Bus error

- No-response error

- Checksum error

- Synchronization field error

- Parity error

- 2 Interrupt lines with priority encoding for:

- Receive

- Transmit

- ID, error, and status

- Support for LIN 2.0 checksum

- Enhanced synchronizer finite state machine (FSM) support for frame processing

- Enhanced handling of extended frames

- Enhanced baud rate generator

#### 1.3 Block Diagram

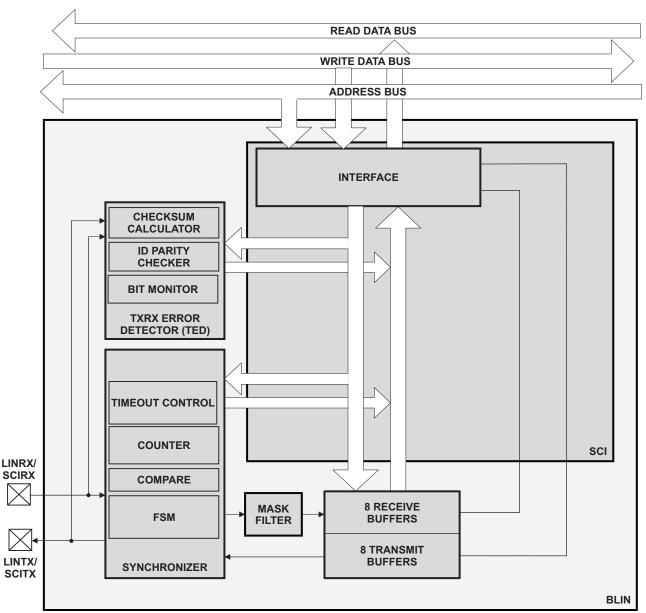

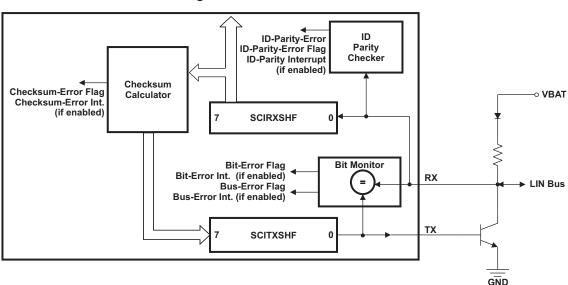

The SCI/BLIN module is based on the SCI with the addition of an error detector (parity calculator, checksum calculator, and bit monitor), a mask filter, a synchronizer, and a multibuffered receiver and transmitter. The SCI interface and the baud generator are modified as part of the hardware enhancements for LIN compatibility. Figure 1 shows the SCI/BLIN block diagram.

#### Figure 1. SCI/BLIN Block Diagram

#### 1.4 Standards

The LIN standard is based on the SCI (UART) serial data link format. The communication concept is single-master/multiple-slave with a message identification for multi-cast transmission between any network nodes.

For compatibility with LIN2.0 standard, the following additional features are implemented over LIN1.3:

- (i) Support for LIN 2.0 checksum

- (ii) Enhanced synchronizer FSM support for frame processing

- (iii) Enhanced handling of extended frames

- (iv) Enhanced baudrate generator

- (v) Update wakeup/go to sleep

The SCI/BLIN module covers the CPU performance-consuming features, defined in the *LIN Specification Package* Revision 1.3 and 2.0 by hardware.

#### 2 Operation

The SCI/BLIN module can be used in LIN mode or SCI (UART) mode. The enhancements for baud generation and additional receive/transmit buffers necessary for LIN mode operation are part of the enhanced buffered SCI/BLIN module.

**NOTE:** To make a determination of the bit value, 16 samples for each bit are taken with majority vote on samples 8, 9, and 10.

For a detailed description of SCI/BLIN registers, see Section 6.

#### 2.1 Message Frame

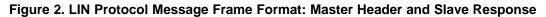

The LIN protocol defines a message frame format, illustrated in Figure 2. Each frame includes one master header, one response, one in-frame response space, and inter-byte spaces. In-frame-response and interbyte spaces may be 0.

There is no arbitration in the definition of the LIN protocol; therefore, multiple slave nodes responding to a header might be detected as an error.

The LIN bus is a single channel wired-AND. The bus has a binary level: either dominant for a value of 0, or recessive for a value of 1.

#### 2.1.1 Message Header

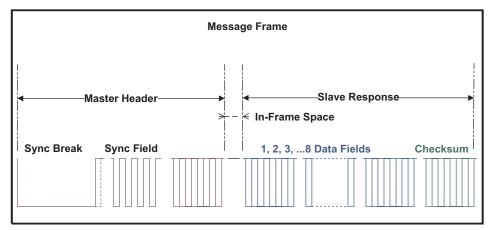

The header of a message is initiated by a master (see Figure 3) and consists of a three field-sequence:

- The synch break field signaling the beginning of a message

- The synch field conveying bit rate information of the LIN bus

- The ID field denoting the content of a message

#### Figure 3. Header Fields: Synch Break, Synch, and ID

Operation

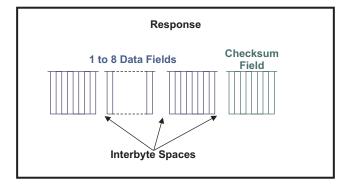

#### 2.1.2 Response

The format of the response is as illustrated in Figure 4. There are two types of fields in a response: data and checksum. The data field consists of exactly one data byte, one start bit, and one stop bit, for a total of 10 bits. The LSB is transmitted first. The checksum field consists of one checksum byte, one start bit and one stop bit. The checksum byte is the inverted modulo-256 sum over all data bytes in the data fields of the response.

Figure 4. Response Format of LIN Message Frame

The format of the response is a stream of "N" data fields and one checksum field. Typically N is from 1 to 8, with the exception of the extended command frames. The length N of the response is indicated with the optional length control bits of the identifier, or by the SCIFORMAT(18–16) register (Section 6.11); see Table 1. The SCI/BLIN module supports response lengths from 1 to 8 bytes in compliance with LIN 2.0.

| SCIFORMAT (18–16) | No. of Bytes |

|-------------------|--------------|

| 000               | 1            |

| 001               | 2            |

| 010               | 3            |

| 011               | 4            |

| 100               | 5            |

| 101               | 6            |

| 110               | 7            |

| 111               | 8            |

Table 1. Response Length with SCIFORMAT(18–16) Programming

#### 2.2 Synchronizer

The synchronizer has three major functions in the messaging between master and slave nodes. It generates the master header data stream, it synchronizes to the LIN bus for responding, and it locally detects timeouts. A bit rate is programmed using the prescalers in the BRS register as indicated by the LIN\_speed value in the LIN description file (LDF).

The SCI/BLIN synchronizer will perform the following functions: master header signal generation, slave detection and synchronization to message header with optional baud rate adjusting, response transmission timing and timeout control.

The SCI/BLIN synchronizer should be capable of detecting an incoming break and initialize communication at all times.

#### 2.3 Baud Rate

The LIN module is clocked at a frequency of one-half the CPU clock (SYSCLKOUT). i.e. LIN Module input clock (LM\_CLK) = SYSCLKOUT/2. For a 60 MHz device, LM\_CLK = 30 MHz.

The transmission baud rate of any node is configured by the CPU in the beginning; this defines the bit time  $T_{bit}$ . The bit time is derived from the fields P and M in the baud rate selection register (BRSR; Section 6.12).

The ranges for the prescaler values in the BRSR are:

$P = 0, 1, 2, 3, \ldots, 2^{24} - 1$

M = 0, 1, 2, . . . , 15

The BRSR with P and M values are user programmable. These divider values are automatically obtained in LIN mode (during header reception) when the synchronization field is measured, if the ADAPT bit is set. Otherwise, the P and M dividers could be used for both SCI mode and LIN mode to select a baud rate.

The LIN protocol defines baud rate boundaries as follows:

$1 \text{kHz} \leq \text{F}_{\text{LINCLK}} \leq 20 \text{kHZ}$

All transmitted bits are shifted in and out at T<sub>bit</sub> periods.

#### 2.3.1 Fractional Divider

The M field of the BRSR register (Section 6.12) modifies the integer prescaler P for finer tuning of the baud rate. The M value adds in increments of 1/16 of the P value.

Therefore, the LINCLK frequency is given by

For all P other than 0, and all M,

$$T_{bit} = 16 \left[P + 1 + \frac{M}{16}\right] T_{LM_{-}CLK}$$

For

$$P = 0$$

:  $T_{bit} = 32T_{LM CLK}$

Therefore, the LINCLK frequency is given by:

$$F_{\text{LINCLK}} = \frac{LM - CLK}{16\left[P + 1 + \frac{M}{16}\right]}, \text{ for all P other than zero}$$

$$F_{\text{LINCLK}} = \frac{LM - CLK}{32}, \text{ for P} = 0$$

**NOTE:** LM\_CLK = 30 MHz,  $T_{LM CLK}$  = 33.3 ns for a 60 MHz device.

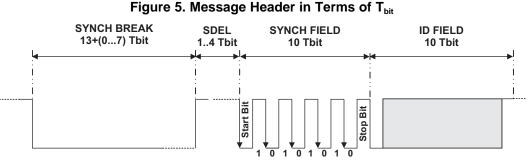

#### 2.4 Header Generation

Automatic generation of the LIN protocol header data stream is supported without CPU interaction. The CPU will trigger a message header generation and the SCI/BLIN state machine will handle the generation itself. The header is always sent by the master to initiate a LIN communication and consists of three fields: synchronization break field, synchronization field, and identification field, as seen in Figure 5.

- The synchronization break field consists of two components.

- The synchronization break (SYNCH BREAK) consists of a minimum of 13 (dominant) low bits to a maximum of 20 dominant bits. The synch break length may be extended from the minimum with the 3- bit SBREAK value in the LINCOMP register.

- The synchronization break delimiter (SDEL) consists of a minimum of 1 (recessive) high bit to a maximum of 4 recessive bits. The delimiter marks the end of the synchronization break field. The synch break delimiter length depends on the 2-bit SDEL value in the LINCOMP register.

- The synchronization field (SYNCH FIELD) consists of one start bit, byte 0x55, and a stop bit. It is used to convey T<sub>bit</sub> information and resynchronize LIN bus nodes.

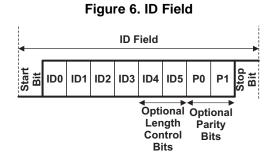

- The identifier field's ID byte may use six bits as an identifier (optional length control within it), and two

optional bits as parity of the identifier. The identifier parity is used and checked if the (SCIGCR1.2)

PARITY enable bit is set. If length control bits are not used, then there can be a total of 64 identifiers

plus parity. If neither length control or parity are used there can be up to 256 identifiers. See Figure 6

for an illustration of the ID field.

- **NOTE:** The LIN protocol uses the parity bits in the identifier. The control length bits are optional to the LIN protocol.

A master node initiates header generation on CPU writes to the IDBYTE in the LINID register (Section 6.19).

**NOTE:** IDBYTE [LINID(5–4); Section 6.19] conveys response length information if compliant to standards earlier than LIN 1.3.

| ID5 | ID4 | Number of Data bytes |

|-----|-----|----------------------|

| 0   | 0   | 2                    |

| 0   | 1   | 2                    |

| 1   | 0   | 4                    |

| 1   | 1   | 8                    |

The SCIFORMAT register (Section 6.11) stores the length of the response for later versions of the LIN protocol.

#### 2.4.1 Event Triggered Frame Handling

The LIN 2.0 protocol uses event-triggered frames that may occasionally cause collisions. Event-triggered frames have to be handled in software.

If no slave answers to an event triggered frame header, the master node will set the NRE flag and a NRE interrupt will occur if enabled. If a collision occurs, a frame error and checksum error may arise before the NRE error. Those errors are flagged and the appropriate interrupts will occur, if enabled.

Frame errors and checksum errors depend on the behavior and synchronization of the responding slaves. If the slaves are totally synchronized and stop transmission once the collision occurred, it is possible that only the NRE error is flagged despite the occurrence of a collision. To detect if there has been a reception of one byte before the NRE error is flagged use the bus busy flag (SCIFLR.3) as an indicator.

The bus busy flag is set on the reception of the first bit of the header and remains set until the header reception is complete, and again is set on the reception of the first bit of the response. In the case of a collision, the flag is cleared in the same cycle as the NRE flag is set.

Software could implement the following sequence:

- Once the reception of the header is done (poll for RXID flag), wait for the bus busy flag to get set or NRE flag to get set.

- If bus busy flag is not set before NRE flag, then it is a true no response case (no data has been transmitted onto the bus).

- If bus busy flag gets set, then wait for NRE flag to get set or for successful reception. If NRE flag is set, then in this case a collision has occurred on the bus.

Even in the case of a collision, the received (corrupted) data is accessible in the RX buffers; registers LINRD0 and LINRD1.

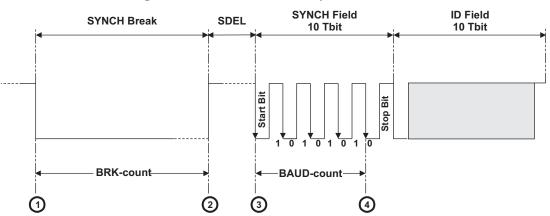

#### 2.4.2 Header Reception and Adaptive Baud Rate

A slave node baud rate might be adjusted to the detected bit rate as an option in the SCI/BLIN module. The adaptive baud rate option is enabled by setting the ADAPT bit in SCIGCR1 (Section 6.2). During header reception, a slave measures the baud rate during detection of the synch field. If SCIGCR1[10] (the ADAPT bit) is set, then the measured baud rate is compared to the slave node's programmed baud rate and adjusted to the LIN bus baud rate if necessary.

The SCI/BLIN synchronizer determines two measurements: BRK\_count and BAUD\_count (Figure 7). These values are always calculated during the Header reception for synch field validation (Figure 8).

#### NOTE: When an inconsistent synch field (ISF) error occurs, suggested action for the application is

- Reset the SWnRST bit.

- Set the SWnRST bit to make sure that the internal FSMs are back to their normal states

#### Figure 7. Measurements for Synchronization

#### Figure 8. Synchronization Validation Process and Baud Rate Adjustment

By measuring the values BRK\_count and BAUD\_count, a valid synch break sequence can be detected as described in Figure 8. The four numbered events in Figure 7 signal the start/stop of the synchronizer counter. The synchronizer counter uses LM\_CLK as the time base.

The synchronizer counter is used to measure the synch break relative to the detecting node  $T_{bit}$ . For a slave node receiving the synch break, a threshold of 11  $T_{bit}$  is used as required by the LIN protocol. For detection of the dominant data stream of the synch break, the synchronizer counter is started on a falling edge and stopped on a rising edge of the LINRX. On detection of the synch break delimiter, the synchronizer counter value is saved and then reset.

On detection of five consecutive falling edges, the BAUD\_count is measured. Bit timing calculation and consistency to required accuracy is implemented following the recommendations of LIN revision 2.0. A slave node can calculate a single  $T_{bit}$  time by division of BAUD\_count by 8. In addition, for consistency between the detected edges the following is evaluated:

$BAUD\_count + BAUD\_count \gg 2 + BAUD\_count \gg 3 \le BRK\_count$

The BAUD\_count value is shifted 3 times to the right and rounded using the first insignificant bit to obtain a  $T_{bit}$  unit. If the ADPAT bit is set then, the detected baud rate is compared to the programmed baud rate.

During the header reception processing as illustrated in Figure 8, if the measured BRK\_count value is less than 11  $T_{bit}$  the synch break is not valid according to the protocol for a fixed rate. If the ADAPT bit is set, then the MBRS (Section 6.22) is used for measuring BRK\_count and BAUD\_count values and automatically adjusts to any allowed LIN bus rate (refer to LIN Specification Package 2.0).

NOTE: The MBRS divider should be set so that the rate is 20 kHz.

**NOTE:** The synch-break-threshold relative to the slave node is 11 T<sub>bit</sub>. The synch break is 13 T<sub>bit</sub> as specified in LIN version 1.3.

If the synch field is not detected within the given tolerances, the inconsistent-synch-field-error (ISFE) flag will be set. An ISFE interrupt will be generated, if enabled by its respective bit in the SCISETINT register (Section 6.6). The ID byte should be received after the synch field validation was successful. Any time a valid synch break (larger than 11  $T_{bit}$ ) is detected, the receiver's state machine should reset to reception of this new frame. This reset condition is only valid during response state, it should not occur if an additional synch break occurs during header reception.

#### 2.5 Extended Frames Handling

The LIN protocol includes two extended frames with identifiers 62 (user defined) and 63 (reserved extended). The length for these identifiers will be set during network configuration and are to be shared with the LIN bus nodes.

**NOTE:** Only identifier 62 (0x3E) applies to this special extended frame handling of unlimited response length.

Extended frame communication is triggered on reception of a header with identifier 0x3E; see Figure 9. Once the extended frame communication is triggered, unlike normal frames, this communication needs to be stopped before issuing another header. To stop the current extended frame communication, the SCIGCR1.13 bit must be set.

#### Figure 9. Optional Embedded Checksum in Response for Extended Frames

Extended Frame With Embedded Checksum Bytes

For the LIN 2.0 specification, the length of the user-defined frame is unlimited. Therefore, an ID interrupt will be generated (if enabled and there is a match) on reception of this identifier. This interrupt allows the CPU using a software counter to keep track of the bytes that are being sent out and decides when to calculate and insert a checksum byte (recommended at periodic rates). To handle this procedure, bit SCIGCR2[16] (Section 6.3) is used. A write to the SCIGCR2[16] bit will initiate an automatic send of the checkbyte. The last data field should be a checksum in compliance with the LIN protocol.

The periodicity of the checksum insertion, defined during network configuration, is used by the receiving node to evaluate the checksum of the ongoing message and has the benefit of enhanced reliability.

For the sending node, the automatic embedding of checksum should be possible when the SCIGCR2[16] bit is set. For the receiving node, a checksum comparison should be forced when the SCIGCR2[17] bit is set; see Figure 10.

**NOTE:** The LIN 2.0 enhanced checksum does not apply to the reserved identifiers. They will always use the classic checksum.

#### 2.6 Timeout Control

Any SCI/BLIN node listening to the bus and expecting a response initiated from a master node could flag a no-response error timeout event. The LIN protocol defines four types of timeout events, which are all handled by the hardware of the SCI/BLIN module. The four LIN protocol events are:

- No-response timeout error

- Bus idle detection

- Timeout after wakeup signal

- Timeout after three wakeup signals

#### 2.6.1 No-Response Error

The no-response error will occur when any node expecting a response waits for T<sub>FRAME\_MAX</sub> time and the message frame is not fully completed within the maximum length allowed, T<sub>FRAME\_MAX</sub>. After this time a no-response error (NRE) is flagged in the NRE bit of the SCIFLR register. An interrupt is triggered if enabled.

As specified in the LIN 1.3 standard, the minimum time to transmit a frame is:

$T_{FRAME_MIN} = T_{HEADER_MIN} + T_{DATA_FIELD} + TC_{HECKSUM_FIELD} = 44 + 10N$

where N = number of data fields.

And the maximum time frame is given by:

$T_{\text{FRAME MAX}} = (T_{\text{FRAME MIN}} + 1) \times 1.4$

The timeout value  $T_{FRAME_MAX}$  is derived from the N number of data fields value. The N value is either embedded in the header's ID field for messages or is part of the description file. In the latter case, the 3-bit CHAR value, SCIFORMAT(18–16) in Section 6.11, will indicate the value for N.

| Ν |    | T <sub>FRAME_MIN</sub> | T <sub>FRAME_MAX</sub> |

|---|----|------------------------|------------------------|

| 1 | 10 | 54                     | 77                     |

| 2 | 20 | 64                     | 91                     |

| 3 | 30 | 74                     | 105                    |

#### Table 2. Timeout Values in T<sub>bit</sub> Units

| Table 2. Thireout Values in T <sub>bit</sub> Onits (Continued) |                                                       |                                                                                                                                        |                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| T <sub>DATA_FIELD</sub>                                        | T <sub>FRAME_MIN</sub>                                | T <sub>FRAME_MAX</sub>                                                                                                                 |                                                                                                                                                                                                               |  |  |

| 40                                                             | 84                                                    | 119                                                                                                                                    |                                                                                                                                                                                                               |  |  |

| 50                                                             | 94                                                    | 133                                                                                                                                    |                                                                                                                                                                                                               |  |  |

| 60                                                             | 104                                                   | 147                                                                                                                                    |                                                                                                                                                                                                               |  |  |

| 70                                                             | 114                                                   | 161                                                                                                                                    |                                                                                                                                                                                                               |  |  |

| 80                                                             | 124                                                   | 175                                                                                                                                    |                                                                                                                                                                                                               |  |  |

|                                                                | <b>T<sub>DATA_FIELD</sub></b><br>40<br>50<br>60<br>70 | T <sub>DATA_FIELD</sub> T <sub>FRAME_MIN</sub> 40         84           50         94           60         104           70         114 | T <sub>DATA_FIELD</sub> T <sub>FRAME_MIN</sub> T <sub>FRAME_MAX</sub> 40         84         119           50         94         133           60         104         147           70         114         161 |  |  |

Table 2. Timeout Values in T<sub>bit</sub> Units (continued)

**NOTE:** The length coding of the ID field does not apply to two extended frame identifiers, with ID fields 0x3E (62) and 0x3F (63). In these cases, the ID field can be followed by an arbitrary number of data byte fields. The LIN 2.0 protocol specification mentions that ID field 0x3F (63) cannot be used. For these two cases, the NRE will not be handled by the SCI/BLIN controller hardware.

#### 2.6.2 Bus Idle Detection

The second type of timeout can occur when a node detects an inactive LIN bus: no transitions between recessive and dominant values are detected on the bus. This should happen after a minimum of 4 s (this is 80,000  $F_{LINCLK}$  cycles with the fastest bus rate of 20 kbps). If a node detects no activity in the bus as the TIMEOUT bit is set (Section 6.8), then it can be assumed that the LIN bus is in sleep mode.

#### 2.6.3 Timeout after Wakeup Signal and Timeout after Three Wakeup Signals

The third and fourth types of timeout are related to the wakeup signal. A node initiating a wakeup should expect a header from the master within a defined amount of time: timeout after wakeup signal. See Section 4.3 for more details.

#### 2.7 TXRX Error Detector (TED)

The following sources of error are detected by the TXRX error detector logic (TED). The TED logic consists of a bit monitor, an ID parity checker, and a checksum error. The following errors are detected:

- Bit errors (BE)

- Physical bus errors (PBE)

- Identifier parity errors (PE)

- Checksum errors (CE)

All of these errors (BE, PBE, PE, CE) are flagged. An interrupt for the flagged errors will be generated if enabled. A message is valid for both the transmitter and the receiver if there is no error detected until the end of the frame.

#### 2.7.1 Bit Errors

A BE has to be detected at that bit time when the bit value that is monitored is different from the bit value that is sent. A BE is indicated by the BE flag in SCIFLR (Section 6.8). After signaling a BE, the transmission has to be aborted no later than the next byte. The bit monitor ensures that the transmitted bit in LINTX is the correct value on the LIN bus by reading back on the LINRX pin as shown in Figure 11.

Operation

#### Figure 11. TXRX Error Detector

#### 2.7.2 Physical Bus Errors

A PBE must be detected by a master if no valid message can be generated on the bus (i.e., the bus is shorted to GND or  $V_{BAT}$ ). The bit monitor can detect a physical bus error during header generation as it compares the actual value on the bus with the expected value at each bit time.

#### 2.7.3 ID Parity Errors

If parity is enabled, an ID parity error has to be detected, if any of the two parity bits of the sent ID byte are not equal to the calculated parity on the receiver node. The two parity bits are generated using the following mixed parity algorithm.

$P0 = ID0 \oplus ID1 \oplus ID2 \oplus ID4$  (even parity)

$P1 = ID1 \oplus ID3 \oplus ID4 \oplus ID5 \text{(odd parity)}$

An ID-parity error is flagged if detected and the received ID is not valid. See Section 2.7.4 for details.

#### 2.7.4 Checksum Errors

A CE must be detected and flagged at the receiving end if the calculated modulo-256 sum over all received data bytes (including the ID byte if it is the enhanced checksum type) plus the checkbyte does not result in 0xFF. The modulo-256 sum is calculated over each byte by adding with carry, where the carry bit of each addition is added to the LSB of its resulting sum.

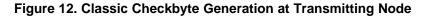

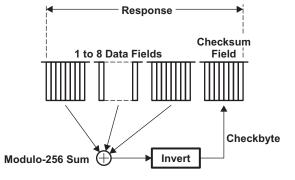

For the transmitting node, the checkbyte sent at the end of a message is the inverted sum of all the data bytes (see Figure 12) for classic implementation. The checkbyte is the inverted sum of the identifier byte and all the data bytes (see Figure 13) for the LIN 2.0 compliant implementation. The classic implementation should always be used for reserved identifiers 60 to 63; therefore, the CTYPE bit (SCIGCR1[12]; Section 6.2) will be overridden in this case. For signal-carrying-frame identifiers (0 to 59) the type of checksum used depends on the CTYPE bit (SCICGR1.12)

#### Figure 13. LIN 2.0-Compliant Checkbyte Generation at Transmitting Node

#### 2.8 Message Filtering and Validation

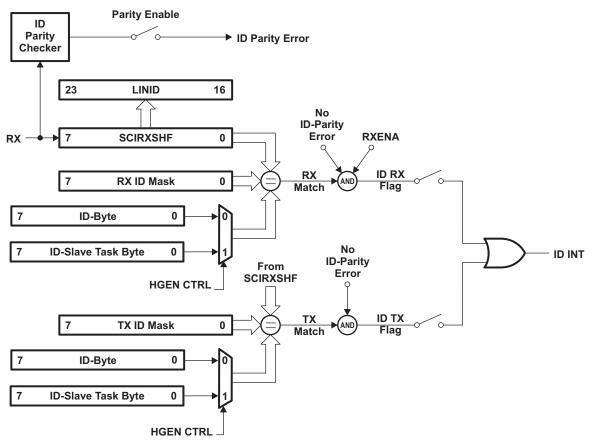

Message filtering uses the entire identifier to determine which nodes will participate in a response, either receiving or transmitting a response. Therefore, two acceptance masks are used as shown in Figure 14.

#### Figure 14. ID Reception, Filtering and Validation

During header reception, all nodes filter the received ID-Field and decide whether they transmit or receive a response for the current message. There are two masks: one to receive a response; the other to initiate a transmission. All nodes compare the received ID to the identifier stored in the ID-SlaveTask BYTE field of the LINID register (Section 6.19) and use the RX-ID MASK and the TX-ID MASK fields in the LINMASK register (Section 6.18) to filter the bits of the identifier that should not be compared.

If there is an RX match with no parity error and the RXENA (SCIGCR1[24]; Section 6.2) bit is set, there will be an ID RX flag and an interrupt will be triggered if enabled. If there is a TX match with no parity error and the TXENA (SCIGCR1[25]; Section 6.2) bit is set, there will be an ID TX flag and an interrupt will be triggered if enabled in the SCISETINT register.

The masked bits become don't cares for the comparison. To build a mask for a set of identifiers, an XOR function could be used.

For example, to build a mask to accept IDs 0x26 and 0x25 using LINID(7–0) = 0x20; i.e., compare five most significant bits (MSBs) and filter three least significant bits (LSBs), the acceptance mask could be:

$$(0x26+0x25) \oplus 0x20 = 0x07$$

A mask of all zeros will compare all bits of the received identifier in the shift register with the ID-BYTE in LINID(7–0). If HGEN CTRL in SCIGCR1 (Section 6.2) is set to 1, a mask of 0xFF will always cause a match. A mask of all 1s will filter all bits of the received identifier, and thus there will be an ID match regardless of the content of the ID-SlaveTask BYTE field in the LINID register (Section 6.19).

**NOTE:** When the HGEN CTRL bit = 0, the LIN nodes compare the received ID to the ID-BYTE field in the LINID register, and uses the RX-ID MASK and the TX-ID MASK in the LINMASK register to filter the bits of the identifier that should not be compared.

If there is an RX match with no parity error and the RXENA (SCIGCR1[24]) bit is set, there will be an ID RX flag and an interrupt will be triggered if enabled. A mask of all 0s will compare all bits of the received identifier in the shift register with the ID-BYTE field in LINID(7–0). A mask of all 1s will filter all bits of the received identifier and there will be no match.

#### If HGEN CTRL = 1:

Received ID is compared with the ID-SlaveTask byte, using the RX-ID mask and the TX-ID mask. A mask of all ones will always result in a match.

A mask of all zeroes means all the bits must be the same to result in a match.

If a mask has some bits which are ones, then those bits will not be used for the filtering criterion. If **HGEN CTRL = 0**:

Received ID is compared with the ID-Byte, using the RX-ID mask and the TX-ID mask.

A mask of all ones will result in No-match.

A mask of all zeroes means all the bits must be the same to result in a match.

If a mask has some bits which are ones, then those bits will not be used for the filtering criterion.

During header reception, the received identifier is copied to the RECEIVED ID field [23:16] in the LINID register. If there is no parity error and there is either a TX match or an RX match, then the corresponding TX or RX ID flag is set (SCIFLR[13] or SCIFLR[14]; Section 6.8). If the ID interrupt is enabled (SCISETINT[13] = 1; Section 6.4), then an ID interrupt is generated.

After the ID interrupt is generated, the CPU may read the LINID (23–16) buffer and determine what response to load into the transmit buffers.

**NOTE:** When byte 0 is written to TDO (LINTDO(31–24), the response transmission is automatically generated.

In multibuffer mode, the TXRDY flag (Section 6.8) will be set when all the response data bytes and checkbyte are copied to the shift register SCITXSHF, which is a shadow register not accessible by the user.

In any other mode, the TXRDY flag is set each time a byte is copied to the SCITXSHF register and the last byte of the frame after the checkbyte is copied to the SCITXSHF register.

In multibuffer mode, the TXEMPTY flag is set when both the transmit buffer(s) TDy and the SCITXSHF shift register are emptied and after the checksum has been sent.

In any other mode, TXEMPTY is set each time TD0 and SCITXSHF are emptied except for the last byte of the frame where the checkbyte must also be transmitted. In multibuffer mode, TXEMPTY is set when the checkbyte has been transmitted.

If parity is enabled (bit SCIGCR1[3]), all slave receiving nodes will validate the identifier using all eight bits of the received ID byte. The SCI/BLIN will flag a corrupted identifier because of an IDparity error.

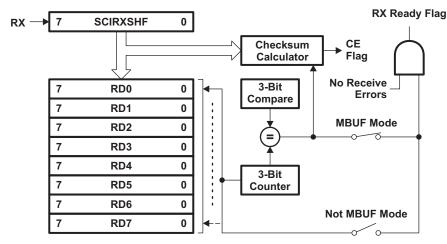

#### 2.9 Receive Buffers

To reduce CPU load when receiving a LIN N-byte (with N = 1–8) response in interrupt mode, the SCI/BLIN module has eight receive buffers; see Figure 15. These buffers can store an entire LIN response in the RDy receive buffers (SCIGCR1[11]; Section 6.2). Also, these receive buffers may be used in buffered SCI mode (the LIN MODE bit, SCIGCR1[6], = 0 and the MBUF MODE bit, SCIGCR1[10], = 1).

Figure 15. Receive Buffers

The checkbyte following the data bytes should be validated by the checksum calculator in the TED logic. The checksum error flag indicates a checksum error and a CE interrupt will be generated if enabled in the SCISETINT register.

The multibuffer 3-bit counter counts the data bytes transferred from the SCIRXSHF register to the RDy receive buffers (Section 6.16–Section 6.17) if multibuffer mode is enabled, or to RD0 if multibuffer mode is disabled. The 3-bit compare register contains the number of data bytes expected to be received. Therefore, it should be loaded with the length control field (bits 4 and 5) of the ID BYTE field received during the header reception. In cases where the ID BYTE field does not convey message length, the LENGTH value, SCIFORMAT(18–16) (Section 6.11), indicates the expected length and should be used to load the 3-bit compare register. Whether the length control field or the LENGTH value is used is selectable with the SCIGCR1[0] bit in communication mode.

A receive interrupt (RX interrupt; see the SCIINTVECT0/1 registers in Section 6.9/Section 6.10, and a receive ready RXRDY flag (SCIFLR[9]; Section 6.8) could occur after receiving a response if there are no response receive errors for the frame (checksum error, frame error, and overrun error). The checkbyte will be compared before acknowledging a reception.

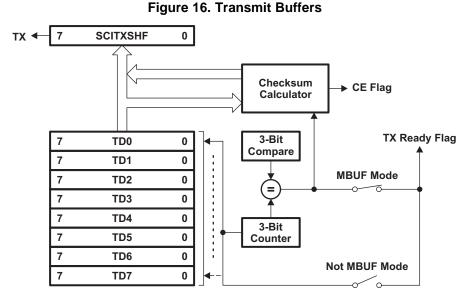

#### 2.10 Transmit Buffers

To reduce the CPU load when transmitting a LIN N-byte (with N = 1–8) response in interrupt mode, the SCI/BLIN module has eight transmit buffers, TD0–TD7 in LINTDO and LINTD1 (Section 6.20 and Section 6.21). With these buffers, it can preload an entire LIN response field in the TXy transmit buffers. Also, these transmit buffers may be used in buffered SCI mode (LIN MODE bit, SCIGCR1[6], = 0 and MBUF MODE bit, SCIGCR1[10], = 1).

The multibuffer 3-bit counter counts the data bytes transferred from the TDy transmit buffers register in multibuffer mode, or from TD0 to SCITXSHF if multibuffer mode is disabled. The 3-bit compare register contains the number of data bytes expected to be transmitted. Therefore it should be loaded with the length control field (bits 4 and 5) of the ID BYTE (Section 6.19) received during the header reception. If the ID field is not used to convey message length, the LENGTH value, SCIFORMAT(18–16), indicates the expected length and should be used instead to load the 3-bit compare register. Which bit field is used is selectable with the COMM MODE bit in LIN mode, SCIGCR1[0].

A transmit interrupt (TX interrupt) and a transmit ready flag (TX ready flag) could occur after transmitting a response.

Figure 16 illustrates the transmit buffers.

The checkbyte will be generated by the checksum calculator and sent after the data-fields transmission is finished. The multibuffer 3-bit counter counts the data bytes transferred from the TDy buffers into the SCITXSHF register.

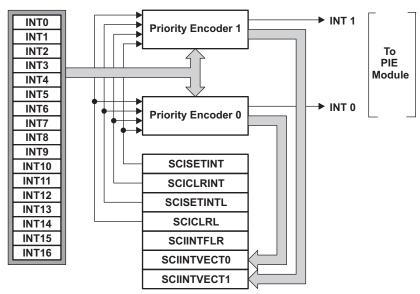

#### 3 Interrupts

The SCI/BLIN module has two interrupt lines, level 0 and level 1, to the peripheral interrupt expansion (PIE) module (see Figure 17). Two offset registers (SCIINTVECT0 and SCIINTVECT1; and Section 6.10) determine which flag triggered the interrupt according to the respective priority encoders. Each interrupt has a bit to enable/disable the interrupt in the SCISETINT and SCICLRINT registers (Section 6.6 and Section 6.7), respectively.

Each interrupt has a bit to be set as interrupt level 0 or as interrupt level 1. By default, interrupts are in line level 0. SCISETINTLVL sets a given interrupt to line level1. SCICLEARINTLVL (Section 6.7) resets a given interrupt level to the default line level 0.

The interrupt vector registers SCIINTVECT0 and SCIINTVECT1 (and Section 6.10) return the vector of the pending interrupt line INT0 or INT1. If more than one interrupt is pending, the interrupt vector register holds the highest priority interrupt.

If multiple interrupts are pending, interrupts must be disabled and re-enabled after the first interrupt is serviced, in order for the other pending interrupts to be serviced.

Figure 17. General Interrupt Scheme

There are 16 interrupt sources in the SCI/BLIN module, with 9 being LIN mode only, as seen in Table 3.

| Offset <sup>(1)</sup> | Interrupt                                  | Comment        |

|-----------------------|--------------------------------------------|----------------|

| 0                     | No interrupt                               |                |

| 1                     | Wakeup                                     | SCI + LIN mode |

| 2                     | Inconsistent-synch-field error             | LIN mode only  |

| 3                     | Parity error                               | SCI + LIN mode |

| 4                     | ID                                         | LIN mode only  |

| 5                     | Physical bus error                         | LIN mode only  |

| 6                     | Frame error                                | SCI + LIN mode |

| 7                     | Break detect                               | SCI mode only  |

| 8                     | Checksum error                             | LIN mode only  |

| 9                     | Overrun error                              | SCI + LIN mode |

| 10                    | Bit error                                  | LIN mode only  |

| 11                    | Receive                                    | SCI + LIN mode |

| 12                    | Transmit                                   | SCI + LIN mode |

| 13                    | No-response error                          | LIN mode only  |

| 14                    | Timeout after wakeup signal (150 ms)       | LIN mode only  |

| 15                    | Timeout after three wakeup signals (1.5 s) | LIN mode only  |

| 16                    | Timeout (Bus Idle, 4s)                     | LIN mode only  |

Table 3. SCI/BLIN Interrupts

<sup>(1)</sup> Offset 1 is the highest priority. Offset 16 is the lowest priority.

For each of the interrupt sources FLAGx, the SCISETINT and SCICLRINT register pair is used to enable/ disable the interrupt. For each source, the interrupt line can be chosen to be INT0 or INT1 with the SCISETINTLVL and SCICLRINTLVL register pair.

## A LIN message frame indicating the timing and sequence of the according LIN interrupts that could occur is shown in Figure 19.

Figure 19. LIN Message Frame Showing LIN Interrupt Timing and Sequence"

#### 4 Low-Power Mode

The SCI/BLIN module enters low-power mode when a sleep command frame is received. A wakeup signal will terminate the sleep mode of the LIN bus. On receipt of the sleep command, the POWERDOWN bit in SCIGCR2 (Section 6.3) must be set by the application software and the module enters local low-power mode.

- **NOTE:** If the module needs to be able to wake up upon a wake-up request, the following sequence should be followed:

- 1. Enable wakeup interrupt in the SCISETINT register (Section 6.4).

- 2. Set the POWERDOWN bit.

The SCI/BLIN module can be put in either local or global low-power mode. Global low-power mode is asserted by the system and is not controlled by the SCI/BLIN module. During global low-power mode (HALT and STANDBY), all clocks to the SCI/BLIN are turned off so the module is completely inactive.

#### NOTE: Enabling Local Low-Power Mode During Receive and Transmit.

If the wakeup interrupt is enabled and low-power mode is requested while the receiver is receiving data, then the SCI/BLIN immediately generates a wake-up interrupt to clear the powerdown bit. Thus, the SCI/BLIN is prevented from entering low-power mode and completes the current reception. Otherwise, if the wakeup interrupt is disabled, the SCI/BLIN completes the current reception and then enters the lowpower mode.

#### 4.1 Entering Sleep Mode

In LIN mode, a sleep command is used to broadcast the sleep mode to all nodes. The sleep command consists of a diagnostic master request frame with identifier 0x3C (60), with the first data field as 0x00. There should be no activity in the bus once all nodes receive the sleep command: the bus is in sleep mode.

Local low-power mode is asserted by setting the POWERDOWN (SCIGCR2[0]; Section 6.3 ) bit; setting this bit stops the clocks to the SCI/BLIN internal logic and registers. Clearing the POWERDOWN bit causes SCI/ BLIN to exit from local low-power mode. All the registers are accessible during local power-down mode. If a register is accessed in low-power mode, this access results in enabling the clock to the module for that particular access alone.

#### 4.2 Wakeup

The wakeup interrupt is used to allow the SCI/BLIN module to automatically exit low-power mode. A SCI/BLIN wakeup is triggered when a low level is detected on the LINRX pin, and this clears the POWERDOWN bit.

- **NOTE:** A node which is not in power-down mode but is receiving a wake-up pulse will not trigger a wake-up interrupt. Wake-up interrupt can only be triggered if the module is in power-down mode.

- **NOTE:** If the wakeup interrupt is disabled (WAKEUP INT in the SCISETINT register is cleared), then the SCI/BLIN enters low-power mode whenever it is requested to do so, but a low level on the receive RX pin does NOT cause the SCI/BLIN to exit low-power mode.

In LIN mode, any node can terminate sleep mode by sending a wakeup signal; see Figure 20. A slave node that detects the bus in sleep mode, if a wakeup request is pending, will send a wakeup signal. The wakeup signal is generated with a dominant value on the LIN bus for  $T_{WUSIG}$ ; this should be at least 5  $T_{bits}$  for the LIN bus baud rates. The wakeup signal should be generated by sending an 0xF0 byte containing 5 dominant  $T_{bits}$  and 5 recessive  $T_{bits}$ .

0.25 ms≤T<sub>WUSIG</sub>≤ 5ms

Assuming a perfect bus with no noise or loading effects, a write of 0xF0 to TD0 will load the transmitter to meet the wakeup signal timing requirement for TWUSIG. Then, setting the GENWU bit (SCIGCR2[8]; Section 6.3) will transmit the preloaded value in TD0 for a wakeup signal transmission. The ability of a node to transmit a wakeup is independent of the value of the TXENA (SCIGCR1.25) bit.

**NOTE:** The GENWU bit can be set/reset only when SWnRST is set to 1 and the node is in power down mode. The bit will be cleared on a valid synch break detection. A master sending a wakeup request, will exit power down mode upon reception of the wakeup pulse. The bit will be cleared on a SWnRST (SCIGCR1[7]; Section 6.2). This can be used to stop a master from sending further wakeup requests.

The TI TPIC1021 LIN transceiver, upon receiving a wakeup signal, will translate it to the microcontroller for wakeup with a dominant level on the LINRX pin, or a signal to the voltage regulator. While the POWERDOWN (SCIGCR2[0]; Section 6.3) bit is set, if the SCI/BLIN module detects a dominant level in the LINRX pin, it will generate a wakeup interrupt if enabled in the SCISETINT register (Section 6.4).

The TI TPIC1021 LIN transceiver will detect a dominant level on the bus longer than 150 ms as a wakeup request. The SCI/BLIN controller's slave should be ready to listen to the bus in less than 100 ms ( $T_{INITIALIZE}$ <100 ms) after a dominant-to-recessive edge (end-of-wakeup signal).

#### 4.3 Wakeup Timeouts

The LIN protocol defines the following timeouts for a wakeup sequence. After a wakeup signal has been sent to the bus, all nodes wait for the master to send a header. If no synch field is detected before 150 ms (3,000 cycles at 20 kHz) after dominant wakeup signal's ending edge, a new wakeup is sent by the same node that requested the first wakeup. This sequence is not repeated more than three times. After three attempts to wake up the LIN bus, wakeup signal generation is suspended for a 1.5 s (30,000 cycles at 20 kHz) period.

- **NOTE:** The SCI/BLIN controller handles the wakeup expiration times defined by the LIN protocol with a hardware implementation.

- **NOTE:** The MBRS register (Section 6.22) must be set to assure that the LIN 2.0 (real-timebased) timings meet the LIN 1.3 bit time base. A node triggering the wakeup should set the MBRS register accordingly to meet the targeted time as 128 T<sub>bits</sub> x programmed prescaler.

#### 5 Emulation Mode

In emulation mode, the CONT bit of the SCIGCR1 (Section 6.2) determines how the SCI/BLIN operates when the program is suspended. The SCI/BLIN counters are affected by this bit during debug mode; when set, the counters are not stopped and when cleared, the counters are stopped.

Any reads in emulation mode to a SCI/BLIN register will not have any effect on the flags in the SCIFLR register (Section 6.8).

#### 6 SCI/BLIN Control Registers

The SCI/BLIN module registers are based on the SCI registers, with added functionality registers enabled by the LIN MODE bit in the SCIGCR1 register.

These registers are accessible in 8-, 16-, and 32-bit reads or writes. The SCI/BLIN is controlled and accessed through the registers listed in Table 4. Among the features that can be programmed are the LIN protocol mode, communication and timing modes, baud rate value, frame format, and interrupt configuration.

| Address | Register       | Description                                                              | Section        |

|---------|----------------|--------------------------------------------------------------------------|----------------|

| 0x6C00  | SCIGCR0        | Global Control Register 0                                                | Section 6.1    |

| 0x6C02  | SCIGCR1        | Global Control Register 1                                                | Section 6.2    |

| 0x6C04  | SCIGCR2        | Global Control Register 2                                                | Section 6.3    |

| 0x6C06  | SCISETINT      | Interrupt Enable Register                                                | Section 6.4    |

| 0x6C08  | SCICLEARINT    | Interrupt Disable Register                                               | Section 6.5    |

| 0x6C0A  | SCISETINTLVL   | Set Interrupt Level Register                                             | Section 6.6    |

| 0x6C0C  | SCICLEARINTLVL | Clear Interrupt Level Register                                           | Section 6.7    |

| 0x6C0E  | SCIFLR         | Flag Register                                                            | Section 6.8    |

| 0x6C10  | SCIINTVECT0    | Interrupt Vector Offset Register 0                                       | Section 6.9    |

| 0x6C12  | SCIINTVECT1    | Interrupt Vector Offset Register 1                                       | Section 6.10   |

| 0x6C14  | SCIFORMAT      | Length Control register                                                  | Section 6.11   |

| 0x6C16  | BRSR           | Baud Rate Selection Register                                             | Section 6.12   |

| 0x6C18  | SCIED          | Emulation buffer register                                                | Section 6.13.1 |

| 0x6C1A  | SCIRD          | Receiver data buffer register                                            | Section 6.13.2 |

| 0x6C1C  | SCITD          | Transmit data buffer register                                            | Section 6.13.3 |

| 0x6C22  | SCIPIO2        | Pin control register 2                                                   | Section 6.14   |

| 0x6C30  | LINCOMP        | Compare register                                                         | Section 6.15   |

| 0x6C32  | LINRD0         | Receive data register 0                                                  | Section 6.16   |

| 0x6C34  | LINRD1         | Receive data register 1                                                  | Section 6.17   |

| 0x6C36  | LINMASK        | Acceptance mask register                                                 | Section 6.18   |

| 0x6C38  | LINID          | Register containing ID- byte, ID-SlaveTask byte, and ID received fields. | Section 6.19   |

| 0x6C3A  | LINTD0         | Transmit Data Register 0                                                 | Section 6.20   |

| 0x6C3C  | LINTD1         | Transmit Data Register 1                                                 | Section 6.21   |

| 0x6C3E  | MBRSR          | Baud Rate Selection Register                                             | Section 6.22   |

| 0x6C48  | IODFTCTRL      | IODFT for BLIN                                                           | Section 6.23   |

#### **Table 4. LIN Registers**

SCI/BLIN Control Registers

www.ti.com

#### SCI Global Control Register 0 (SCIGCR0)

| 31 |          |   | 16         |

|----|----------|---|------------|

|    | Reserved |   |            |

|    | R-0      |   |            |

|    |          |   |            |

| 15 |          | 1 | 0          |

| 15 | Reserved | 1 | 0<br>RESET |

#### SCI Global Control Register (SCIGCR1)

| 31      |          |            |           |        | 26         | 25          | 24        |

|---------|----------|------------|-----------|--------|------------|-------------|-----------|

|         |          | Rese       | erved     |        |            | TXENA       | RXENA     |

|         |          | R-         | -0        |        |            | R/W-0       | R/W-0     |

| 23      |          |            |           |        | 18         | 17          | 16        |

|         |          | Rese       | erved     |        |            | CONT        | LOOP BACK |

|         |          | R-         | -0        |        |            | R/W-0       | R/W-0     |

| 15      | 14       | 13         | 12        | 11     | 10         | 9           | 8         |

| Rese    | Reserved |            | HGEN CTRL | CTYPE  | MBUF MODE  | ADAPT       | SLEEP     |

| R       | -0       | R/WL-0     | R/WL-0    | R/WL-0 | R/W-0      | R/WL-0      | R/WC-0    |

| 7       | 6        | 5          | 4         | 3      | 2          | 1           | 0         |

| SW nRST | LIN MODE | CLK_MASTER | STOP      | PARITY | PARITY ENA | TIMING MODE | COMM MODE |

| R/W-0   | R/W-0    | R/W-0      | R/WC-0    | R/WC-0 | R/W-0      | R/W-0       | R/W-0     |

#### SCI Global Control Register (SCIGCR2)

| 31       |         |       |   |          | 18 | 17     | 16            |

|----------|---------|-------|---|----------|----|--------|---------------|

|          | Reserve | ed    |   |          |    | CC     | SC            |

|          | R-0     |       |   |          |    | R/W-L0 | R/WL-0        |

| 15       | 9       | 8     | 7 |          |    | 1      | 0             |

| Reserved | 3       | GENWU |   | Reserved |    |        | POWER<br>DOWN |

| R-0      |         | R/W-0 |   | R-0      |    |        | R/W-0         |

### SCI Set Interrupt Register (SCISETINT)

| 31                  | 30                 | 29         | 28                | 27          | 26         | 25                 | 24               |

|---------------------|--------------------|------------|-------------------|-------------|------------|--------------------|------------------|

| SET BE INT          | SET PBE INT        | SET CE INT | SETISFE INT       | SET NRE INT | SET FE INT | SET OE INT         | SET PE INT       |

| R/WL-0              | R/WL-0             | R/WL-0     | R/WL-0            | R/WL-0      | R/W-0      | R/W-0              | R/W-0            |

| 23                  |                    |            |                   |             |            |                    | 16               |

|                     |                    |            | Rese              | erved       |            |                    |                  |

|                     |                    |            | R                 | -0          |            |                    |                  |

| 15                  | 14                 | 13         | 12                |             | 10         | 9                  | 8                |

| Res                 | erved              | SET ID INT |                   | Reserved    |            | SET RX INT         | SET TX INT       |

| R                   | -0                 | R/WL-0     |                   | R-0         |            | R/W-0              | R/W-0            |

| 7                   | 6                  | 5          | 4                 | 3           | 2          | 1                  | 0                |

| SET TOA3<br>WUS INT | SET TOA WUS<br>INT | Reserved   | SETTIMEOUT<br>INT | Rese        | rved       | SET WAKE UP<br>INT | SET BRKDT<br>INT |

| R/WL-0              | R/WL-0             | R-0        | R/WL-0            | R           | -0         | R/W-0              | R/WC-0           |

#### TEXAS INSTRUMENTS

www.ti.com

#### SCI/BLIN Control Registers

|                     |                    | SCI C      | lear Interrupt    | Register (SC | ICLEARINT) |                    |                  |

|---------------------|--------------------|------------|-------------------|--------------|------------|--------------------|------------------|

| 31                  | 30                 | 29         | 28                | 27           | 26         | 25                 | 24               |

| CLR BE INT          | SET PBE INT        | CLR CE INT | CLRISFE INT       | CLR RE INT   | CLR FE INT | CLR OE INT         | CLR PE INT       |

| R/WL-0              | R/WL-0             | R/WL-0     | R/WL-0            | R/WL-0       | R/W-0      | R/W-0              | R/W-0            |

| 23                  |                    |            |                   |              |            |                    | 16               |

|                     |                    |            | Rese              | rved         |            |                    |                  |

|                     |                    |            | R-                | ·0           |            |                    |                  |

| 15                  | 14                 | 13         | 12                |              | 10         | 9                  | 8                |

| Res                 | erved              | CLR ID INT |                   | Reserved     |            | CLR RX INT         | CLR TX INT       |

| R                   | -0                 | R/WL-0     |                   | R-0          |            | R/W-0              | R/W-0            |

| 7                   | 6                  | 5          | 4                 | 3            | 2          | 1                  | 0                |

| CLR TOA3<br>WUS INT | CLR TOA WUS<br>INT | Reserved   | CLRTIMEOUT<br>INT | Rese         | erved      | CLR WAKE UP<br>INT | CLR BRKDT<br>INT |

| R/WL-0              | R/WL-0             | R-0        | R/WL-0            | R            | -0         | R/W-0              | R/WC-0           |

#### SCI Set Interrupt Level Register (SCISETINTLVL)

| 31                    | 30                   | 29                | 28                    | 27                 | 26                | 25                     | 24                   |

|-----------------------|----------------------|-------------------|-----------------------|--------------------|-------------------|------------------------|----------------------|

| SET BE INT<br>LVL     | SET PBE INT<br>LVL   | SET CE INT<br>LVL | SET ISFE INT<br>LVL   | SET NRE INT<br>LVL | SET FE INT<br>LVL | SET OE INT<br>LVL      | SET PE INT<br>LVL    |

| 23                    |                      |                   | 272                   |                    |                   |                        | 16                   |

|                       |                      |                   | Rese                  | erved              |                   |                        |                      |

|                       |                      |                   | R                     | -0                 |                   |                        |                      |

| 15                    | 14                   | 13                | 12                    | 11                 | 10                | 9                      | 8                    |

| Rese                  | erved                | SET ID INT<br>LVL |                       | Reserved           |                   | SET RX INT<br>LVL      | SET TX INT<br>LVL    |

| R                     | -0                   |                   | L                     | R-0                |                   |                        |                      |

| 7                     | 6                    | 5                 | 4                     | 3                  | 2                 | 1                      | 0                    |

| SETTOA3WUS<br>INT LVL | SETTOAWUS<br>INT LVL | Reserved          | SETTIMEOUT<br>INT LVL | Rese               | erved             | SET WAKE UP<br>INT LVL | SET BRKDT<br>INT LVL |

|                       |                      | R-0               |                       | R                  | -0                |                        |                      |