# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC22 1999 Jul 01

# SAA7113H

### CONTENTS

| CONTEN                                                                              | 15                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                   | FEATURES                                                                                                                                                                                                                                                                                                               |

| 2                                                                                   | APPLICATIONS                                                                                                                                                                                                                                                                                                           |

| 3                                                                                   | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                    |

| 4                                                                                   | QUICK REFERENCE DATA                                                                                                                                                                                                                                                                                                   |

| 5                                                                                   | ORDERING INFORMATION                                                                                                                                                                                                                                                                                                   |

| 6                                                                                   | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                          |

| 7                                                                                   | PINNING                                                                                                                                                                                                                                                                                                                |

| 8                                                                                   | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                 |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10<br>8.11<br>8.12 | Analog input processing<br>Analog control circuits<br>Chrominance processing<br>Luminance processing<br>Synchronization<br>Clock generation circuit<br>Power-on reset and CE input<br>Multi-standard VBI data slicer<br>VBI-raw data bypass<br>Digital output port VPO7 to VPO0<br>RTCO output<br>RTS0, RTS1 terminals |

| 9                                                                                   | BOUNDARY SCAN TEST                                                                                                                                                                                                                                                                                                     |

| 9.1<br>9.2                                                                          | Initialization of boundary scan circuit<br>Device identification codes                                                                                                                                                                                                                                                 |

| 10                                                                                  | LIMITING VALUES                                                                                                                                                                                                                                                                                                        |

| 11                                                                                  | THERMAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                |

| 12                                                                                  | CHARACTERISTICS                                                                                                                                                                                                                                                                                                        |

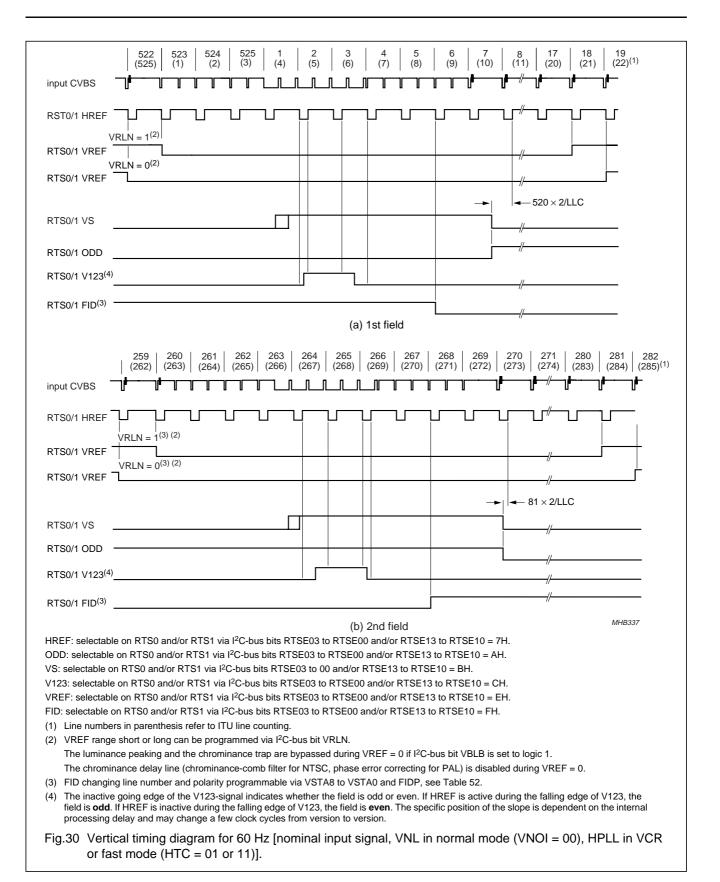

| 13                                                                                  | TIMING DIAGRAMS                                                                                                                                                                                                                                                                                                        |

| 14                                                                                  | APPLICATION INFORMATION                                                                                                                                                                                                                                                                                                |

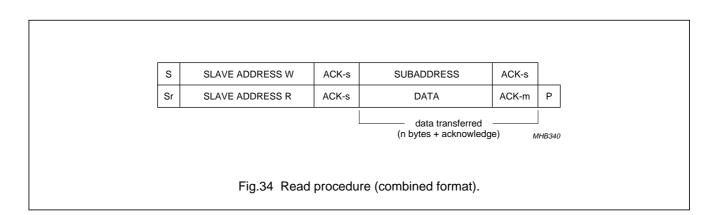

| 15                                                                                  | I <sup>2</sup> C-BUS DESCRIPTION                                                                                                                                                                                                                                                                                       |

| 15.1<br>15.2                                                                        | l <sup>2</sup> C-bus format<br>l <sup>2</sup> C-bus detail                                                                                                                                                                                                                                                             |

| 16                                                                                  | I <sup>2</sup> C-BUS START SET-UP                                                                                                                                                                                                                                                                                      |

| 17                                                                                  | PACKAGE OUTLINE                                                                                                                                                                                                                                                                                                        |

| 18                                                                                  | SOLDERING                                                                                                                                                                                                                                                                                                              |

| 18.1                                                                                | Introduction to soldering surface mount<br>packages                                                                                                                                                                                                                                                                    |

| 18.2<br>18.3<br>18.4<br>18.5<br>19                                                  | Reflow soldering<br>Wave soldering<br>Manual soldering<br>Suitability of surface mount IC packages for<br>wave and reflow soldering methods<br>DEFINITIONS                                                                                                                                                             |

| 20                                                                                  | LIFE SUPPORT APPLICATIONS                                                                                                                                                                                                                                                                                              |

| 21                                                                                  | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                                                                                                                                                                                                                                                        |

|                                                                                     |                                                                                                                                                                                                                                                                                                                        |

# SAA7113H

### 1 FEATURES

- Four analog inputs, internal analog source selectors, e.g. 4 × CVBS or 2 × Y/C or (1 × Y/C and 2 × CVBS)

- Two analog preprocessing channels in differential CMOS style for best S/N-performance

- Fully programmable static gain or automatic gain control for the selected CVBS or Y/C channel

- Switchable white peak control

- Two built-in analog anti-aliasing filters

- Two 9-bit video CMOS Analog-to-Digital Converters (ADCs), digitized CVBS or Y/C-signals are available on the VPO-port via I<sup>2</sup>C-bus control

- · On-chip clock generator

- · Line-locked system clock frequencies

- Digital PLL for horizontal sync processing and clock generation, horizontal and vertical sync detection

- Requires only one crystal (24.576 MHz) for all standards

- Automatic detection of 50 and 60 Hz field frequency, and automatic switching between PAL and NTSC standards

- Luminance and chrominance signal processing for PAL BGHI, PAL N, combination PAL N, PAL M, NTSC M, NTSC N, NTSC 4.43, NTSC-Japan and SECAM

- User programmable luminance peaking or aperture correction

- Cross-colour reduction for NTSC by chrominance comb filtering

- · PAL delay line for correcting PAL phase errors

- Brightness Contrast Saturation (BCS) and hue control on-chip

- Real-time status information output (RTCO)

- Two multi functional real-time output pins controlled by  $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\xspace$ -bus

- Multi-standard VBI-data slicer decoding World Standard Teletext (WST), North-American Broadcast Text System (NABTS), closed caption, Wide Screen Signalling (WSS), Video Programming System (VPS), Vertical Interval Time Code (VITC) variants (EBU/SMPTE) etc.

- Standard ITU 656 YUV 4 : 2 : 2 format (8-bit) on VPO output bus

- Enhanced ITU 656 output format on VPO output bus containing:

- active video

- raw CVBS data for INTERCAST applications (27 MHz data rate)

- decoded VBI data

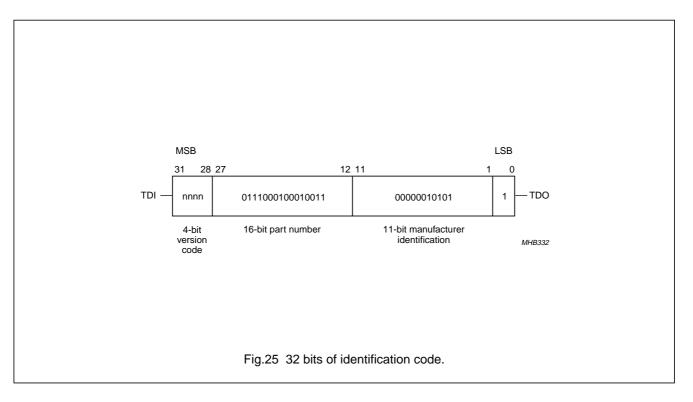

- Boundary scan test circuit complies with the "IEEE Std. 1149.b1 1994" (ID-Code = 1 7113 02B)

- I<sup>2</sup>C-bus controlled (full read-back ability by an external controller, bit rate up to 400 kbits/s)

- Low power (<0.5 W), low voltage (3.3 V), small package (QFP44)

- Power saving mode by chip enable input

- 5 V tolerant digital I/O ports

- Detection of copy protected input signals according to the macrovision standard. Can be used to prevent unauthorized recording of pay-TV or video tape signals.

### 2 APPLICATIONS

- Notebook (low power consumption)

- PCMCIA card application

- AGP based graphics cards

- Image processing

- Video phone applications

- Intercast and PC teletext applications

- Security applications.

# SAA7113H

### **3 GENERAL DESCRIPTION**

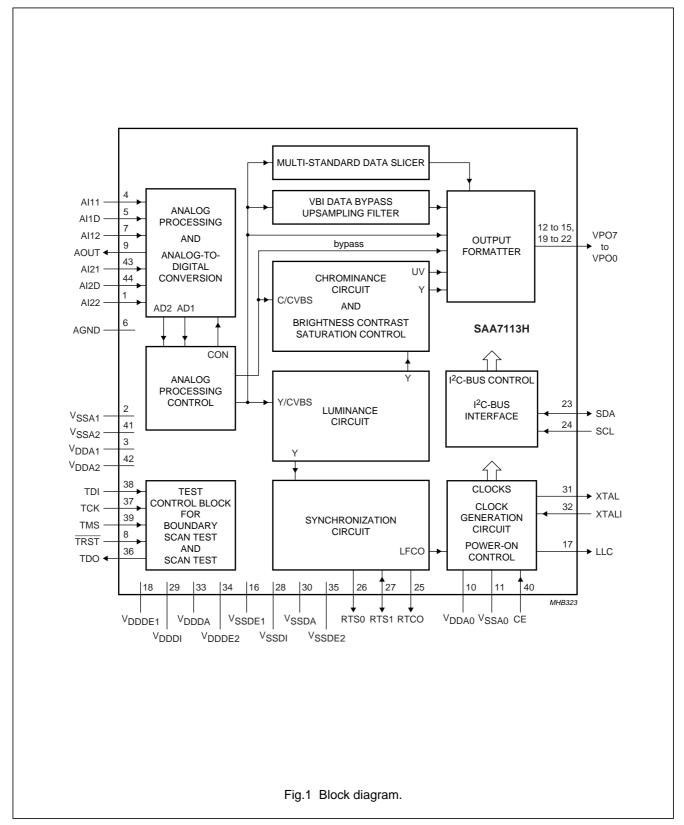

The 9-bit video input processor is a combination of a two-channel analog preprocessing circuit including source selection, anti-aliasing filter and ADC, an automatic clamp and gain control, a Clock Generation Circuit (CGC), a digital multi-standard decoder (PAL BGHI, PAL M, PAL N, combination PAL N, NTSC M, NTSC-Japan, NTSC N and SECAM), a brightness, contrast and saturation control circuit, a multi-standard VBI data slicer and a 27 MHz VBI data bypass; see Fig.1.

The pure 3.3 V (5 V compatible) CMOS circuit SAA7113H, analog front-end and digital video decoder, is a highly integrated circuit for desktop video applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the colour of PAL, SECAM and NTSC signals into CCIR-601 compatible colour component values. The SAA7113H accepts as analog inputs CVBS or S-video (Y/C) from TV or VTR sources. The circuit is I<sup>2</sup>C-bus controlled. The integrated high performance multi-standard data slicer supports several VBI data standards:

- Teletext [WST (World Standard Teletext), CCST (Chinese teletext)] (625 lines)

- Teletext [US-WST, NABTS (North-American Broadcast Text System) and MOJI (Japanese teletext)] (525 lines)

- Closed caption [Europe, US (line 21)]

- Wide Screen Signalling (WSS)

- Video Programming Signal (VPS)

- Time codes (VITC EBU/SMPTE)

- HIGH-speed VBI data bypass for intercast application.

| SYMBOL           | PARAMETER                            | MIN. | TYP. | MAX. | UNIT |

|------------------|--------------------------------------|------|------|------|------|

| V <sub>DDD</sub> | digital supply voltage               | 3.0  | 3.3  | 3.6  | V    |

| V <sub>DDA</sub> | analog supply voltage                | 3.1  | 3.3  | 3.5  | V    |

| T <sub>amb</sub> | operating ambient temperature        | 0    | 25   | 70   | °C   |

| P <sub>A+D</sub> | analog and digital power dissipation | -    | 0.4  | _    | W    |

### 5 ORDERING INFORMATION

QUICK REFERENCE DATA

| TYPE     | PACKAGE |                                                                                              |          |  |

|----------|---------|----------------------------------------------------------------------------------------------|----------|--|

| NUMBER   | NAME    | DESCRIPTION                                                                                  | VERSION  |  |

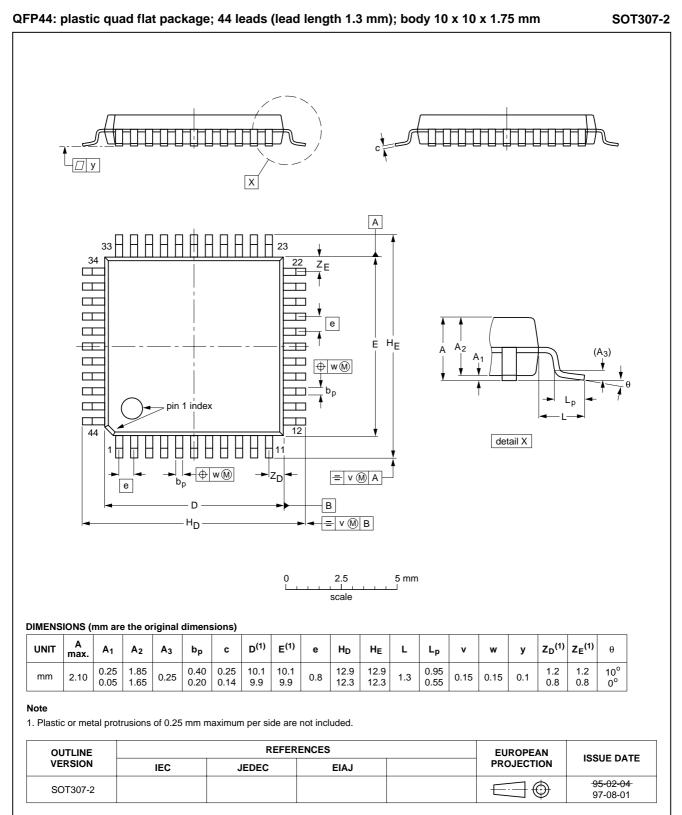

| SAA7113H | QFP44   | plastic quad flat package; 44 leads (lead length 1.3 mm); body $10 \times 10 \times 1.75$ mm | SOT307-2 |  |

### .

4

# SAA7113H

### 6 BLOCK DIAGRAM

SAA7113H

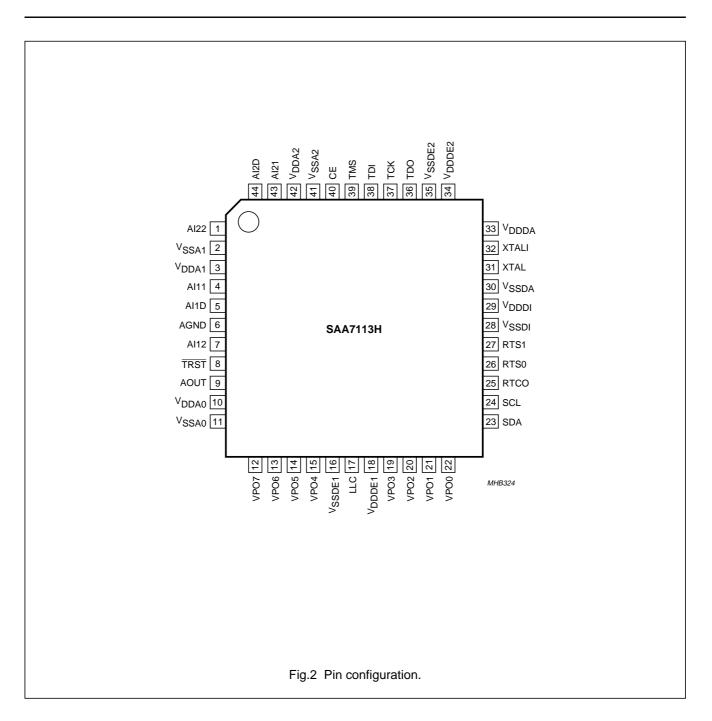

## 7 PINNING

| SYMBOL             | PIN      | I/O/P | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al22               | 1        | 1     | analog input 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SSA1</sub>  | 2        | Р     | ground for analog supply voltage channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDA1</sub>  | 3        | Р     | positive supply voltage for analog channel 1 (+3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AI11               | 4        | I     | analog input 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

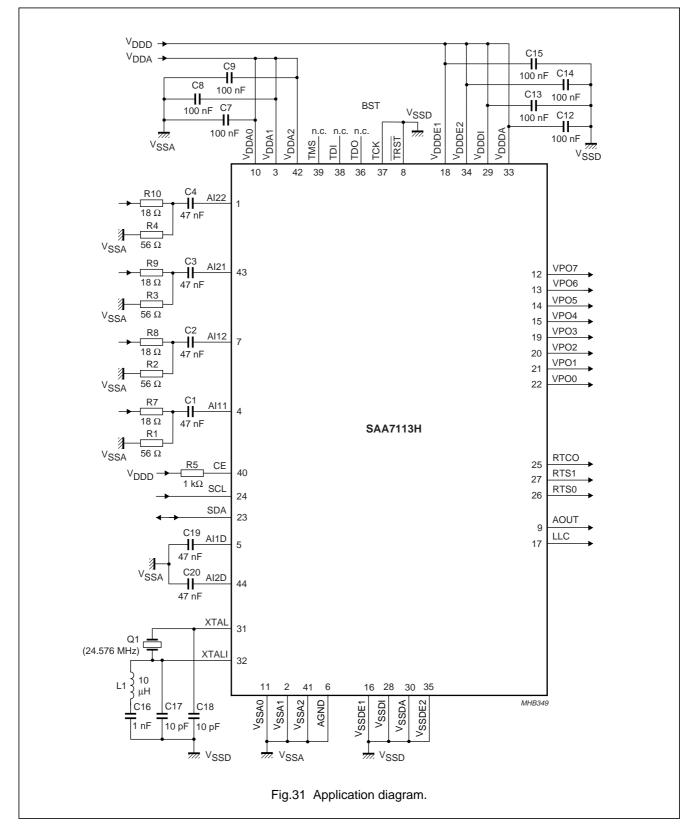

| AI1D               | 5        | I     | differential analog input for AI11 and AI12; has to be connected to ground via a capacitor; see application diagram of Fig.31                                                                                                                                                                                                                                                                                                                                                            |

| AGND               | 6        | Р     | analog signal ground connection                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AI12               | 7        | I     | analog input 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TRST               | 8        | I     | test reset input (active LOW), for boundary scan test; notes 1, 2 and 3                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AOUT               | 9        | 0     | analog test output; for testing the analog input channels, 75 $\Omega$ termination possible                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>DDA0</sub>  | 10       | Р     | positive supply voltage (+3.3 V) for internal Clock Generation Circuit (CGC)                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SSA0</sub>  | 11       | Р     | ground for internal clock generation circuit                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VPO7 to<br>VPO4    | 12 to 15 | 0     | digital VPO-bus output signal; higher bits of the 8-bit output bus. The output data types of the VPO-bus are controlled via $l^2$ C-bus registers LCR2 to LCR24; see Table 4. If $l^2$ C-bus bit VIPB = 1, the higher bits of the digitized input signal are connected to these outputs, configured by the $l^2$ C-bus control signals MODE3 to MODE0                                                                                                                                    |

| V <sub>SSDE1</sub> | 16       | Р     | ground 1 or digital supply voltage input E (external pad supply)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LLC                | 17       | 0     | line-locked system clock output (27 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>DDDE1</sub> | 18       | Р     | digital supply voltage E1 (external pad supply 1; +3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VPO3 to<br>VPO0    | 19 to 22 | 0     | digital VPO-bus output signal; lower bits of the 8-bit output bus. The output data types of the VPO-bus are controlled via I <sup>2</sup> C-bus registers LCR2 to LCR24; see Table 4. If I <sup>2</sup> C-bus bit VIPB = 1, the lower bits of the digitized input signal are connected to these outputs, configured by the I <sup>2</sup> C-bus control signals MODE3 to MODE0                                                                                                           |

| SDA                | 23       | I/O   | serial data input/output (I <sup>2</sup> C-bus) 5 V-compatible                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCL                | 24       | 1     | serial clock input (I <sup>2</sup> C-bus) 5 V-compatible                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RTCO               | 25       | (I/)O | real-time control output: contains information about actual system clock frequency, field rate, odd/even sequence, decoder status, subcarrier frequency and phase and PAL sequence (see external document <i>"RTC Functional Description"</i> , available on request); the RTCO pin is enabled via I <sup>2</sup> C-bus bit OERT; <b>this pin is also used as an input pin for test purposes and has an internal pull-down resistor; do not connect any pull-up resistor to this pin</b> |

| RTS0               | 26       | (I/)O | real-time signal output 0: multi functional output, controlled by l <sup>2</sup> C-bus bits<br>RTSE03 to RTSE00; see Table 49. RTS0 is strapped during power-on or CE driven<br>reset, defines which l <sup>2</sup> C-bus slave address is used; 0 = 48H for write, 49H for read,<br>external pull-down resistor of 3.3 k $\Omega$ is needed; 1 = 4AH for write, 4BH for read,<br>default slave address (default, internal pull-up)                                                      |

| RTS1               | 27       | I/O   | real-time signal I/O terminal 1: multi functional output, controlled by I <sup>2</sup> C-bus bit RTSE13 to RTSE10; see Table 50                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SSDI</sub>  | 28       | Р     | ground for internal digital core supply                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DDDI</sub>  | 29       | Р     | internal core supply (+3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>SSDA</sub>  | 30       | Р     | digital ground for internal crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                           |

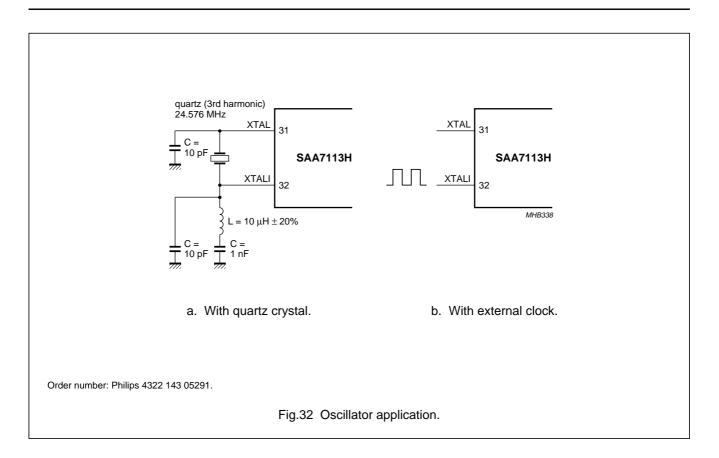

| XTAL               | 31       | 0     | second terminal of crystal oscillator; not connected if external clock signal is used                                                                                                                                                                                                                                                                                                                                                                                                    |

# SAA7113H

| SYMBOL             | PIN | I/O/P | DESCRIPTION                                                                                                                                        |

|--------------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| XTALI              | 32  | I     | input terminal for crystal oscillator or connection of external oscillator with CMOS compatible square wave clock signal                           |

| V <sub>DDDA</sub>  | 33  | Р     | digital positive supply voltage for internal crystal oscillator (+3.3 V)                                                                           |

| V <sub>DDDE2</sub> | 34  | Р     | digital supply voltage E2 (external pad supply 2; +3.3 V)                                                                                          |

| V <sub>SSDE2</sub> | 35  | Р     | ground 2 for digital supply voltage input E (external pad supply)                                                                                  |

| TDO                | 36  | 0     | test data output for boundary scan test; note 3                                                                                                    |

| TCK                | 37  | I     | test clock for boundary scan test; note 3                                                                                                          |

| TDI                | 38  | 1     | test data input for boundary scan test; note 3                                                                                                     |

| TMS                | 39  | I     | test mode select input for boundary scan test or scan test; note 3                                                                                 |

| CE                 | 40  | I     | chip enable, 'sleep mode' with low power consumption if connected to ground (internal pull-up); internal reset sequence is generated when released |

| V <sub>SSA2</sub>  | 41  | Р     | ground for analog supply voltage channel 2                                                                                                         |

| V <sub>DDA2</sub>  | 42  | Р     | positive supply voltage for analog channel 2 (+3.3 V)                                                                                              |

| AI21               | 43  | I     | analog input 21                                                                                                                                    |

| AI2D               | 44  | I     | differential analog input for Al21 and Al22; has to be connected to ground via a capacitor; see application diagram of Fig.31                      |

### Notes

1. For board design without boundary scan implementation connect the  $\overline{\text{TRST}}$  pin to ground.

2. This pin provides easy initialization of BST circuit. TRST can be used to force the Test Access Port (TAP) controller to the TEST\_LOGIC\_RESET state (normal operation) at once.

3. In accordance with the *IEEE1149.1* standard the pads TDI, TMS and TRST are input pads with an internal pull-up transistor and TDO is a 3-state output pad.

SAA7113H

# 9-bit video input processor

### 8 FUNCTIONAL DESCRIPTION

### 8.1 Analog input processing

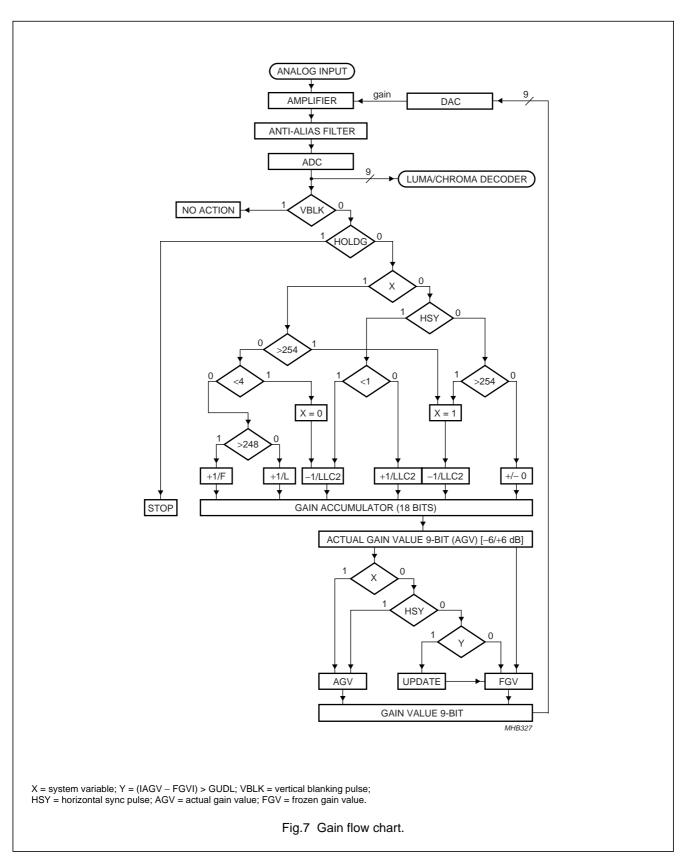

The SAA7113H offers four analog signal inputs, two analog main channels with source switch, clamp circuit, analog amplifier, anti-alias filter and video 9-bit CMOS ADC; see Fig.6.

### 8.2 Analog control circuits

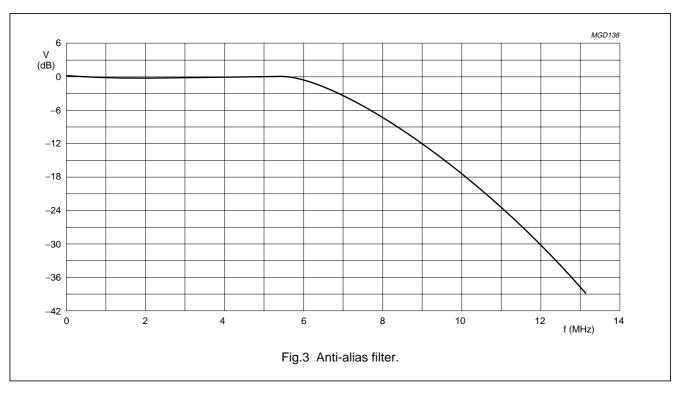

The anti-alias filters are adapted to the line-locked clock frequency via a filter control circuit. The characteristics are shown in Fig.3. During the vertical blanking period, gain and clamping control are frozen.

### 8.2.1 CLAMPING

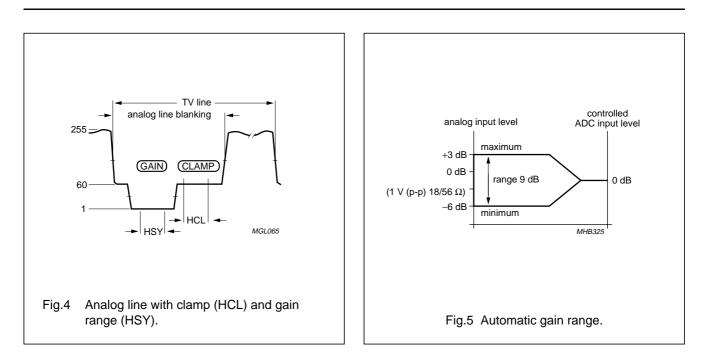

The clamp control circuit controls the correct clamping of the analog input signals. The coupling capacitor is also used to store and filter the clamping voltage. An internal digital clamp comparator generates the information with respect to clamp-up or clamp-down. The clamping levels for the two ADC channels are fixed for luminance (120) and chrominance (256). Clamping time in normal use is set with the HCL pulse at the back porch of the video signal.

### 8.2.2 GAIN CONTROL

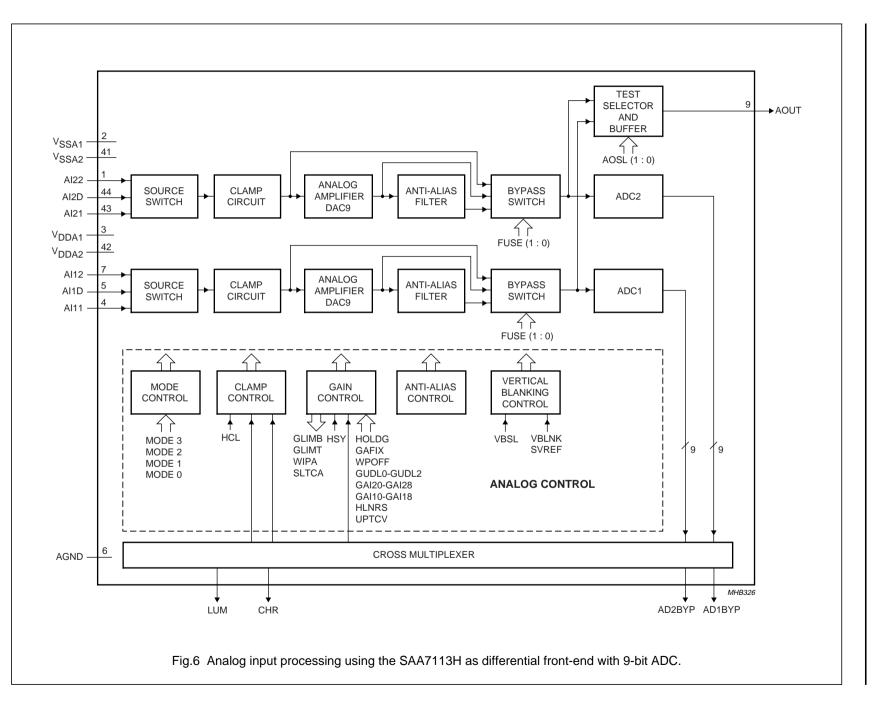

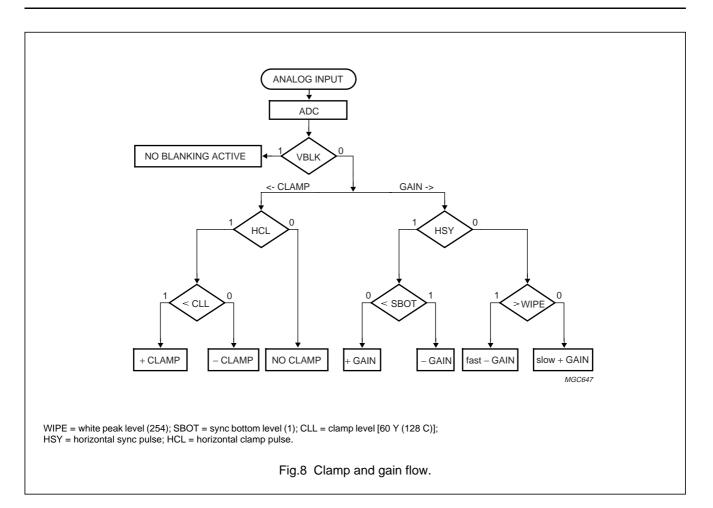

The gain control circuit receives (via the l<sup>2</sup>C-bus) the static gain levels for the two analog amplifiers or controls one of these amplifiers automatically via a built-in Automatic Gain Control (AGC) as part of the Analog Input Control (AICO). The AGC (automatic gain control for luminance) is used to amplify a CVBS or Y signal to the required signal amplitude, matched to the ADCs input voltage range. The AGC active time is the sync bottom of the video signal.

Signal (white) peak control limits the gain at signal overshoots. The flow charts (see Figs 7 and 8) show more details of the AGC. The influence of supply voltage variation within the specified range is automatically eliminated by clamp and automatic gain control.

# SAA7113H

Philips Semiconductors

Product specification

# 9-bit video input processor

SAA7113H

\_

1999 Jul 01

1

# SAA7113H

# SAA7113H

### 8.3 Chrominance processing

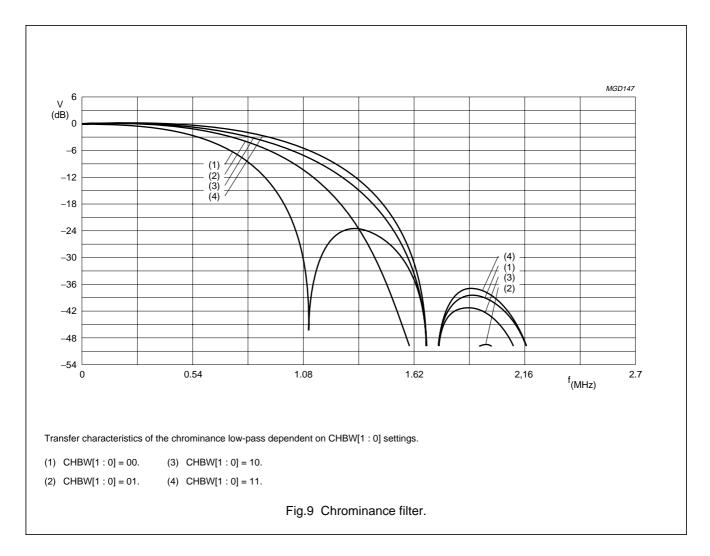

The 9-bit chrominance signal is fed to the multiplication inputs of a quadrature demodulator, where two subcarrier signals from the local oscillator DTO1 are applied (0 and 90° phase relationship to the demodulator axis). The frequency is dependent on the present colour standard. The output signals of the multipliers are low-pass filtered (four programmable characteristics) to achieve the desired bandwidth for the colour difference signals (PAL, NTSC) or the 0 and 90° FM signals (SECAM).

The colour difference signals are fed to the Brightness/Contrast/Saturation block (BCS), which includes the following five functions:

- AGC (automatic gain control for chrominance PAL and NTSC)

- Chrominance amplitude matching (different gain factors for (R Y) and (B Y) to achieve CCIR-601 levels  $C_R$  and  $C_B$  for all standards)

- Chrominance saturation control

- Luminance contrast and brightness

- Limiting YUV to the values 1 (minimum) and 254 (maximum) to fulfil CCIR-601 requirements.

The SECAM-processing contains the following blocks:

- Baseband 'bell' filters to reconstruct the amplitude and phase equalized 0 and 90° FM signals

- Phase demodulator and differentiator (FM-demodulation)

- De-emphasis filter to compensate the pre-emphasized input signal, including frequency offset compensation (DB or DR white carrier values are subtracted from the signal, controlled by the SECAM switch signal).

The burst processing block provides the feedback loop of the chrominance PLL and contains:

- Burst gate accumulator

- Colour identification and killer

- Comparison nominal/actual burst amplitude (PAL/NTSC standards only)

# SAA7113H

- Loop filter chrominance gain control (PAL/NTSC standards only)

- Loop filter chrominance PLL (only active for PAL/NTSC standards)

- PAL/SECAM sequence detection, H/2-switch generation

- Increment generation for DTO1 with divider to generate stable subcarrier for non-standard signals.

The chrominance comb filter block eliminates crosstalk between the chrominance channels in accordance with the PAL standard requirements. For NTSC colour standards the chrominance comb filter can be used to eliminate crosstalk from luminance to chrominance (cross-colour) for vertical structures. The comb filter can be switched off if desired. The embedded line delay is also used for SECAM recombination (cross-over switches).

The resulting signals are fed to the variable Y-delay compensation and the output interface, which contains the VPO output formatter and the output control logic, see Fig.10.

1999 Jul 01

\_

AD2BYP AD1BYP LUM CHR SECAM PROCESSING sequential UV signals TRST 37 тск QUADRATURE LEVEL TEST LOW-PASS 38 DEMODULATOR TDI CONTROL ADJUSTMENT, 39 BRIGHTNESS, BLOCK 12, 13, 14, 15, 19, 20, TMS CONTRAST, 36 TDO ┥ AND 21, 22 VPO7 OUTPUT PHASE SATURATION CONTROL SUBCARRIER GENERATION to FORMATTER DEMODULATOR VPO0 AND RESET SUBCARRIER AMPLITUDE UV INTERFACE  $\wedge$ INCREMENT DETECTOR  $\left\{ \right\}$ GENERATION GAIN 18 V<sub>DDDE1</sub> HUEC AND BURST GATE CONTROL 29 DIVIDER COMB ACCUMULATOR V<sub>DDDI</sub> AND Y-DELAY UV POWER-ON FILTERS 33 COMPENSATION V<sub>DDDA</sub> CONTROL LOOP FILTER SECAM 34 V<sub>DDDE2</sub> RECOMBINATION  $\overline{\mathbf{v}}$  $\left\{ \right\}$ 57 17 17 CODE CSTD 1 CSTD 0 FCTC BRIG DCCF GPSW (1 : 0) RTSE1 (7 : 0) CE CLOCKS CONT OFTS0 OFTS1 SATN INCS RTSE0 (7 : 0) VIPB OEYC 16 V<sub>SSDE1</sub> f<sub>H</sub>/2 switch signal OEHV 28 VSSDI COLO VRLN VBI DATA BYPASS 30 VSTA (8:0) UPSAMPLING VSSDA 35 VSTO (8:0) FILTER V<sub>SSDE2</sub> 25 → RTCO DATA SLICER MULTI-STANDARD DATA SLICER MULTI-STANDARD DATA SLICER INPUT INTERFACING MHB328 Υ LUM Fig.10 Chrominance circuit, text slicer, VBI-bypass, output formatting, power and test control.

Philips Semiconductors

9-bit video input processor

Product specification

**SAA7113H**

**1**ភ

SAA7113H

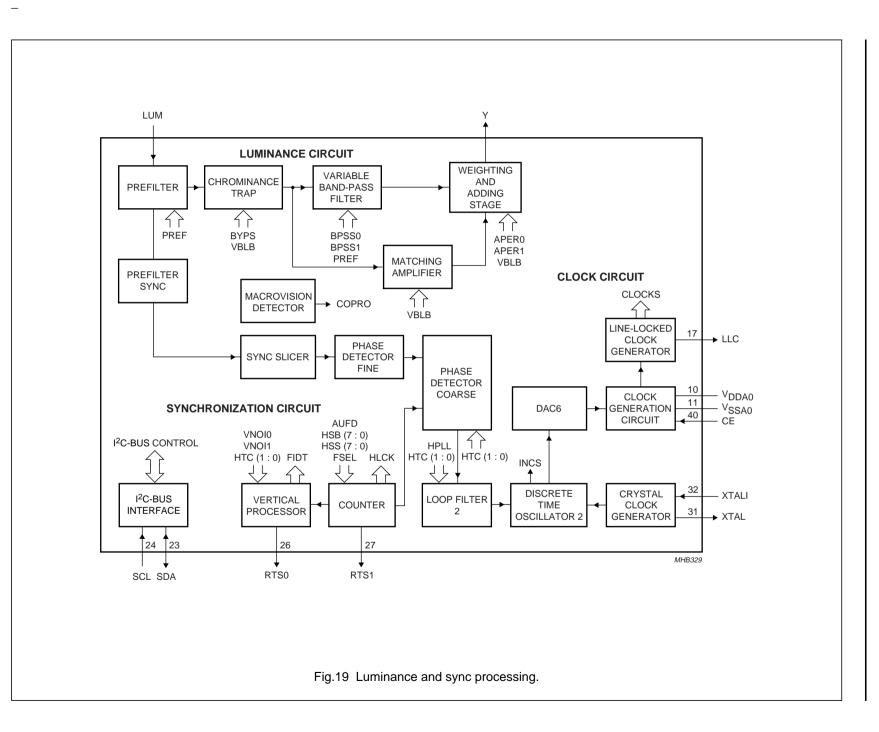

### 8.4 Luminance processing

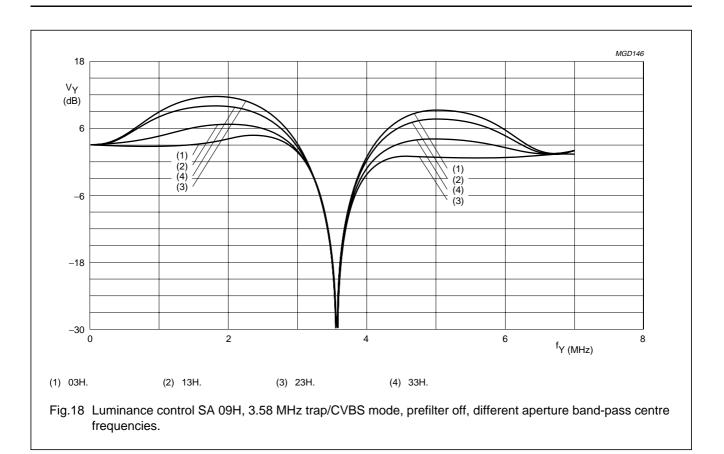

The 9-bit luminance signal, a digital CVBS format or a luminance format (S-VHS, HI8), is fed through a switchable prefilter. High frequency components are emphasized to compensate for loss. The following chrominance trap filter ( $f_0$  = 4.43 or 3.58 MHz centre frequency set according to the selected colour standard) eliminates most of the colour carrier signal. It should be bypassed via I<sup>2</sup>C-bit BYPS (subaddress 09H, bit 7) for S-video (S-VHS, HI8) signals.

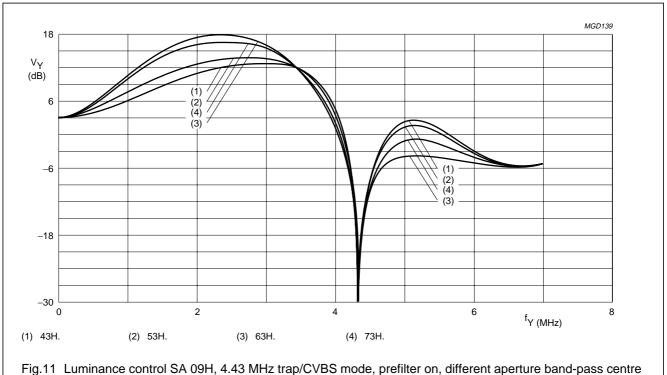

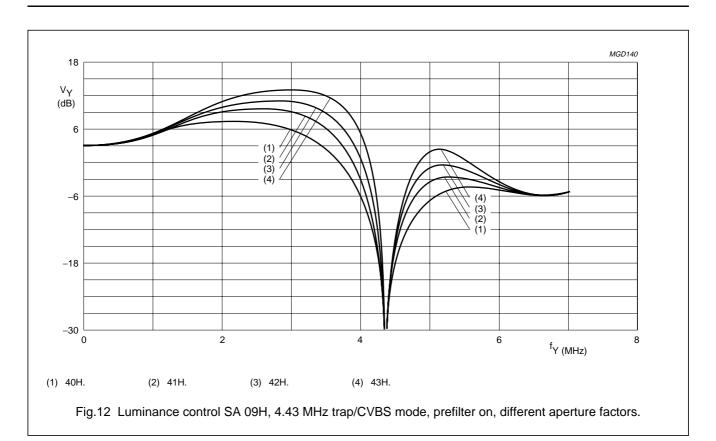

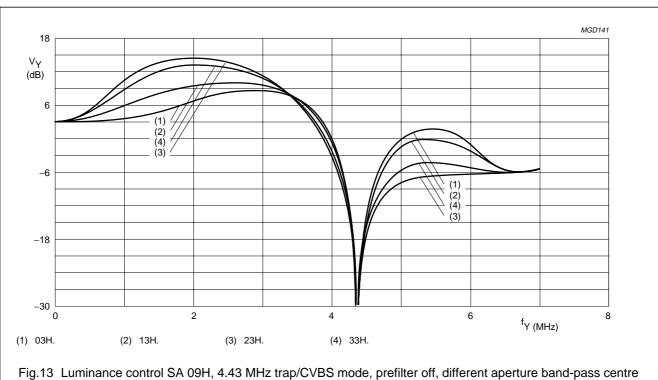

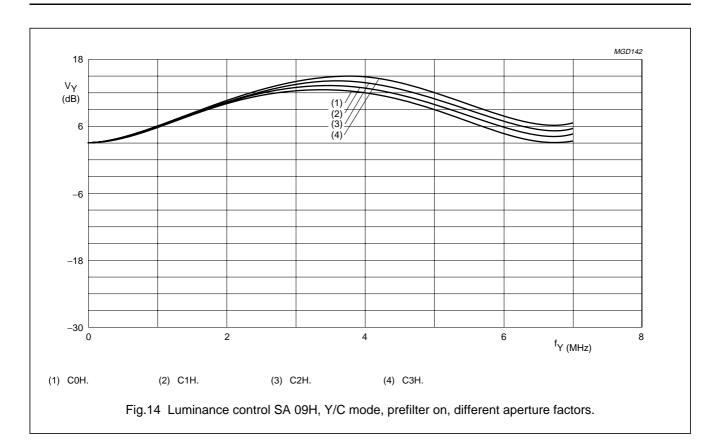

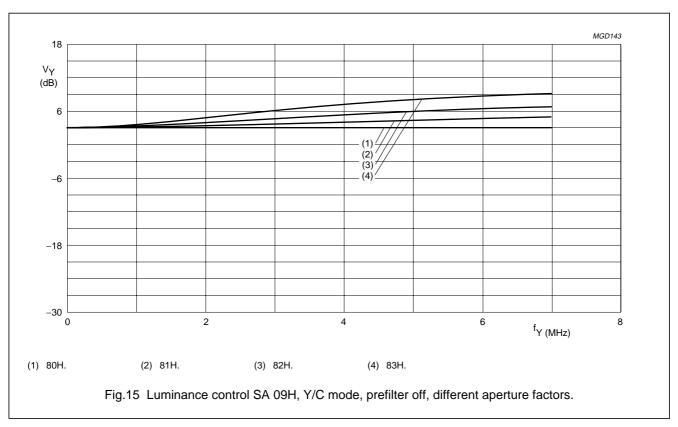

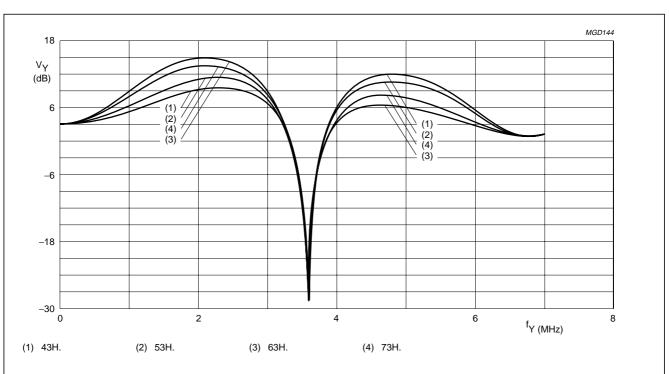

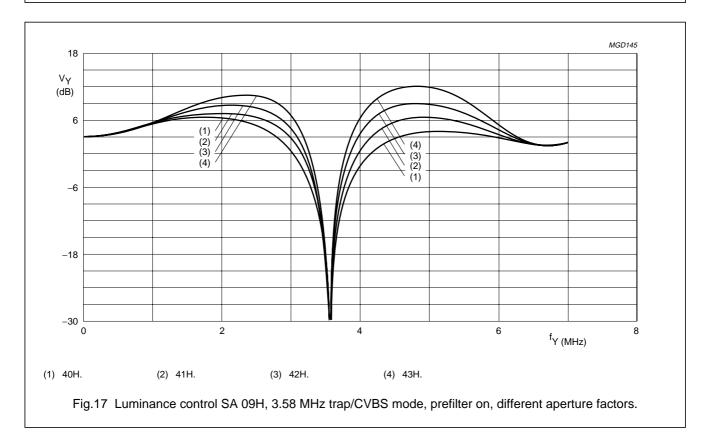

The high frequency components of the luminance signal can be peaked (control for sharpness improvement via I<sup>2</sup>C-bus subaddress 09H, see Table 36) in two band-pass filters with selectable transfer characteristic. This signal is then added to the original (unpeaked) signal. For the resulting frequency characteristics see Figs 11 to 18. A switchable amplifier achieves common DC amplification, because the DC gains are different in both chrominance trap modes. The improved luminance signal is fed to the BCS control located in the chrominance processing block, see Fig.19.

frequencies.

# SAA7113H

Fig.13 Luminance control SA 09H, 4.43 MHz trap/CVBS mode, prefilter off, different aperture band-pass centre frequencies.

# SAA7113H

# SAA7113H

Fig.16 Luminance control SA 09H, 3.58 MHz trap/CVBS mode, prefilter on, different aperture band-pass centre frequencies.

# SAA7113H

Philips Semiconductors

Product specification

# 9-bit video input processor

**SAA7113H**

1999 Jul 01

21

# SAA7113H

### 8.5 Synchronization

The prefiltered luminance signal is fed to the synchronization stage. Its bandwidth is further reduced to 1 MHz in a low-pass filter. The sync pulses are sliced and fed to the phase detectors where they are compared with the sub-divided clock frequency. The resulting output signal is applied to the loop filter to accumulate all phase deviations. Internal signals (e.g. HCL and HSY) are generated in accordance with analog front-end requirements. The loop filter signal drives an oscillator to generate the line frequency control signal LFCO, see Fig.19.

The detection of 'pseudo syncs' as part of the macrovision copy protection standard is also done within the synchronization circuit.

The result is reported as flag COPRO within the decoder status byte at subaddress 1FH.

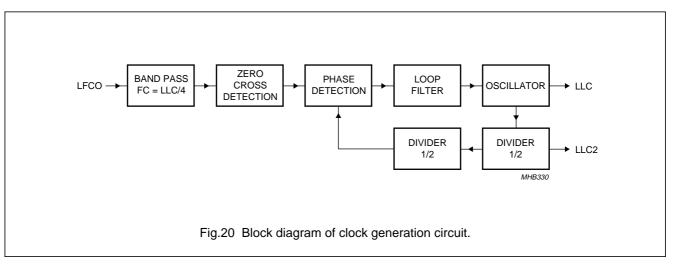

### 8.6 Clock generation circuit

The internal CGC generates all clock signals required for the video input processor. The internal signal LFCO is a digital-to-analog converted signal provided by the horizontal PLL. It is the multiple of the line frequency [6.75 MHz =  $429 \times f_H$  (50 Hz) or  $432 \times f_H$  (60 Hz)].

Internally the LFCO signal is multiplied by a factor of 2 and 4 in the PLL circuit (including phase detector, loop filtering, VCO and frequency divider) to obtain the output clock signals. The rectangular output clocks have a 50% duty factor.

| Table 1 | Clock frequencies |

|---------|-------------------|

|---------|-------------------|

| CLOCK           | FREQUENCY (MHz) |

|-----------------|-----------------|

| XTAL            | 24.576          |

| LLC             | 27              |

| LLC2 (internal) | 13.5            |

| LLC4 (internal) | 6.75            |

| LLC8 (virtual)  | 3.375           |

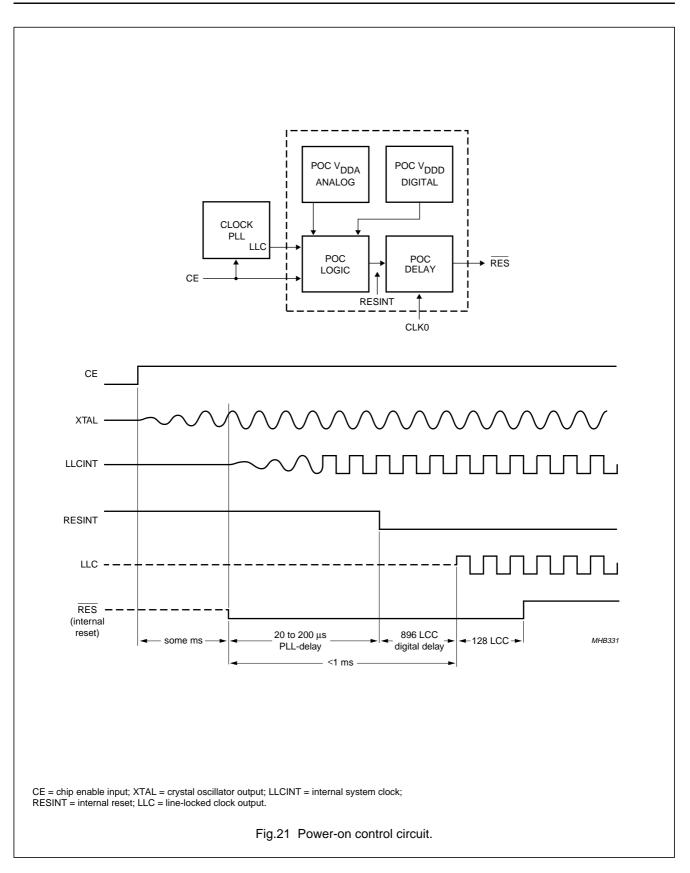

### 8.7 Power-on reset and CE input

A missing clock, insufficient digital or analog  $V_{DDA0}$  supply voltages (below 2.8 V) will initiate the reset sequence; all outputs are forced to 3-state (see Fig.21).

It is possible to force a reset by pulling the Chip Enable (CE) to ground. After the rising edge of CE and sufficient power supply voltage, the outputs LLC and SDA return from 3-state to active, while RTS0, RTS1 and RTCO remain in 3-state and have to be activated via I<sup>2</sup>C-bus programming (see Table 2).

# SAA7113H

SAA7113H

| INTERNAL POWER-ON<br>CONTROL SEQUENCE      | PIN OUTPUT STATUS                                                                                   | REMARKS                                                                                  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Directly after power-on asynchronous reset | VPO7 to VPO0, RTCO, RTS0, RTS1, SDA and LLC are in high-impedance state                             | direct switching to high-impedance for 20 to 200 ms                                      |

| Synchronous reset sequence                 | LLC and SDA become active;<br>VPO7 to VPO0, RTCO, RTS0 and RTS1<br>are held in high-impedance state | internal reset sequence                                                                  |

| Status after power-on control sequence     | VPO7 to VPO0, RTCO, RTS0 and RTS1 are held in high-impedance state                                  | after power-on (reset sequence) a complete I <sup>2</sup> C-bus transmission is required |

### Table 2 Power-on control sequence

### 8.8 Multi-standard VBI data slicer

The multi-standard data slicer is a Vertical Blanking Interval (VBI) and Full Field (FF) video data acquisition block. In combination with software modules the slicer acquires most existing formats of broadcast VBI and FF data.

The implementation and programming model of the multi-standard VBI data slicer is similar to the text slicer built in the *"Multimedia Video Data Acquisition Circuit SAA5284"*.

The circuitry recovers the actual clock phase during the clock-run-in-period, slices the data bits with the selected data rate, and groups them into bytes. The clock frequency, signals source, field frequency and accepted error count must be defined via the I<sup>2</sup>C-bus in subaddress 40H, AC1: bits D7 to D4.

Several standards can be selected per VBI line. The supported VBI data standards are described in Table 3.

The programming of the desired standards is done via I<sup>2</sup>C-bus subaddresses 41H to 57H (LCR2[7 : 0] to LCR24[7 : 0]); see detailed description in Chapter 8.10. To adjust the slicers processing to the signals source, there are offsets in horizontal and vertical direction available via the I<sup>2</sup>C-bus in subaddresses 5BH (bits 2 to 0), 59H (HOFF10 to HOFF0) and 5BH (bit 4), 5AH (VOFF8 to VOFF0). The formatting of the decoded VBI data is done within the output interface to the VPO-bus. For a detailed description of the sliced data format see Table 17.

| STANDARD TYPE                   | DATA RATE<br>(Mbits/s) | FRAMING CODE       | FC<br>WINDOW | HAM<br>CHECK |

|---------------------------------|------------------------|--------------------|--------------|--------------|

| Teletext EuroWST, CCST          | 6.9375                 | 27H                | WST625       | always       |

| European closed caption         | 0.500                  | 001                | CC625        |              |

| VPS                             | 5                      | 9951H              | VPS          |              |

| Wide screen signalling bits     | 5                      | 1E3C1FH            | WSS          |              |

| US teletext (WST)               | 5.7272                 | 27H                | WST525       | always       |

| US closed caption (line 21)     | 0.503                  | 001                | CC525        |              |

| Teletext                        | 6.9375                 | programmable       | general text | optional     |

| VITC/EBU time codes (Europe)    | 1.8125                 | programmable       | VITC625      |              |

| VITC/SMPTE time codes (USA)     | 1.7898                 | programmable       | VITC625      |              |

| US NABTS                        | 5.7272                 | programmable       | NABTS        | optional     |

| MOJI (Japanese)                 | 5.7272                 | programmable (A7H) | Japtext      |              |

| Japanese format switch (L20/22) | 5                      | programmable       |              |              |

### Table 3 Supported VBI standards

SAA7113H

### 8.9 VBI-raw data bypass

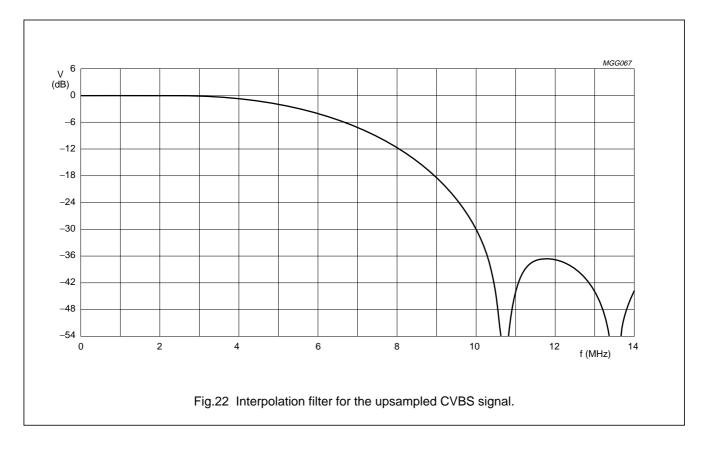

For a 27 MHz VBI-raw data bypass the digitized CVBS signal is upsampled after AD-conversion. Suppressing of the back folded CVBS frequency components after upsampling is achieved by an interpolation filter; see Fig.22.

SAA7113H

### 8.10 Digital output port VPO7 to VPO0

The 8-bit VPO-bus can carry 16 data types in three different formats, selectable by the control registers LCR2 to LCR24 (see also Chapter 15, subaddresses 41H to 57H).

| DATA TYPE<br>NUMBER | DATA<br>FORMAT | DATA TYPE                                   | NAME         | NUMBER OF VALID<br>BYTES SENT PER<br>LINE |

|---------------------|----------------|---------------------------------------------|--------------|-------------------------------------------|

| 0                   | sliced         | teletext EuroWST, CCST                      | WST625       | 88                                        |

| 1                   | sliced         | European closed caption                     | CC625        | 8                                         |

| 2                   | sliced         | VPS                                         | VPS          | 56                                        |

| 3                   | sliced         | Wide screen signalling bits                 | WSS          | 32                                        |

| 4                   | sliced         | US teletext (WST)                           | WST525       | 72                                        |

| 5                   | sliced         | US closed caption (line 21)                 | CC525        | 8                                         |

| 6                   | YUV 4 : 2 : 2  | video component signal, VBI region          | test line    | 1440                                      |

| 7                   | raw            | oversampled CVBS data                       | intercast    | programmable                              |

| 8                   | sliced         | teletext                                    | general text | 88                                        |

| 9                   | sliced         | VITC/EBU time codes (Europe)                | VITC625      | 26                                        |

| 10                  | sliced         | VITC/SMPTE time codes (USA)                 | VITC625      | 26                                        |

| 11                  | reserved       | reserved                                    | -            | _                                         |

| 12                  | sliced         | US NABTS                                    | NABTS        | 72                                        |

| 13                  | sliced         | MOJI (Japanese)                             | Japtext      | 74                                        |

| 14                  | sliced         | Japanese format switch (L20/22)             | JFS          | 56                                        |

| 15                  | YUV 4 : 2 : 2  | video component signal, active video region | active video | 1440                                      |

Table 4

VPO-bus data formats and types

### Note

1. The number of valid bytes per line can be less for the sliced data format if standard not recognized (wrong standard or poor input signal).

For each LCR value from 2 to 23 the data type can be programmed individually. LCR2 to LCR23 refer to line numbers. The selection in LCR24 values is valid for the rest of the corresponding field. The upper nibble contains the value for field 1 (odd), the lower nibble for field 2 (even). The relationship between LCR values and line numbers can be adjusted via VOFF8 to VOFF0 (located in subaddresses 5BH, bit 4 and 5AH, bits 7 to 0). The recommended values are 07H for 50 Hz sources and 0AH for 60 Hz sources, to accommodate line number conventions as used for PAL, SECAM and NTSC standards; see Tables 8 to 11.

Some details about data types:

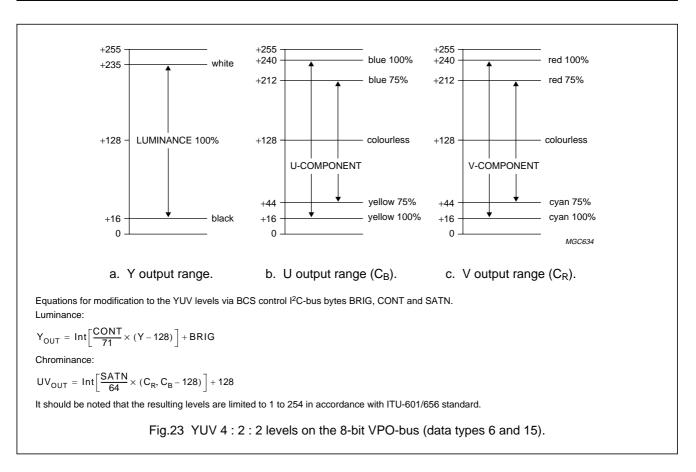

- Active video (data type 15) component YUV 4 : 2 : 2 signal, 720 active pixels per line. Format and nominal levels are given in Fig.23 and Table 13.

- **Test line** (data type 6), is similar to decoded YUV-data as in active video, with two exceptions:

- vertical filter (chrominance comb filter for NTSC standards, PAL-phase-error correction) within the chrominance processing is disabled

- peaking and chrominance trap are bypassed within the luminance processing, if I<sup>2</sup>C-bus bit VBLB is set. This data type is defined for future enhancements; it could be activated for lines containing standard test signals within the vertical blanking period; currently the most sources do not contain test lines.

This data type is available only in lines with VREF = 0, see  $I^2C$ -bus detail section, Table 45. Format and nominal levels are given in Fig.23 and Table 13.

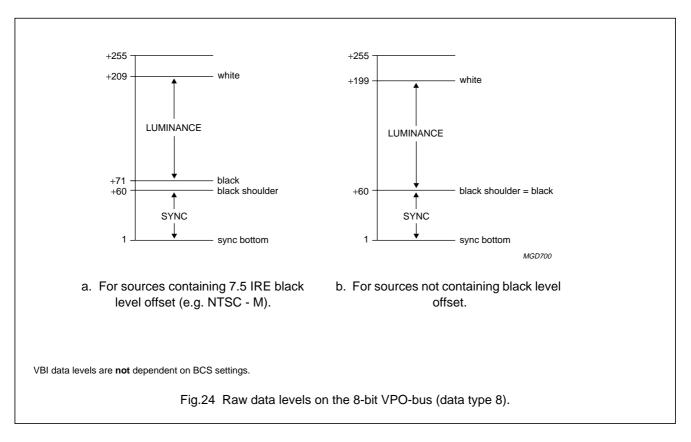

Raw samples (data type 7) oversampled CVBS-signal for intercast applications; the data rate is 27 MHz. The horizontal range is programmable via HSB7 to HSB0, HSS7 to HSS0 and HDEL1 to HDEL0; see I<sup>2</sup>C-bus section subaddresses 06H, 07H and 10H and Tables 33, 34 and 46.

Format and nominal levels are given in Fig.24 and Table 15.

• **Sliced data** (various standards, data types 0 to 5 and 8 to 14).

The format is given in Table 17.

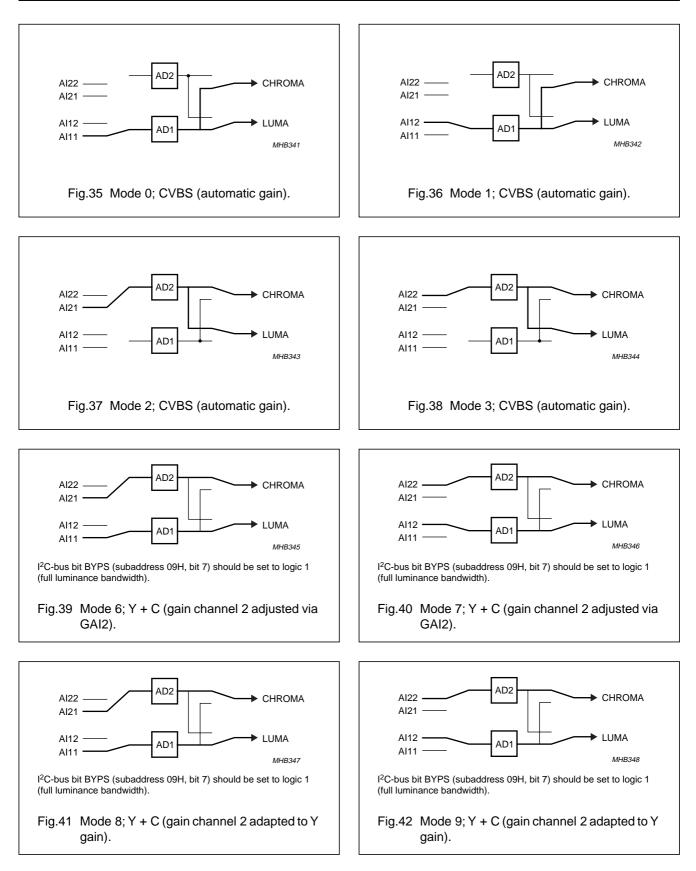

The data type selections by LCR are overruled by setting VIPB (subaddress 11H bit 1) to logic 1. This setting is mainly intended for device production tests. The VPO-bus carries the upper or lower 8 bits of the two ADCs depending on the ADLSB (subaddress 13H bit 7) setting. The output configuration is done via MODE3 to MODE0 settings (subaddress 02H bits 3 to 0, see Table 27). If the YC-mode is selected, the VPO-bus carries the multiplexed output signals of both ADCs, in CVBS-mode the output of only one ADC. No timing reference codes are generated in this mode.

**Note**: The LSBs (bit 0) of the ADCs are available on pins RTS0 or RTS1. See Chapter 15, subaddress 12H for details.

The SAV/EAV timing reference codes define start and end of valid data regions.

| Table 5 | SAV/EAV format |

|---------|----------------|

|---------|----------------|

| B | IT 7 | BIT 6 (F)                                                                                        | BIT 5 (V)                                                                                                 | BIT 4 (H)                     | BIT 3<br>(P3) | BIT 2<br>(P2)                |          | BIT 0<br>(P0) |

|---|------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------|---------------|------------------------------|----------|---------------|

|   | 1    | field bit<br>1st field: F = 0;<br>2nd field: F = 1;<br>for vertical timing<br>see Tables 6 and 7 | vertical blanking bit<br>VBI: V = 1;<br>active video: V = 0;<br>for vertical timing<br>see Tables 6 and 7 | H = 0 in SAV;<br>H = 1 in EAV | recom         | ed; eva<br>mendeo<br>cording | d (prote | ction         |

The generation of the H-bit and consequently the timing of SAV/EAV corresponds to the selected data format. H = 0 during active data region. For all data formats excluding data type 7 (raw data), the length of the active data region is 1440 LLC. For the YUV 4 : 2 : 2 formats (data types 15 and 6) every clock cycle within this range contains valid data, see Table 13.

The sliced data stream (various standards, data types 0 to 5 and 8 to 14; see Table 17) contains also invalid cycles marked as 00H.

The length of the raw data region (data type 7) is programmable via HSB7 to HSB0 and HSS7 to HSS0 (subaddresses 06H and 07H; see Fig.24).

During horizontal blanking period between EAV and SAV the ITU-blanking code sequence '-80-10-80-10-...' is transmitted.

The position of the F-bit is constant according to ITU 656 (see Tables 6 and 7).

The V-bit can be generated in four different ways (see Tables 6 and 7) controlled via OFTS1 and OFTS0 (subaddress 10H, bits 7 and 6), VRLN (subaddress 10H, bit 3) and LCR2 to LCR24 (subaddresses 41H to 57H).

F and V bits change synchronously with the EAV code.

# SAA7113H

|             |                |                         |          |                   | V                                                   |

|-------------|----------------|-------------------------|----------|-------------------|-----------------------------------------------------|

| LINE NUMBER | F<br>(ITU 656) | OFTS1 = 0;<br>OFTS0 = 0 |          | 61 = 0;<br>60 = 1 | OFTS1 = 1; OFTS0 = 0                                |

|             |                | (ITU 656)               | VRLN = 0 | VRLN = 1          |                                                     |

| 1 to 3      | 1              | 1                       | 1        | 1                 | according to selected data type via                 |

| 4 to 19     | 0              | 1                       | 1        | 1                 | LCR2 to LCR24 (subaddresses 41H to 57H):            |

| 20          | 0              | 0                       | 1        | 1                 | data types 0 to 14: $V = 1$ ; data type 15: $V = 0$ |

| 21          | 0              | 0                       | 1        | 0                 |                                                     |

| 22 to 261   | 0              | 0                       | 0        | 0                 |                                                     |

| 262         | 0              | 0                       | 1        | 0                 |                                                     |

| 263         | 0              | 0                       | 1        | 1                 |                                                     |

| 264 and 265 | 0              | 1                       | 1        | 1                 |                                                     |

| 266 to 282  | 1              | 1                       | 1        | 1                 |                                                     |

| 283         | 1              | 0                       | 1        | 1                 |                                                     |

| 284         | 1              | 0                       | 1        | 0                 |                                                     |

| 285 to 524  | 1              | 0                       | 0        | 0                 |                                                     |

| 525         | 1              | 0                       | 1        | 0                 |                                                     |

Table 6 525 lines/60 Hz vertical timing

Table 7 625 lines/50 Hz vertical timing

|             |                |                         |              |                   | V                                                   |

|-------------|----------------|-------------------------|--------------|-------------------|-----------------------------------------------------|

| LINE NUMBER | F<br>(ITU 656) | OFTS1 = 0;<br>OFTS0 = 0 | OFTS<br>OFTS | 51 = 0;<br>50 = 1 | OFTS1 = 1; OFTS0 = 0                                |

|             |                | (ITU 656)               | VRLN = 0     | VRLN = 1          |                                                     |

| 1 to 22     | 0              | 1                       | 1            | 1                 | according to selected data type via                 |

| 23          | 0              | 0                       | 1            | 0                 | LCR2 to LCR24 (subaddresses 41H to 57H):            |

| 24 to 309   | 0              | 0                       | 0            | 0                 | data types 0 to 14: $V = 1$ ; data type 15: $V = 0$ |

| 310         | 0              | 0                       | 1            | 0                 |                                                     |

| 311 and 312 | 0              | 1                       | 1            | 1                 |                                                     |

| 313 to 335  | 1              | 1                       | 1            | 1                 |                                                     |

| 336         | 1              | 0                       | 1            | 0                 |                                                     |

| 337 to 622  | 1              | 0                       | 0            | 0                 |                                                     |

| 623         | 1              | 0                       | 1            | 0                 |                                                     |

| 624 and 625 | 1              | 1                       | 1            | 1                 |                                                     |

## Table 8 Relationship of LCR to line numbers in 525 lines/60 Hz systems (part 1)

| Line number                                                     | 519   | 520     | 521 | 522 | 523 | 524 | 525 | 5    | 1         | 2         | 3   |      | 4         | 5        | 6   |     | 7         | 8        | 9    |

|-----------------------------------------------------------------|-------|---------|-----|-----|-----|-----|-----|------|-----------|-----------|-----|------|-----------|----------|-----|-----|-----------|----------|------|

| (1st field)                                                     | activ | e video |     |     | •   |     |     | (    | equaliz   | ation pul | ses |      | serratio  | n pulses | 5   |     | equaliz   | ation pu | lses |

| _ine number                                                     | 257   | 258     | 259 | 260 | 261 | 262 | 263 | 3 2  | 264       | 265       | 266 | 5    | 267       | 268      | 269 | )   | 270       | 271      | 272  |

| 2nd field)                                                      | activ | e video |     | •   | •   |     |     | equa | alizatior | pulses    |     | seri | ration pu | ilses    |     | equ | alizatior | n pulses |      |

| _CR<br>/VOFF = 00AH;<br>HOFF = 354H;<br>FOFF = 1;<br>FISET = 1) | 24    |         |     |     |     |     |     |      |           | 2         | 3   |      | 4         | 5        | 6   |     | 7         | 8        | 9    |

Table 9

Relationship of LCR to line numbers in 525 lines/60 Hz systems (part 2)

| VERTICAL LINE OFFSET                                      | VOFF8  | TO VOF    | F0 = 00 | AH; HOF | RIZONTA | AL PIXE |     | ET HOFF | 10 TO H | IOFF0 = | 354H, F | OFF = 1 | , FISET  | = 1   |

|-----------------------------------------------------------|--------|-----------|---------|---------|---------|---------|-----|---------|---------|---------|---------|---------|----------|-------|

| Line number (1st field)                                   | 10     | 11        | 12      | 13      | 14      | 15      | 16  | 17      | 18      | 19      | 20      | 21      | 22       | 23    |

|                                                           | nomina | l VBI-lin | es F1   |         |         |         |     |         |         |         |         |         | active v | video |

| Line number (2nd field)                                   | 273    | 274       | 275     | 276     | 277     | 278     | 279 | 280     | 281     | 282     | 283     | 284     | 285      | 286   |

|                                                           | nomina | l VBI-lin | es F2   | -       |         |         |     |         |         |         |         |         | active v | video |

| LCR (VOFF = 00AH;<br>HOFF = 354H; FOFF = 1;<br>FISET = 1) | 10     | 11        | 12      | 13      | 14      | 15      | 16  | 17      | 18      | 19      | 20      | 21      | 22       | 23    |

Table 10

Relationship of LCR to line numbers in 625 lines/50 Hz systems (part 1)

| VERTICAL LINE OFFSET VOFF8 TO VOFF0 = 007H; HOF     | RIZONTA  |       | L OF | FSE   | T HOFF    | 10 TO F | IOFF0 =   | 354H, F  | OFF = | 1, FISET     | = 0      |

|-----------------------------------------------------|----------|-------|------|-------|-----------|---------|-----------|----------|-------|--------------|----------|

| Line number (1st field)                             | 621      | 622   | 623  |       | 624       | 625     | 1         | 2        | 3     | 4            | 5        |

|                                                     | active v | /ideo |      | equ   | alizatior | pulses  | serratio  | n pulses | s e   | equalization | n pulses |

| Line number (2nd field)                             | 309      | 310   | 311  |       | 312       | 313     | 314       | 315      | 316   | 317          | 318      |

|                                                     | active v | /ideo | equ  | aliza | ation pul | ses sei | ration pu | Ilses    | equa  | lization pu  | lses     |

| LCR (VOFF = 007H; HOFF = 354H; FOFF = 1; FISET = 0) | 24       |       |      |       |           |         |           | 2        | 3     | 4            | 5        |

# 9-bit video input processor

SAA7113H

Product specification

\_

1999 Jul 01

Philips Semiconductors

9-bit video input processor

SAA7113H

Product specification

Table 11

Relationship of LCR to line numbers in 625 lines/50 Hz systems (part 2)

| VERTICAL                                                        | LINE | OFFS    | SET VO   | OFF8 T | O VOF | F0 = 0 | 07H; H | IORIZ | ONTAL | . PIXEI | OFF | SET HO | OFF10 | то но | )FF0 = | 354H, | FOFF | = 1, Fl | SET =           | 0   |

|-----------------------------------------------------------------|------|---------|----------|--------|-------|--------|--------|-------|-------|---------|-----|--------|-------|-------|--------|-------|------|---------|-----------------|-----|

| Line number                                                     | 6    | 7       | 8        | 9      | 10    | 11     | 12     | 13    | 14    | 15      | 16  | 17     | 18    | 19    | 20     | 21    | 22   | 23      | 24              | 25  |

| (1st field)                                                     | nomi | inal VE | BI-lines | 5 F1   |       |        |        |       |       |         |     |        |       | •     |        |       |      |         | active<br>video |     |

| Line number                                                     | 319  | 320     | 321      | 322    | 323   | 324    | 325    | 326   | 327   | 328     | 329 | 330    | 331   | 332   | 333    | 334   | 335  | 336     | 337             | 338 |

| (2nd field)                                                     | nomi | inal VE | 3I-lines | s F2   |       |        |        |       |       |         |     |        |       |       |        |       |      | active  | video           | •   |

| LCR<br>(VOFF = 007H;<br>HOFF = 354H;<br>FOFF = 1;<br>FISET = 0) | 6    | 7       | 8        | 9      | 10    | 11     | 12     | 13    | 14    | 15      | 16  | 17     | 18    | 19    | 20     | 21    | 22   | 23      | 24              |     |

Table 12 Location of related programming registers

| NAME            | SUBADDRESS, BITS              |

|-----------------|-------------------------------|

| VOFF8 to VOFF0  | 5B, D4 and 5A, D7 to D0       |

| HOFF10 to HOFF0 | 5B, D2 to D0 and 59, D7 to D0 |

| FOFF            | 5B, D7                        |

| FISET           | 40, D7                        |

1999 Jul 01

\_

# SAA7113H

### Table 13 YUV data format on the 8-bit VPO-bus (data types 6 and 15)

| ANK    | -  | TIMING<br>REFERENCE<br>CODE |    |    |     |         | 7  | 20 PI)           | ELS | S YUV            | 4:2 | 2 : 2 | DATA               |      | R  | EFE | NING<br>REN<br>DDE |     |    | ANKI<br>ERIC |  |

|--------|----|-----------------------------|----|----|-----|---------|----|------------------|-----|------------------|-----|-------|--------------------|------|----|-----|--------------------|-----|----|--------------|--|

| <br>80 | 10 | FF                          | 00 | 00 | SAV | $C_B 0$ | Y0 | C <sub>R</sub> 0 | Y1  | C <sub>B</sub> 2 | Y2  |       | C <sub>R</sub> 718 | Y719 | FF | 00  | 00                 | EAV | 80 | 10           |  |

### Table 14 Explanation to Table 13

| NAME             | EXPLANATION                                                              |

|------------------|--------------------------------------------------------------------------|

| SAV              | start of active video range; see Tables 5 to 7                           |

| C <sub>B</sub> n | U (B – Y) colour difference component, pixel number n = 0, 2, 4 to 718   |

| Yn               | Y (luminance) component, pixel number n = 0, 1, 2, 3 to 719              |

| C <sub>R</sub> n | V (R – Y) colour difference component, pixel number $n = 0, 2, 4$ to 718 |

| EAV              | end of active video range; see Tables 5 to 7                             |

# SAA7113H

### Table 15 Raw data format on the 8-bit VPO-bus (data type 8)

| <br>ANK<br>PERIC |    | R  | EFE | AING<br>REN<br>DDE | ICE |    | ov | ERS | AMP | LED | CVE | 3S S | SAMPLE | S  | R  | EFE | NING<br>REN<br>DDE |     |    | ANKI<br>ERIO |  |

|------------------|----|----|-----|--------------------|-----|----|----|-----|-----|-----|-----|------|--------|----|----|-----|--------------------|-----|----|--------------|--|

| <br>80           | 10 | FF | 00  | 00                 | SAV | Y0 | Y1 | Y2  | Y3  | Y4  | Y5  |      | Yn – 1 | Yn | FF | 00  | 00                 | EAV | 80 | 10           |  |

### Table 16 Explanation to Table 15

| NAME | EXPLANATION                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------|

| SAV  | start of raw sample range; see Tables 5 to 7                                                                                          |

| Yi   | oversampled raw sample stream (CVBS signal), $n = 0, 1, 2, 3$ to n; n is programmable via HSB and HSS; see Sections 15.2.7 and 15.2.8 |

| EAV  | end of raw sample range; see Tables 5 to 7                                                                                            |

| BLANKING<br>PERIOD |    | TIMING<br>REFERENCE CODE |    |    | INTERNAL HEADER |      |    | SLICED DATA |      |      |      | TIMING<br>REFERENCE CODE |      |      | BLANKING<br>PERIOD |    |    |     |    |    |  |

|--------------------|----|--------------------------|----|----|-----------------|------|----|-------------|------|------|------|--------------------------|------|------|--------------------|----|----|-----|----|----|--|

| <br>80             | 10 | FF                       | 00 | 00 | SAV             | SDID | DC | IDI1        | IDI2 | DLN1 | DHN1 |                          | DLNn | DHNn | FF                 | 00 | 00 | EAV | 80 | 10 |  |

### Table 18 Explanation to Table 17

| NAME | EXPLANATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SAV  | start of active data; see Tables 5 to 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| SDID | sliced data identification: NEP <sup>(1)</sup> , EP <sup>(2)</sup> , SDID5 to SDID0, freely programmable via I <sup>2</sup> C-bus subaddress 5EH, D5 to D0, e. g. to be used as source identifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| DC   | Dword count: NEP <sup>(1)</sup> , EP <sup>(2)</sup> , DC5 to DC0; DC is inserted for software compatibility reasons to SAA7112, but does not represent any relevant information for SAA7113H applications.<br>DC describes the number of succeeding 32-bit words:<br>$DC = \frac{1}{4}(C + n)$ , where $C = 2$ (the two data identification bytes IDI1 and IDI2) and $n =$ number of decoded bytes according to the chosen text standard. As the sliced data are transmitted nibble wise, the maximum number of bytes transmitted (NBT) starting at IDI1 results to:<br>NBS = (DC × 8) - 2<br>DC can vary between 1 and 11, depending on the selected data type.<br>Note that the number of bytes actually transmitted can be less than NBT for two reasons:<br>1. result of DC would result to a non-integer value (DC is always rounded up)<br>2. standard not recognized (wrong standard or poor input signal) |  |  |  |  |  |  |  |  |

| IDI1 | internal data identification 1: $OP^{(3)}$ , FID (field 1 = 0, field 2 = 1), LineNumber8 to LineNumber3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

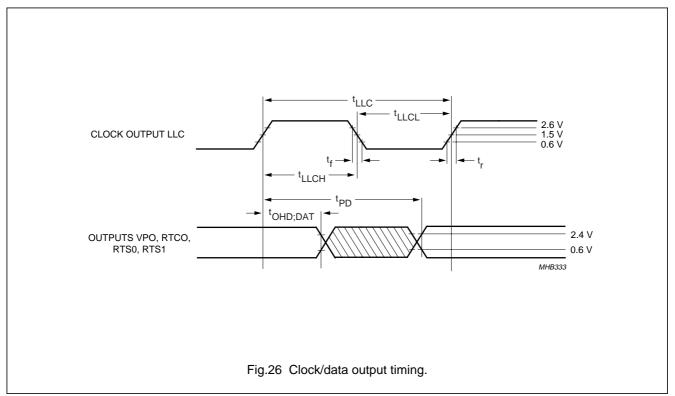

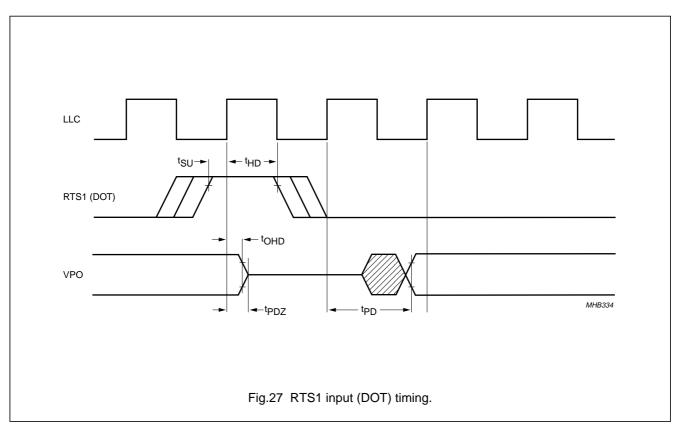

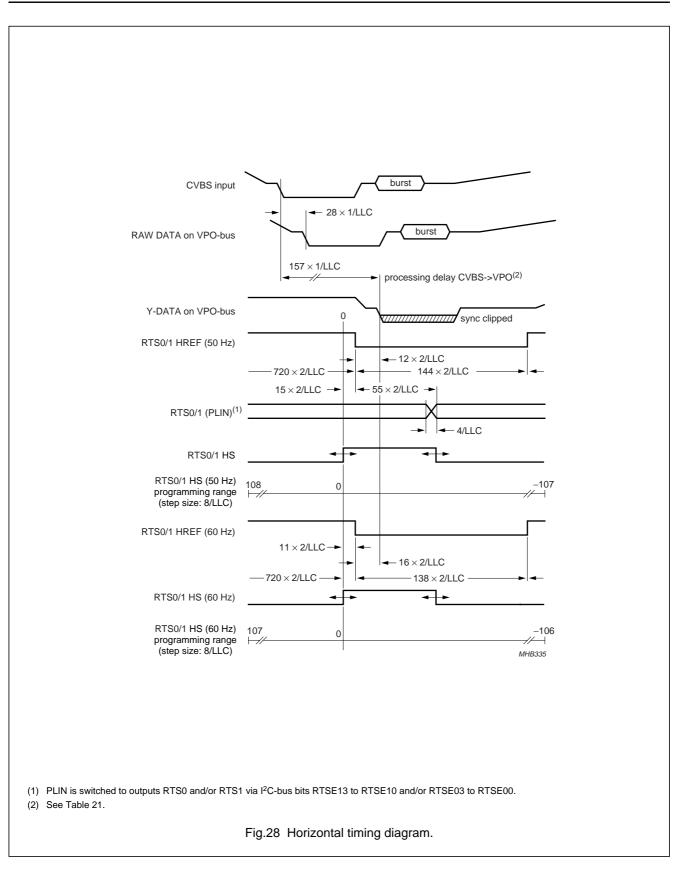

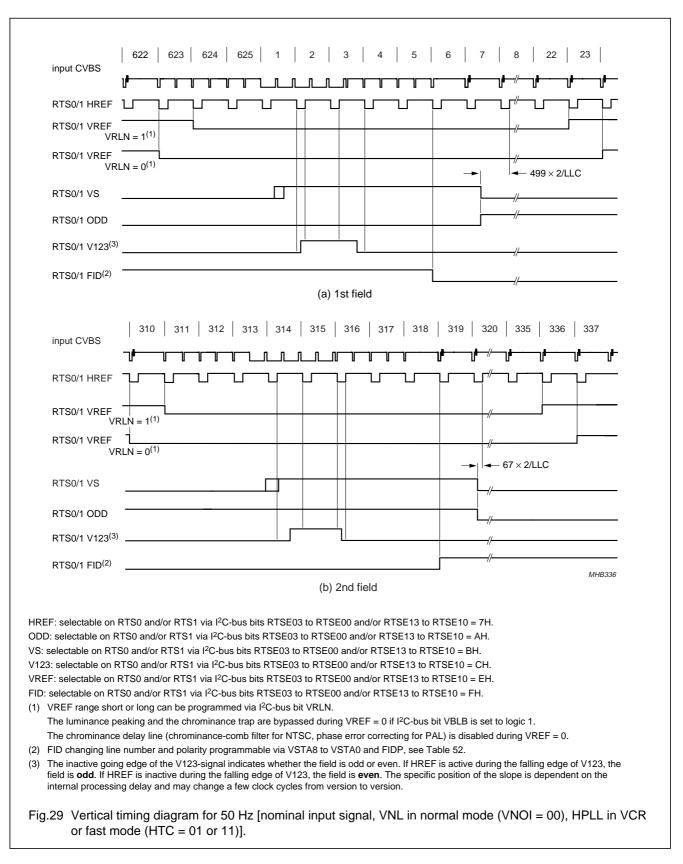

| IDI2 | internal data identification 2: OP <sup>(3)</sup> , LineNumber2 to LineNumber0, DataType3 to DataType0; see Table 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |