# signetics

## DUAL J-K EDGE-TRIGGERED FLIP-FLOP | S54H108

\$54H108-A,F,W . N74H108-A,F

## S54H108 N74H108

## DIGITAL 54/74 TTL SERIES

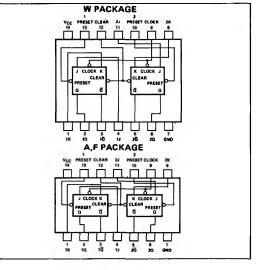

## PIN CONFIGURATIONS

## DESCRIPTION

These dual monolithic J-K flip-flops are negative-adge-triggered. They feature individual J, K, and asynchronous preset inputs to each flip-flop as well as common clock and asynchronous clear inputs. When the clock goes high, the inputs are enabled and data is accepted. Logical state of J and K inputs may be allowed to change when the clock pulse is in a high state and bistable performs according to the truth table as long as minimum set-up times are observed. Data input is transferred to the outputs on the negative edge of the clock pulse.

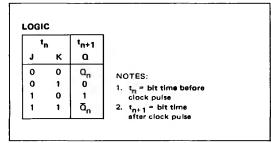

## TRUTH TABLE

## **RECOMMENDED OPERATING CONDITIONS**

|                                                                                   | MIN  | NOM | MAX  | UNIT |

|-----------------------------------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S54H108 Circuits                                 | 4.5  | 5   | 5.5  | v    |

| N74H108 Circuits                                                                  | 4.75 | 5   | 5.25 | l v  |

| Operating Free-Air Temperature Range, TA: S54H108 Circuits                        | -55  | 25  | 125  | l °c |

| N74H108 Circuits                                                                  | 0    | 25  | 70   | °C   |

| Normalized Fan-Out from each Output, N                                            |      |     | 10   |      |

| Width of Clock Pulse, to (clock)                                                  | 10   |     |      | ns   |

| Width of Clock Pulse, tp(clock)<br>Width of Preset Pulse, tp(creset)              | 15   |     |      | ns   |

| Width of Clear Pulse, to (clear)                                                  | 16   |     |      | ns   |

| Input Setup Time, teetun: Logical 1                                               | 10   |     |      | ns   |

| Logical O                                                                         | 13   |     |      | ns   |

| Input Hold Time, thous                                                            | 0    |     |      | ns   |

| Input Hold Time, t <sub>hold</sub><br>Clock Pulse Transition Lime, t <sub>O</sub> |      |     | 150  | ns   |

## ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER           |                                        | TEST CONDITIONS +      |                            |     | TYP <sup>†</sup> | MAX  |     |

|---------------------|----------------------------------------|------------------------|----------------------------|-----|------------------|------|-----|

|                     | Input voltage required to ensure       |                        |                            | 2   |                  |      | v   |

| V <sub>in(1)</sub>  | logical 1 at any input terminal        |                        |                            | 2   |                  |      | ľ   |

| v                   | Input voltage required to ensure       |                        |                            | ĺ   |                  | 0.8  | ĺv  |

| V <sub>in(0)</sub>  | logical O at any input terminal        |                        |                            |     |                  | 0.8  | *   |

| V <sub>out(1)</sub> | Logical 1 Output voltage               | V <sub>CC</sub> - MIN, | l <sub>ioad</sub> = -500µA | 2.4 | 3.2              |      | v   |

| V <sub>out(0)</sub> | Logical O output voltage               | V <sub>CC</sub> = MIN, | I <sub>sink</sub> = 20mA   |     | 0.25             | 0.4  | v v |

| •                   | Logical O level input current at       | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 0.4∨     |     | -1               | -2   | mA  |

| <sup>1</sup> in(0)  | in (0) J,K, or preset                  | VCC - MAA,             | v <sub>in</sub> = 0.4V     |     | -1               | -2   |     |

| lin(0)              | Logical O level input current at clock | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 0.4V     |     | -6               | -9.6 | mA  |

| lin(0)              | Logical O level input current at clear | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 0.4V     |     | -2               | -4   | mA  |

|                     | Logical 1 level input current at       | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V     |     |                  | 50   | μΑ  |

| lin(1)              | J or K                                 | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 5.5V     |     |                  | 1    | mA  |

| 1                   | Logical 1 level input current at       | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V     | 0   |                  | -1   | mA  |

| lin(1)              | clock                                  | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 5.5V     |     |                  | 1    | mA  |

## ELECTRICAL CHARACTERISTICS (Cont'd)

| PARAMETER          |                                  | TEST CONDITIONS        |                          | MIN T | YP MAX | UNIT |

|--------------------|----------------------------------|------------------------|--------------------------|-------|--------|------|

| 1                  | Logical 1 level input current at | V <sub>CC</sub> - MAX, | V <sub>in</sub> = 2.4V   |       | 100    | μA   |

| lin(1)             | preset                           | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 6.6V · |       | 1      | mA   |

| 1                  | Logical 1 level input current at | V <sub>CC</sub> - МАХ, | V <sub>in</sub> = 2.4∨   |       | 200    | μΑ   |

| <sup>1</sup> in(1) | clear                            | V <sub>CC</sub> = мах, | V <sub>in</sub> = 5.6V   |       | 1      | mA   |

| los                | Short-circuit output current **  | V <sub>CC</sub> = MAX, | V <sub>in</sub> = 0      | -40   | -100   | mA   |

| <sup>I</sup> cc    | Supply current                   | V <sub>CC</sub> = MAX  |                          |       | 40 76  | mA   |

## SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

| PARAMETER         |                                                                                                                    | TEST CONDITIONS        |                       | MIN | түр | MAX | UNIT |

|-------------------|--------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| fclock            | Maximum input clock frequency                                                                                      | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω | 40  | 50  |     | MHz  |

| <sup>t</sup> pd1  | Propagation delay time to logical 1<br>level from preset or clear to output<br>Propagation delay time to logical 0 | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω |     | 8   | 12  | ns   |

| t <sub>pd</sub> 0 | level from preset or clear to output<br>(clock low)                                                                | С <sub>L</sub> = 25рF, | R <sub>L</sub> = 280Ω |     | 23  | 35  | ns   |

| <sup>t</sup> pd0  | Propagation delay time to logical O<br>level from preset or clear to<br>output (clock high)                        | С <sub>L</sub> = 25рF, | R <sub>L</sub> = 280Ω |     | 15  | 20  | ns   |

| t <sub>pd1</sub>  | Propagation delay time to logical 1<br>level from clock to output                                                  | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω | 5   | 10  | 15  | ns   |

| <sup>t</sup> pd0  | Propagation delay time to logical O<br>level from clock to output                                                  | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω | 8   | 16  | 20  | ns   |

\* For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

\* Not more than one output should be shorted at a time, and duration of short-circuit test should not exceed 1 second. † All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

## DIGITAL 54/74 TTL SERIES

## DESCRIPTION

Series 54S/74S Schottky TTL circuits are implemented with full Schottky-barrier-diode clamping to achieve ultra-high speeds previously obtainable only with emitter-coupled logic, yet they retain the desirable features of, and are completely compatible with, most of the popular saturated logic circuits. Schottky TTL circuits currently offer the best speed-power product of any high-speed logic family.

Schottky-barrier-diode clamping prevents transistors from achieving classic saturation and thereby effectively eliminates excess charge storage and subsequent recovery times. These recovery times contribute significantly to overall propagation delays experienced with saturated digital-logic circuits.

Series 54S/74S circuits are completely compatible with the Series 54/74, Series 54H/74H, and Series 54L/74L TTL logic families. Ease of use and compatibility with other TTL families result in flexibility of choice within the four speed-power ranges offered (Series 54/74, 54H/74H, 54L/74L, 54S/74S) to achieve highly efficient system grading to specific performance requirements.

Definitive specifications are provided for operating characteristics over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C for Series 54S circuits and over the temperature range of  $0^{\circ}$ C to  $70^{\circ}$ C for Series 74S circuits.

## FEATURES

## VERY-HIGH-SPEED, LOW-POWER OPERATION

- 3-ns typical gate propagation delay time

19-mW-per-gate power dissipation at 50% duty cycle--

- speed-power product = 57pJ 125-MHz typical J-K flip-flop maximum input clock fre-

- I25-MHZ typical J-K flip-flop maximum input clock frequency (d-c coupled)

### EASE OF SYSTEM DESIGN

- fully compatible with Series 54/74, 54H/74H, and 54L/74L TTL (including MSI/LSI), and most DTL

- Schottky-diode-clamped inputs simplify system design

- terminated, controlled-impedance lines not normally required

- Iow output impedance: provides low AC noise susceptability drives highly capacitive loads

### IMPROVED CIRCUIT PERFORMANCE

- switching times virtually insensitive to power supply and/or temperature variations

- power dissipation remains relatively low at operating frequencies up to 100 MHz

- high-fan-out: 20 54S/74S loads at the high logic level 10 54S/74S loads at the low logic level

- high DC noise margin—typically 1 volt

## ABSOLUTE MAXIMUM RATINGS (over operating free-air temperature range unless otherwise noted)

| Supply Voltage V <sub>CC</sub>        | 7V             |

|---------------------------------------|----------------|

| Input Voltage                         | 5.5V           |

| Intermitter Voltage                   | 5.5V           |

| Output Voltage                        | 7V             |

| Operating Free-Air Temperature Range: |                |

| Series 54S Circuits                   | -55°C to 125°C |

| Series 74S Circuits                   | 0°C to 70°C    |

| Storage Temperature Range             | -65°C to 150°C |

NOTES:

- Voltage values, except intermitter voltage, are with respect to network ground terminal.

- This is the voltage between two emitters of a multiple-emitter transistor.

- 3. This is the maximum voltage which should be applied to any open-collector output when it is in the off state.

#### UNUSED INPUTS OF POSITIVE-AND/NAND GATES

For optimum switching times and minimum noise susceptibility, unused inputs of AND or NAND gates should be maintained at a voltage greater than 2.7V, but not to exceed the absolute maximum rating of 5.5V. This eliminates the distributed capacitance associated with the floating input emitter, bond wire, and package lead, and ensures that no degradation will occur in the propagation delay times. Some possible ways of handling input emitters are:

- a. Connect unused inputs to an independent supply voltage. Preferably, this voltage should be between 2.7V and 3.5V.

- b. Connect unused inputs to a used input if maximum fan-out of the driving output will not be exceeded. Each additional input presents a full load to the driving output at a high-level voltage but adds no loading at a low-level voltage.

- c. Connect unused inputs to  $V_{CC}$  through a 1-k $\Omega$  resistor so that if a transient which exceeds the 5.5-V maximum rating should occur, the impedance will be high enough to protect the input. One to 25 unused inputs may be connected to each 1-k $\Omega$  resistor.

### INPUT-CURRENT REQUIREMENTS

Input-current requirements reflect worst-case  $V_{CC}$  and temperature conditions. Each input of the multiple-emitter input transistors requires a maximum of 2mA out of the input at a low logic level which is defined as 1 normalized load. Each input requires current into the input at a high logic level. This current is  $50\mu A$  maximum for each emitter. Currents into the input terminals are specified as positive values.

#### FAN-OUT CAPABILITY

Fan-out (N) reflects the ability of an output to supply current to a number of normalized loads at a high logic level and to sink current ta the low logic level. At the high logic level, each standard output is capable of supplying current to drive 20 Series 54H, 74H, 54S, or 74S loads (N<sub>H</sub> = 20). Currents out of the output are specified as negative values. At the low logic level, each standard output is capable of sinking current from 10 Series 54H, 74H, 54S, or 74S loads (N<sub>L</sub> = 10).

|                                                                                  |            | SERIES 54S<br>CIRCUITS |            |           | SERIES 74S<br>CIRCUITS |            |      |

|----------------------------------------------------------------------------------|------------|------------------------|------------|-----------|------------------------|------------|------|

|                                                                                  | MIN        | NOM                    | MAX        | MIN       | NOM                    | MAX        | UNIT |

| Supply Voltage V <sub>CC</sub><br>Operating Free-Air Temperature, T <sub>A</sub> | 4.5<br>-55 | 5                      | 5.5<br>125 | 4.75<br>0 | 5                      | 5.25<br>70 | °c   |