## LP3995 Micropower 150mA CMOS Voltage Regulator with Active Shutdown

## **General Description**

The LP3995 regulator is designed to meet the requirements of portable wireless battery-powered applications and will provide an accurate output voltage with low noise and low quiescent current.

For battery powered applications the low dropout and low ground current provided by the device allows the lifetime of the battery to be maximized. The Enable(/Disable) control allows the system to further extend the battery lifetime by reducing the power consumption to virtually zero.

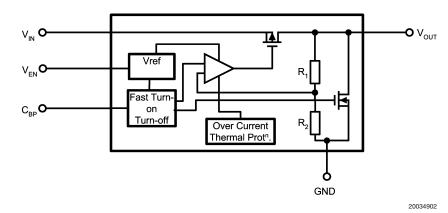

The Enable(/Disable) function on the device incorporates an active discharge circuit on the output for faster device shutdown.

The LP3995 also features internal protection against shortcircuit currents and over-temperature conditions.

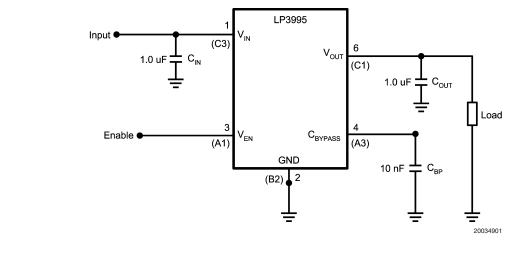

The LP3995 is designed to be stable with small 1.0  $\mu F$  ceramic capacitors. The small outline of the LP3995 micro SMD package with the required ceramic capacitors can realize a system application within minimal board area.

Performance is specified for a  $-40\,^\circ\text{C}$  to  $+125\,^\circ\text{C}$  temperature range.

The device is available in micro SMD package and LLP package. For other package options contact your local NSC sales office.

The device is available in fixed output voltages in the ranges 1.5V to less than 1.8V and 1.8V to less than 2.5Vand 2.5V to 3.3V. For availability, please contact your local NSC sales office.

## **Key Specifications**

- 2.5V to 6.0V Input Range

- Accurate Output Voltage; ±75mV

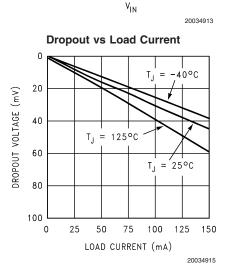

- 60 mV Typical Dropout with 150 mA Load

- Virtually Zero Quiescent Current when Disabled

- Low Output Voltage Noise

- Stable with a 1 µF Output Capacitor

- Guaranteed 150 mA Output Current

- Fast Turn-on; 30 µS (Typ.)

- Fast Turn-off; 175 µS (Typ.)

### **Features**

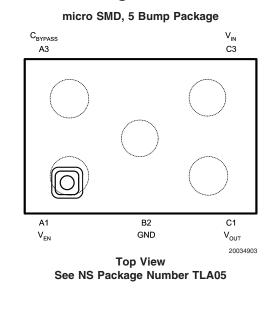

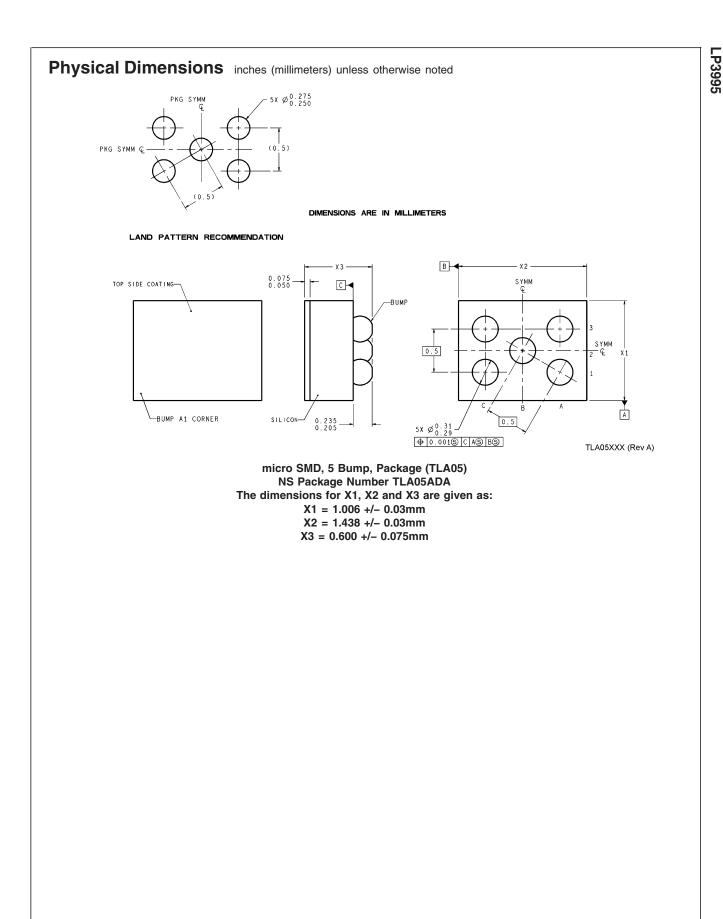

- 5 pin micro SMD Package

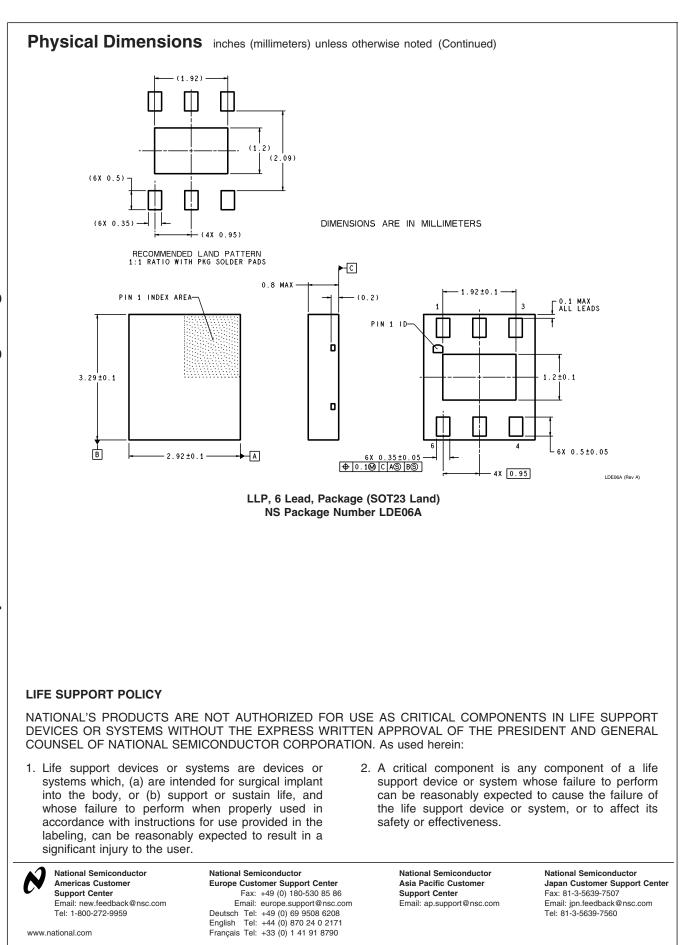

- 6 pin LLP Package

- Stable with Ceramic Capacitor

- Logic Controlled Enable

- Fast Turn-on

- Active Disable for Fast Turn-off.

- Thermal-overload and Short-circuit Protection

- -40 to +125°C Junction Temperature Range for Operation

## Applications

- GSM Portable Phones

- CDMA Cellular Handsets

- Wideband CDMA Cellular Handsets

- Bluetooth Devices

- Portable Information Appliances

May 2003

## **Block Diagram**

## **Pin Description**

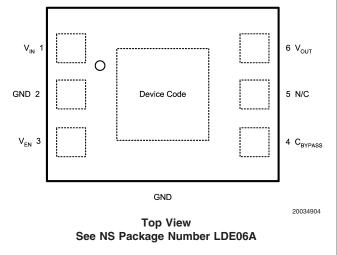

## 5 pin micro SMD and LLP - 6

| Pin                                                            | No. | Name and Function                                                             |                                                          |

|----------------------------------------------------------------|-----|-------------------------------------------------------------------------------|----------------------------------------------------------|

| micro<br>SMD                                                   | LLP |                                                                               |                                                          |

| A1                                                             | 3   | V <sub>EN</sub>                                                               | Enable Input; Disables the Regulator when $\leq 0.4$ V.  |

|                                                                |     |                                                                               | Enables the regulator when $\ge 0.9V$                    |

| B2                                                             | 2   | GND                                                                           | Common Ground                                            |

| C1                                                             | 6   | V <sub>OUT</sub>                                                              | Voltage output. Connect this output to the load circuit. |

| C3                                                             | 1   | V <sub>IN</sub>                                                               | Voltage Supply Input                                     |

| A3                                                             | 4   | C <sub>BYPASS</sub>                                                           | Bypass Capacitor connection.                             |

|                                                                |     |                                                                               | Connect a 0.01 µF capacitor for noise reduction.         |

| 5 N/C No internal connection. There should not be any board co |     | No internal connection. There should not be any board connection to this pin. |                                                          |

|                                                                | Pad | GND                                                                           | Ground connection.                                       |

|                                                                |     |                                                                               | Connect to ground plane for best thermal conduction.     |

## **Connection Diagrams**

## **Ordering Information**

#### For micro SMD Package

| Output Voltage<br>(V) | Grade | LP3995 Supplied as 250<br>Units, Tape and Reel | LP3995 Supplied as 3000 Units, Tape and | Package<br>Marking |

|-----------------------|-------|------------------------------------------------|-----------------------------------------|--------------------|

|                       |       |                                                | Reel                                    |                    |

| 1.5 (Note 1)          | STD   | LP3995ITL-1.5                                  | LP3995ITLX-1.5                          |                    |

| 1.6 (Note 1)          | STD   | LP3995ITL-1.6                                  | LP3995ITLX-1.6                          |                    |

| 1.8                   | STD   | LP3995ITL-1.8                                  | LP3995ITLX-1.8                          |                    |

| 1.9                   | STD   | LP3995ITL-1.9                                  | LP3995ITLX-1.9                          |                    |

| 2.1 (Note 1)          | STD   | LP3995ITL-2.1                                  | LP3995ITLX-2.1                          |                    |

| 2.5                   | STD   | LP3995ITL-2.5                                  | LP3995ITLX-2.5                          |                    |

| 2.8                   | STD   | LP3995ITL-2.8                                  | LP3995ITLX-2.8                          |                    |

| 3.0 (Note 2)          | STD   | LP3995ITL-3.0                                  | LP3995ITLX-3.0                          |                    |

#### For micro SMD Package unleaded

| Output Voltage<br>(V) | Grade | LP3995 Supplied as 250<br>Units, Tape and Reel | LP3995 Supplied as<br>3000 Units, Tape and<br>Reel | Package<br>Marking |

|-----------------------|-------|------------------------------------------------|----------------------------------------------------|--------------------|

| 1.5 (Note 2)          | STD   | LP3995ITL-1.5                                  | LP3995ITLX-1.5                                     |                    |

| 1.6 (Note 2)          | STD   | LP3995ITL-1.6                                  | LP3995ITLX-1.6                                     |                    |

| 1.8 (Note 2)          | STD   | LP3995ITL-1.8                                  | LP3995ITLX-1.8                                     |                    |

| 1.9 (Note 2)          | STD   | LP3995ITL-1.9                                  | LP3995ITLX-1.9                                     |                    |

| 2.1 (Note 2)          | STD   | LP3995ITL-2.1                                  | LP3995ITLX-2.1                                     |                    |

| 2.5 (Note 2)          | STD   | LP3995ITL-2.5                                  | LP3995ITLX-2.5                                     |                    |

| 2.8 (Note 2)          | STD   | LP3995ITL-2.8                                  | LP3995ITLX-2.8                                     |                    |

| 3.0 (Note 2)          | STD   | LP3995ITL-3.0                                  | LP3995ITLX-3.0                                     |                    |

#### For LLP- 6 Package

| Output Voltage<br>(V) | Grade | LP3995 Supplied as 1000<br>Units, Tape and Reel | LP3995 Supplied as<br>4500 Units, Tape and<br>Reel | Package<br>Marking |

|-----------------------|-------|-------------------------------------------------|----------------------------------------------------|--------------------|

| 1.5                   | STD   | LP3995ILD-1.5                                   | LP3995ILDX-1.5                                     | LO20B              |

| 1.6 (Note 2)          | STD   | LP3995ILD-1.6                                   | LP3995ILDX-1.6                                     | LO21B              |

| 1.8                   | STD   | LP3995ILD-1.8                                   | LP3995ILDX-1.8                                     | LO22B              |

| 1.9 (Note 2)          | STD   | LP3995ILD-1.9                                   | LP3995ILDX-1.9                                     | LO23B              |

| 2.1 (Note 2)          | STD   | LP3995ILD-2.1                                   | LP3995ILDX-2.1                                     | LO24B              |

| 2.5 (Note 2)          | STD   | LP3995ILD-2.5                                   | LP3995ILDX-2.5                                     | LO25B              |

| 2.8                   | STD   | LP3995ILD-2.8                                   | LP3995ILDX-2.8                                     | LO26B              |

| 3.0                   | STD   | LP3995ILD-3.0                                   | LP3995ILDX-3.0                                     | LO30B              |

| 3.3 (Note 2)          | STD   | LP3995ILD-3.3                                   | LP3995ILDX-3.3                                     | LO31B              |

Note 1: Available in sample quantities only

Note 2: For availability contact your local sales office

## **Absolute Maximum Ratings**

#### (Notes 3, 4)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Input Voltage (V <sub>IN</sub> ) | –0.3 to 6.5V                     |

|----------------------------------|----------------------------------|

| Output Voltage                   | –0.3 to (V <sub>IN</sub> + 0.3V) |

|                                  | to 6.5V (max)                    |

| Enable Input Voltage             | –0.3 to 6.5V                     |

| Junction Temperature             | 150°C                            |

| Pad Temperature                  |                                  |

| (Note 5)                         |                                  |

| micro SMD                        | 260°C                            |

| LLP                              | 235°C                            |

| Storage Temperature              | −65 to +150°C                    |

| ESD (Note 7)                     |                                  |

| Human Body Model                 | 2 kV                             |

| Machine Model                    | 200V                             |

## **Operating Ratings** (Note 3)

| Input Voltage (V <sub>IN</sub> ) | 2.5 to 6.0V   |

|----------------------------------|---------------|

| Enable Input Voltage             | 0 to 6.0V     |

| Junction Temperature             | –40 to +125°C |

| Thermal Resistance               |               |

| $\theta_{JA}$ (micro SMD pkg.)   | 255°C/W       |

| θ <sub>JA</sub> (LLP pkg.)       | 88°C/W        |

| Power Dissipation at 25°C        |               |

| (Note 6)                         |               |

| micro SMD                        | 392 mW        |

| LLP                              | 1.136 W       |

## **Electrical Characteristics**

Unless otherwise noted,  $V_{EN} = 1.5$ ,  $V_{IN} = V_{OUT} + 1.0V$ ,  $C_{IN} = 1 \ \mu\text{F}$ ,  $I_{OUT} = 1 \ m\text{A}$ ,  $C_{OUT} = 1 \ \mu\text{F}$ ,  $c_{BP} = 0.01 \ \mu\text{F}$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over the full temperature range for operation, -40 to +125^{\circ}\text{C}. (Note 12)

| Symbol           | Parameter                           | Conditions                                                          | Typical | Limit  |     | Units |  |

|------------------|-------------------------------------|---------------------------------------------------------------------|---------|--------|-----|-------|--|

| Symbol           | Parameter                           |                                                                     |         | Min    | Max | Units |  |

| V <sub>IN</sub>  | Input Voltage                       |                                                                     |         | 2.5    | 6.0 | V     |  |

| DEVICE OUT       | ГРИТ: 1.5 ≤ V <sub>о∪т</sub> < 1.8V |                                                                     |         |        |     |       |  |

| $\Delta V_{OUT}$ | Output Voltage Tolerance            | I <sub>OUT</sub> = 1 mA                                             |         | -50    | 50  |       |  |

|                  |                                     |                                                                     |         | -75    | 75  | - mV  |  |

|                  | Line Regulation Error               | $V_{IN} = (V_{OUT(NOM)}+1.0V)$ to 6.0V,<br>$I_{OUT} = 1 \text{ mA}$ |         | -3.5   | 3.5 | mV/V  |  |

|                  | micro SMD<br>Load Regulation Error  | I <sub>OUT</sub> = 1 mA to 150 mA                                   | 10      |        | 75  | μV/mA |  |

|                  | LLP<br>Load Regulation Error        | I <sub>OUT</sub> = 1 mA to 150 mA                                   | 70      |        | 125 | μV/mA |  |

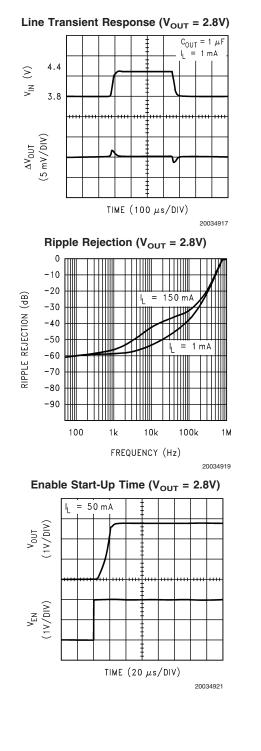

| PSRR             | Power Supply Rejection Ratio        | f = 1 kHz, I <sub>OUT</sub> = 1 mA                                  | 55      |        |     | D     |  |

|                  | (Note 9)                            | f = 10 kHz, I <sub>OUT</sub> = 1 mA                                 | 53      |        |     | dB    |  |

| DEVICE OUT       | ГРИТ: 1.8 ≤ V <sub>ОUT</sub> < 2.5V |                                                                     |         |        |     |       |  |

| $\Delta V_{OUT}$ | Output Voltage Tolerance            | I <sub>OUT</sub> = 1 mA                                             |         | -50 50 | mV  |       |  |

|                  |                                     |                                                                     |         | -75    | 75  |       |  |

|                  | microSMDLine Regulation Error       | $V_{IN} = (V_{OUT(NOM)}+1.0V)$ to 6.0V,<br>$I_{OUT} = 1 \text{ mA}$ |         | -2.5   | 2.5 | mV/V  |  |

|                  | LLP<br>Line Regulation Error        | $V_{IN} = (V_{OUT(NOM)}+1.0V)$ to 6.0V,<br>$I_{OUT} = 1 \text{ mA}$ |         | -3.5   | 3.5 | mV/V  |  |

|                  | micro SMD<br>Load Regulation Error  | I <sub>OUT</sub> = 1 mA to 150 mA                                   | 10      |        | 75  | μV/mA |  |

|                  | LLP<br>Load Regulation Error        | I <sub>OUT</sub> = 1 mA to 150 mA                                   | 80      |        | 125 | μV/mA |  |

| PSRR             | Power Supply Rejection Ratio        | f = 1 kHz, I <sub>OUT</sub> = 1 mA                                  | 55      |        |     |       |  |

|                  | (Note 9)                            | f = 10 kHz, I <sub>OUT</sub> = 1 mA                                 | 50      |        |     | dB    |  |

## Electrical Characteristics (Continued)

Unless otherwise noted,  $V_{EN} = 1.5$ ,  $V_{IN} = V_{OUT} + 1.0V$ ,  $C_{IN} = 1 \ \mu\text{F}$ ,  $I_{OUT} = 1 \ \mu\text{F}$ ,  $C_{OUT} = 1 \ \mu\text{F}$ ,  $c_{BP} = 0.01 \ \mu\text{F}$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over the full temperature range for operation, -40 to +125^{\circ}\text{C}. (Note 12)

| Symbol           | Parameter                    | Conditions                                                          | Typical | Limit |       | Units                 |

|------------------|------------------------------|---------------------------------------------------------------------|---------|-------|-------|-----------------------|

|                  |                              |                                                                     |         | Min   | Max   | Units                 |

| DEVICE OUT       |                              | •                                                                   |         |       |       |                       |

| $\Delta V_{OUT}$ | Output Voltage Tolerance     | I <sub>OUT</sub> = 1 mA                                             |         | -2    | 2     | % of                  |

|                  |                              |                                                                     |         | -3    | 3     | V <sub>OUT(NOM)</sub> |

|                  | Line Regulation Error        | $V_{IN} = (V_{OUT(NOM)}+1.0V)$ to 6.0V,<br>$I_{OUT} = 1 \text{ mA}$ |         | -0.1  | 0.1   | %/V                   |

|                  | micro SMD                    | $I_{OUT} = 1 \text{ mA to } 150 \text{ mA}$                         | 0.0004  |       | 0.002 | %/mA                  |

|                  | Load Regulation Error        |                                                                     | 0.0004  |       | 0.002 | /0/111A               |

|                  | LLP                          | $I_{OUT} = 1 \text{ mA to } 150 \text{ mA}$                         | 0.002   |       | 0.005 | %/mA                  |

|                  | Load Regulation Error        |                                                                     | 0.002   |       | 0.005 | /0/IIIA               |

|                  | Dropout Voltage              | I <sub>OUT</sub> = 1 mA                                             | 0.4     |       | 2     | mV                    |

|                  |                              | I <sub>OUT</sub> = 150 mA                                           | 60      |       | 100   |                       |

| PSRR             | Power Supply Rejection Ratio | $f = 1 \text{ kHz}, I_{OUT} = 1 \text{ mA}$                         | 60      |       |       | dD                    |

|                  | (Note 9)                     | $f = 10 \text{ kHz}, I_{OUT} = 1 \text{ mA}$                        | 50      |       |       | - dB                  |

LP3995

## Electrical Characteristics (Continued)

Unless otherwise noted,  $V_{EN} = 1.5$ ,  $V_{IN} = V_{OUT} + 1.0V$ ,  $C_{IN} = 1 \ \mu\text{F}$ ,  $I_{OUT} = 1 \ \text{mA}$ ,  $C_{OUT} = 1 \ \mu\text{F}$ ,  $c_{BP} = 0.01 \ \mu\text{F}$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over the full temperature range for operation, -40 to +125^{\circ}\text{C}. (Note 12)

| Symbol                  | Parameter                                      | Conditions                                                | Typical - | Limit |     | Unite |

|-------------------------|------------------------------------------------|-----------------------------------------------------------|-----------|-------|-----|-------|

| Symbol                  |                                                |                                                           |           | Min   | Max | Units |

| FULL V <sub>OUT</sub> F | RANGE                                          |                                                           |           |       |     | •     |

| ILOAD                   | Load Current                                   | (Notes 8, 9)                                              |           | 0     |     | μA    |

| l <sub>Q</sub>          | Quiescent Current                              | $V_{EN} = 1.5V, I_{OUT} = 0 \text{ mA}$                   | 85        |       | 150 |       |

|                         |                                                | $V_{EN} = 1.5V, I_{OUT} = 150 \text{ mA}$                 | 140       |       | 200 | μΑ    |

|                         |                                                | $V_{EN} = 0.4V$                                           | 0.003     |       | 1.5 |       |

| I <sub>sc</sub>         | Short Circuit Current Limit                    |                                                           | 450       |       |     | mA    |

| E <sub>N</sub>          | Output Noise Voltage ((Note 9))                | $BW = 10 \text{ Hz to } 100 \text{ kHz},$ $V_{IN} = 4.2V$ | 25        |       |     | μVrms |

| T <sub>SHUTDOWN</sub>   | Thermal Shutdown                               | Temperature                                               | 160       |       |     | °C    |

|                         |                                                | Hysteresis                                                | 20        |       |     | 1     |

| ENABLE CO               | NTROL CHARACTERISTICS                          |                                                           |           |       |     |       |

| I <sub>EN</sub>         | Maximum Input Current at V <sub>EN</sub> Input | $V_{EN} = 0.0V$ and $V_{IN} = 6.0V$                       | 0.001     |       |     | μA    |

| V <sub>IL</sub>         | Low Input Threshold                            |                                                           |           |       | 0.4 | V     |

| V <sub>IH</sub>         | High Input Threshold                           |                                                           |           | 0.9   |     | V     |

| TIMING CHA              | RACTERISTICS                                   |                                                           |           |       |     |       |

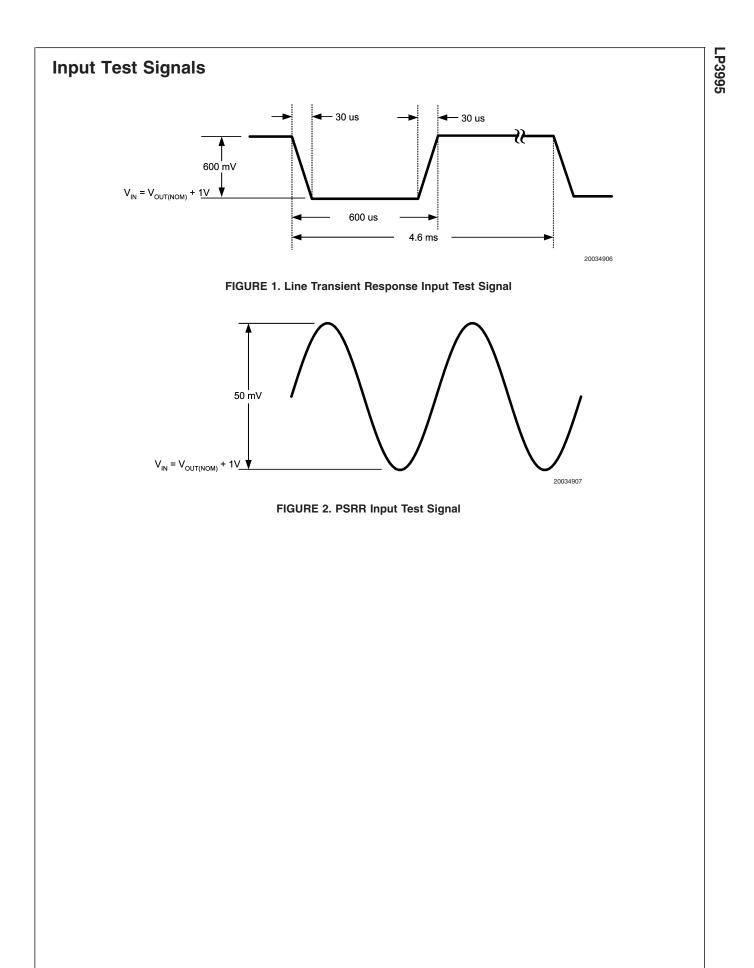

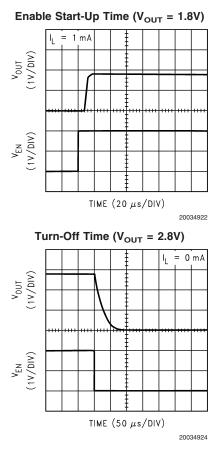

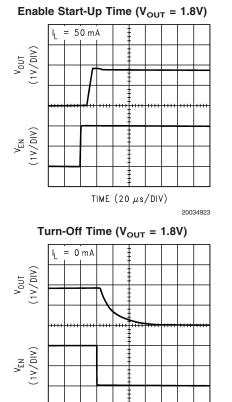

| T <sub>ON</sub>         | Turn On Time (Note 9)                          | To 95% Level (Note 10)                                    | 30        |       |     | μS    |

| T <sub>OFF</sub>        | Turn Off Time (Note 9)                         | To 5% Level (Note 11)                                     | 175       |       |     | μS    |

Note 3: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 4: All voltages are with respect to the potential at the GND pin.

Note 5: For information regarding micro SMD and LLP packages please refer to the following application notes;

AN-1112 Micro SMD Package Wafer Level Chip Scale Package,

AN-1187. Leadless Leadframe Package.

Note 6: The maximum power dissipation of the device is dependent on the maximum allowable junction temperature for the device and the ambient temperature. This relationship is given by the formula

$$\mathsf{P}_{\mathsf{D}} = (\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{A}})/\theta_{\mathsf{J}\mathsf{A}}$$

Where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

Assuming an ambient temperature of 25°C, for the maximum operating junction temperature of 125°C and the micro SMD package  $\theta_{JA}$  of 255°C/W, this gives a figure of 392 mW for the allowable power dissipation.

The derating factor  $(-1/\theta_{JA}) = -3.9 \text{ mW/}^{\circ}\text{C}$ , thus below 25°C the power dissipation figure can be increased by 3.9 mW/ $^{\circ}$ C, and similarly decreased by this factor for temperatures above 25°C.

Similarly the numbers for the absolute maximum case can be derived using a figure of 150°C for the junction temperature.

Note 7: The human body model is an 100 pF discharge through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 8: The device maintains a stable, regulated output voltage without load.

Note 9: This electrical specification is guaranteed by design.

Note 10: Time from  $V_{EN}$  = 0.9V to  $V_{OUT}$  = 95%  $(V_{OUT(NOM)})$

Note 11: Time from  $V_{EN}$  = 0.4V to  $V_{OUT}$  = 5%  $(V_{OUT(NOM)})$

**Note 12:** All limits are guaranteed. All electrical characteristics having room-temperature limits are tested during production at  $T_J = 25^{\circ}C$  or correlated using Statistical Quality Control methods. Operation over the temperature specification is guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

## **Recommended Output Capacitor**

| Symbol           | Parameter        | Conditions            | VALUE | Limit |     | Units |

|------------------|------------------|-----------------------|-------|-------|-----|-------|

|                  |                  |                       |       | Min   | Max | Units |

| C <sub>OUT</sub> | Output Capacitor | Capacitance (Note 13) | 1.0   | 0.75  |     | μF    |

|                  |                  | ESR                   |       | 5     | 500 | mΩ    |

Note 13: The capacitor tolerance should be ±25% or better over the temperature range. Recommended types are X7R, Y5V, and Z5U.

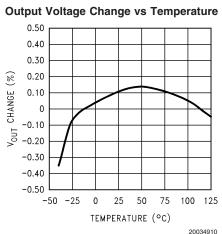

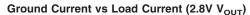

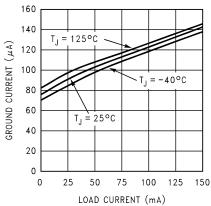

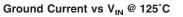

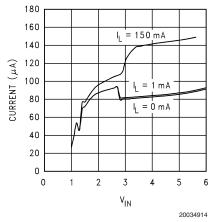

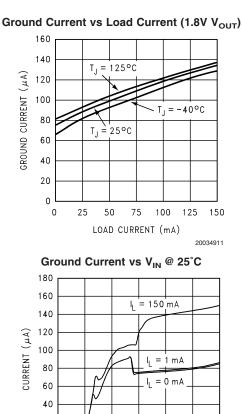

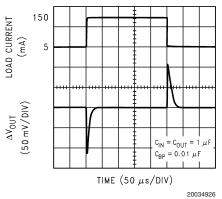

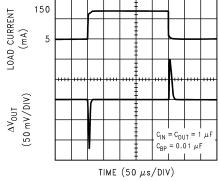

## **Typical Performance Characteristics** Unless otherwise specified, $C_{IN} = C_{OUT} = 1.0 \ \mu\text{F}$ Ceramic, $V_{IN} = V_{OUT} + 1.0V$ , $T_A = 25^{\circ}\text{C}$ , Enable pin is tied to $V_{IN}$ .

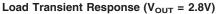

**Typical Performance Characteristics** Unless otherwise specified,  $C_{IN} = C_{OUT} = 1.0 \ \mu\text{F}$  Ceramic,  $V_{IN} = V_{OUT} + 1.0V$ ,  $T_A = 25^{\circ}\text{C}$ , Enable pin is tied to  $V_{IN}$ . (Continued)

TIME (20  $\mu$ s/DIV)

20034920

LP3995

LP3995

**Typical Performance Characteristics** Unless otherwise specified,  $C_{IN} = C_{OUT} = 1.0 \ \mu\text{F}$  Ceramic,  $V_{IN} = V_{OUT} + 1.0V$ ,  $T_A = 25^{\circ}\text{C}$ , Enable pin is tied to  $V_{IN}$ . (Continued)

20034925

#### Load Transient Response (V<sub>OUT</sub> = 1.8V)

TIME (50  $\mu$ s/DIV)

20034927

# LP3995

## **Application Hints**

#### POWER DISSIPATION AND DEVICE OPERATION

The permissible power dissipation for any package is a measure of the capability of the device to pass heat from the power source, the junctions of the IC, to the ultimate heat sink, the ambient environment. Thus the power dissipation is dependent on the ambient temperature and the thermal resistance across the various interfaces between the die and ambient air.

The Thermal Resistance figure

As stated in (Note 6) in the electrical specification section, the allowable power dissipation for the device in a given package can be calculated using the equation:

$$P_{D} = \frac{(T_{J(MAX)} - T_{A})}{\theta_{JA}}$$

With a  $\theta_{JA}$  = 255°C/W, the device in the micro SMD package returns a value of 392 mW with a maximum junction temperature of 125°C.

With a  $\theta_{JA}$  = 88°C/W, the device in the LLP package returns a value of 1.136 mW with a maximum junction temperature of 125°C.

The actual power dissipation across the device can be represented by the following equation:

$$\mathsf{P}_\mathsf{D} = (\mathsf{V}_\mathsf{IN} - \mathsf{V}_\mathsf{OUT}) \ge \mathsf{I}_\mathsf{OUT}.$$

This establishes the relationship between the power dissipation allowed due to thermal consideration, the voltage drop across the device, and the continuous current capability of the device. These two equations should be used to determine the optimum operating conditions for the device in the application.

#### **EXTERNAL CAPACITORS**

In common with most regulators, the LP3995 requires external capacitors to ensure stable operation. The LP3995 is specifically designed for portable applications requiring minimum board space and smallest components. These capacitors must be correctly selected for good performance.

#### **INPUT CAPACITOR**

An input capacitor is required for stability. It is recommended that a 1.0  $\mu F$  capacitor be connected between the LP3995 input pin and ground (this capacitance value may be increased without limit).

This capacitor must be located a distance of not more than 1 cm from the input pin and returned to a clean analogue ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input.

**Important:** Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a lowimpedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for the **ESR** (Equivalent Series Resistance) on the input capacitor, but tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance will remain  $\cong 1.0 \ \mu\text{F}$  over the entire operating temperature range.

#### OUTPUT CAPACITOR

The LP3995 is designed specifically to work with very small ceramic output capacitors. A ceramic capacitor (dielectric types Z5U, Y5V or X7R) in the 1.0 [to 10  $\mu\text{F}$ ] range, and with ESR between 5 m $\Omega$  to 500 m $\Omega$ , is suitable in the LP3995 application circuit.

For this device the output capacitor should be connected between the  $V_{\rm OUT}$  pin and ground.

It may also be possible to use tantalum or film capacitors at the device output,  $V_{OUT}$ , but these are not as attractive for reasons of size and cost (see the section Capacitor Characteristics).

The output capacitor must meet the requirement for the minimum value of capacitance and also have an ESR value that is within the range 5 m $\Omega$  to 500 m $\Omega$  for stability.

#### **NO-LOAD STABILITY**

The LP3995 will remain stable and in regulation with no external load. This is an important consideration in some circuits, for example CMOS RAM keep-alive applications.

#### CAPACITOR CHARACTERISTICS

The LP3995 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer. For capacitance values in the range of 1  $\mu$ F to 4.7  $\mu$ F, ceramic capacitors are the smallest, least expensive and have the lowest ESR values, thus making them best for eliminating high frequency noise. The ESR of a typical 1  $\mu$ F ceramic capacitor is in the range of 20 m $\Omega$  to 40 m $\Omega$ , which easily meets the ESR requirement for stability for the LP3995.

The temperature performance of ceramic capacitors varies by type. Most large value ceramic capacitors ( $\geq 2.2~\mu F)$  are manufactured with Z5U or Y5V temperature characteristics, which results in the capacitance dropping by more than 50% as the temperature goes from 25°C to 85°C.

A better choice for temperature coefficient in a ceramic capacitor is X7R. This type of capacitor is the most stable and holds the capacitance within  $\pm 15\%$  over the temperature range. Tantalum capacitors are less desirable than ceramic for use as output capacitors because they are more expensive when comparing equivalent capacitance and voltage ratings in the 1  $\mu$ F to 4.7  $\mu$ F range.

Another important consideration is that tantalum capacitors have higher ESR values than equivalent size ceramics. This means that while it may be possible to find a tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly) than a ceramic capacitor with the same ESR value. It should also be noted that the ESR of a typical tantalum will increase about 2:1 as the temperature goes from  $25^{\circ}$ C down to  $-40^{\circ}$ C, so some guard band must be allowed.

#### NOISE BYPASS CAPACITOR

A bypass capacitor should be connected between the  $C_{BP}$  pin and ground to significantly reduce the noise at the regulator output. This device pin connects directly to a high impedance node within the bandgap reference circuitry. Any significant loading on this node will cause a change on the regulated output voltage. For this reason, DC leakage current through this pin must be kept as low as possible for best output voltage accuracy.

The use of a 0.01uF bypass capacitor is strongly recommended to prevent overshoot on the output during start-up.

## Application Hints (Continued)

The types of capacitors best suited for the noise bypass capacitor are ceramic and film. High quality ceramic capacitors with NPO or COG dielectric typically have very low leakage. Polypropolene and polycarbonate film capacitors are available in small surface-mount packages and typically have extremely low leakage current.

Unlike many other LDO's, the addition of a noise reduction capacitor does not effect the transient response of the device.

#### ENABLE OPERATION

The LP3995 may be switched ON or OFF by a login input at the ENABLE pin,  $V_{EN}$ . A high voltage at this pin will turn the device on. When the enable pin is low, the regulator output is off and the device typically consumes 3 nA. If the application does not require the shutdown feature, the  $V_{EN}$  pin should be tied to  $V_{IN}$  to keep the regulator output permanently on. To ensure proper operation, the signal source used to drive the  $V_{EN}$  input must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under  $V_{IL}$  and  $V_{IH}$ .

#### FAST TURN OFF AND ON

The controlled switch-off feature of the device provides a fast turn off by discharging the output capacitor via an internal FET device. This discharge is current limited by the RDSon of this switch. Fast turn-on is guaranteed by control circuitry within the reference block allowing a very fast ramp of the output voltage to reach the target voltage.

#### micro SMD MOUNTING

The micro SMD package requires specific mounting techniques which are detailed in National Semiconductor Application Note AN-1112.

Referring to the section *Surface Mount Technology (SMT) Assembly Considerations*, it should be noted that the pad style which must be used with the 5 pin package is NSMD (non-solder mask defined) type.

For best results during assembly, alignment ordinals on the PC board may be used to facilitate placement of the micro SMD device.

#### micro SMD LIGHT SENSITIVITY

Exposing the micro SMD device to direct sunlight will cause incorrect operation of the device. Light sources such as halogen lamps can affect electrical performance if they are situated in proximity to the device.

Light with wavelengths in the red and infra-red part of the spectrum have the most detrimental effect thus the fluorescent lighting used inside most buildings has very little effect on performance. Tests carried out on a micro SMD test board showed a negligible effect on the regulated output voltage when brought within 1 cm of a fluorescent lamp. A deviation of less than 0.1% from nominal output voltage was observed.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.