Ordering number : EN4799A

### **Overview**

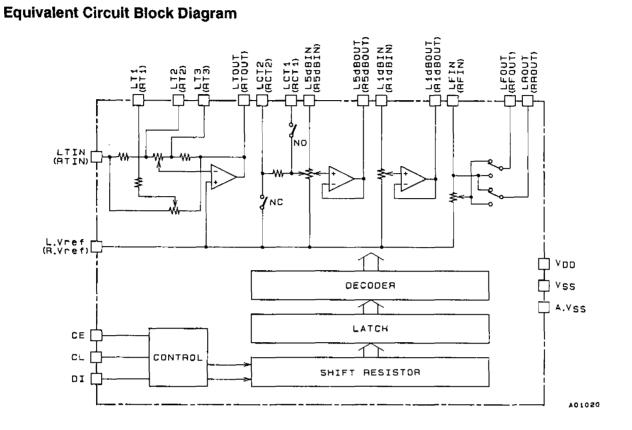

The LC7538JM is a fully equipped electronic volume IC which permits significant reductions in externally connected components while providing ample volume, balance, loudness, fader, bass and treble control functions.

#### **Features**

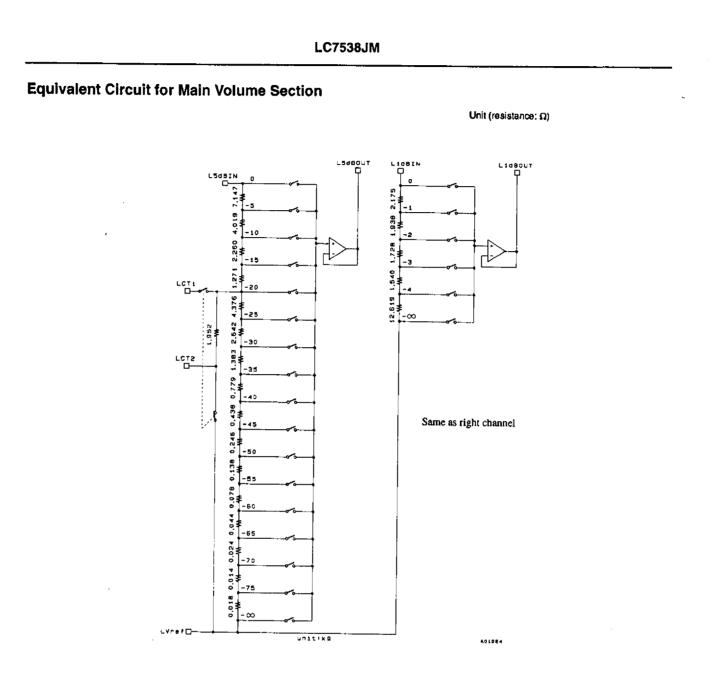

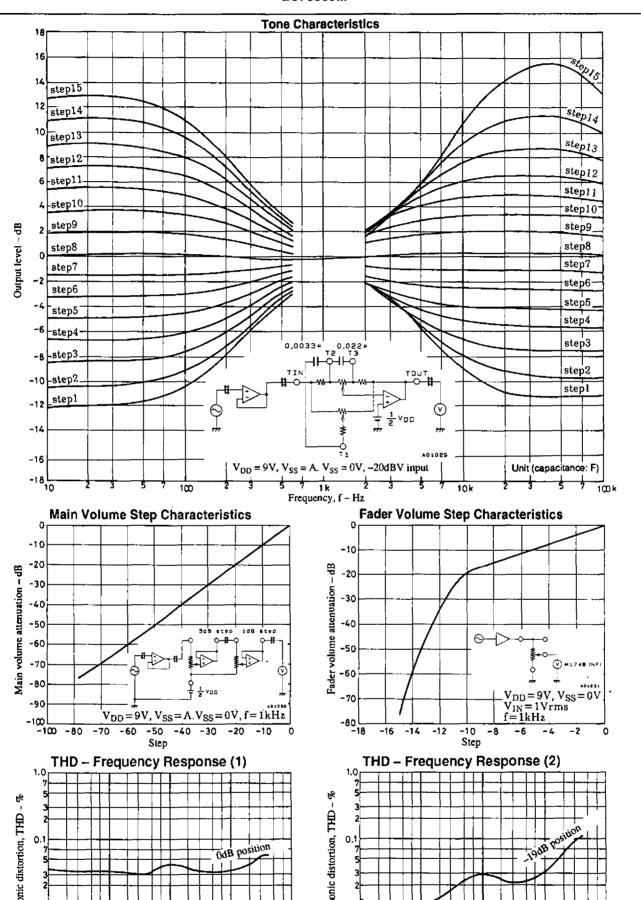

- Volume : 81 positions ranging from 0 dB to -79 dB (in 1 dB increments) plus -∞. Separate left and right control provides excellent balance function.

- : Loudness operation provided by Loudness externally attached CR to activate tap at the -20 dB position of the volume ladder resistor.

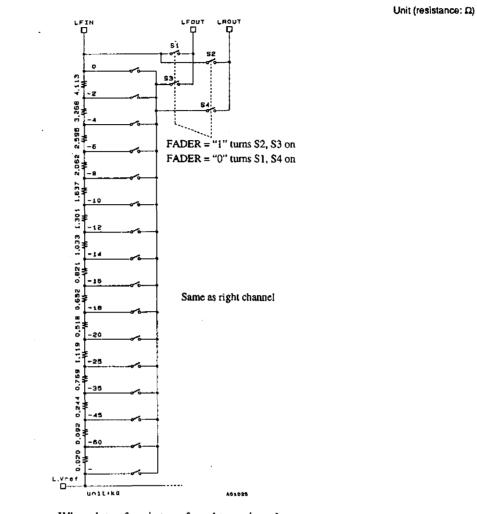

- Fader : Fader function traversing 16 positions with rear or front attenuated output only (these 16 positions consist of 2 dB step intervals ranging from 0 dB to -20 dB, 5 dB step intervals ranging from -20 dB to -45 dB, plus the end settings of -60 dB and -...).

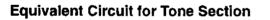

- Bass and Treble: Using externally attached C (capacitor), the LC7538JM provides bass-treble mutual 15-position control and formats a NF-form tone control circuit (LUX form).

- · On-chip op amplifier for caching applications reduces external components.

- Reduced switching noise with silicon gate CMOS processor.

- All controls performed using serial data input (C<sup>2</sup>B).

### Specifications

Absolute Maximum Ratings at  $Ta = 25^{\circ}C$ ,  $V_{SS} = 0 V$

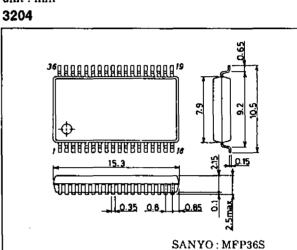

### **Package Dimensions**

unit : mm

| Parameter                   | Symbol               | Conditions                                                | Ratings                          | Unit |  |

|-----------------------------|----------------------|-----------------------------------------------------------|----------------------------------|------|--|

| Maximum supply voltage      | V <sub>DD</sub> max  | V <sub>DD</sub>                                           | 11                               | V    |  |

|                             | V <sub>IN</sub> max1 | CL, DI, CE                                                | $V_{SS} = 0.3$ to $V_{DD} = 0.3$ | v    |  |

| Maximum input voltage       | V <sub>IN</sub> max2 | LTIN, RTIN, L5dBIN, R5dBIN, L1dBIN, R1dBIN,<br>LFIN, RFIN | $V_{SS} = 0.3$ to $V_{DD} + 0.3$ | v    |  |

| Allowable power dissipation | Pd max               | Ta ≤ 85°C                                                 | 210                              | mW   |  |

| Operating temperature       | Topr                 |                                                           | -40 to +85                       | °C   |  |

| Storage temperature         | Tstg                 |                                                           | -50 to +125                      | °C   |  |

## SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito ku, TOKYO, 110 JAPAN

83194 TH (OT) B8-0913 No. 4799-1/13

# Allowable Operation Conditions at Ta = 25°C, $V_{SS}$ = 0 V

| Descenter                 |        |                                                           |                 |     |                 |      |  |

|---------------------------|--------|-----------------------------------------------------------|-----------------|-----|-----------------|------|--|

| Parameter                 | Symbol | Conditions                                                | min             | typ | max             | Unit |  |

| Supply voltage            | VDD    | *1                                                        | 7.0             |     | 10.0            | v    |  |

| Input high level voltage  | VIH    | CL, DI, CE                                                | 4.0             |     | V <sub>DD</sub> |      |  |

| Input low level voltage   | VIL    | CL, DI, CE                                                | V <sub>SS</sub> |     | 1.0             | V    |  |

| Input amplitude voltage V |        | LTIN, RTIN, L5dBIN, R5dBIN, L1dBIN,<br>R1dBIN, LFIN, RFIN | V <sub>SS</sub> |     | V <sub>DD</sub> | Vp-p |  |

| Input pulse width         | tøw    | CL                                                        | 1               |     |                 | μs   |  |

| Setup time                | 1SETUP | CL, DI, CE                                                | 1               |     |                 | μ\$  |  |

| Hold time                 | tHOLD  | CL, DI, CE                                                | 1               |     |                 | μs   |  |

| Operating Frequency       | fopg   | CL                                                        |                 |     | 500             | kHz  |  |

Note: 1. A capacitor rated at 2000 pF or less should be installed between all power supply pins and V<sub>SS</sub>.

# Electrical Characteristics at Ta = 25°C, $V_{DD}$ = 9 V, $V_{SS}$ = 0 V

|                             |                      |                                                                                                                                                                                  |     | Τ    |      |      |  |  |

|-----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--|--|

| Parameter                   | Symbol               | Conditions                                                                                                                                                                       | min | typ  | max  | Unit |  |  |

| Total harmonic distortion   | THD (1)              | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, total overall flat                                                                                                                          |     | 0.04 |      | %    |  |  |

|                             | THD (2)              | V <sub>IN</sub> = 1 Vrms, 1 = 20 kHz, total overall flat                                                                                                                         |     | 0.06 |      | %    |  |  |

| Crosstalk                   | Ст                   | $V_{IN} = 1$ Vrms, f = 1 kHz,<br>total overall flat, Rg = 1 k $\Omega$                                                                                                           | 60  | 87   |      | dB   |  |  |

| Maximum Output Reduction    | Vo min               | VominV <sub>IN</sub> = 1 Vrms, f = 1 kHz,<br>main volume $\rightarrow\infty$ , fader volume $\rightarrow\infty$ ,<br>C = 1000 $\mu$ F between Vref and V <sub>SS</sub> for L/RB2 |     |      |      |      |  |  |

|                             | R <sub>VOL</sub> (1) | 5 dB step                                                                                                                                                                        | 15  | 25   | 35   | kΩ   |  |  |

|                             | R <sub>VOL</sub> (2) | 1 dB step                                                                                                                                                                        | 12  | 20   | 28   | kΩ   |  |  |

| All Resistance Value        | RFADER               |                                                                                                                                                                                  | 12  | 20   | 28   | kΩ   |  |  |

|                             | RBASS                |                                                                                                                                                                                  | 48  | 80   | 112  | kΩ   |  |  |

|                             | RTREBLE              |                                                                                                                                                                                  | 30  | 50   | 70   | kΩ   |  |  |

| Input high level current    | ήн                   | VI = 8 V (CL, CE, DI pins)                                                                                                                                                       |     |      | 10   | μA   |  |  |

| Input low level current     | )IL                  | VI = 0 V (CL, CE, DI pins)                                                                                                                                                       | -10 |      |      | μΑ   |  |  |

| Output noise voltage        | VN                   | All overall flat (IHF-A), Rg = 1 kΩ                                                                                                                                              |     | 7.5  | 15   | μV   |  |  |

| Current dissipation         | IDD                  | V <sub>DD</sub> -V <sub>SS</sub> = 10 V                                                                                                                                          |     | 15   | 21   | mA · |  |  |

|                             |                      | CT1                                                                                                                                                                              | 1.8 | 3.0  | 4.2  | kΩ   |  |  |

|                             |                      | Between CT2 and Vref                                                                                                                                                             | 0.6 | 1.0  | 1.4  | kΩ   |  |  |

| Analog switch on resistance | R <sub>ON</sub>      | Fader S1 to S4                                                                                                                                                                   | 1.8 | 3.0  | 4.2  | kΩ   |  |  |

|                             |                      |                                                                                                                                                                                  | 0.6 | 1.0  | 1.4  | kΩ   |  |  |

|                             |                      | All other cases                                                                                                                                                                  | 6.0 | 10.0 | 14.0 | kΩ   |  |  |

No. 4799-2/13

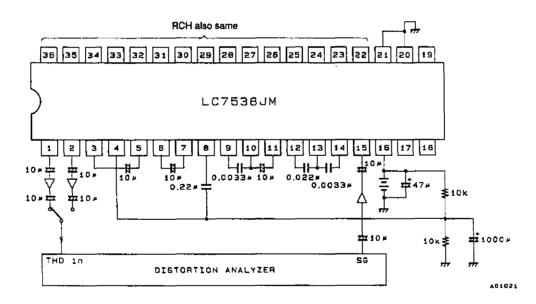

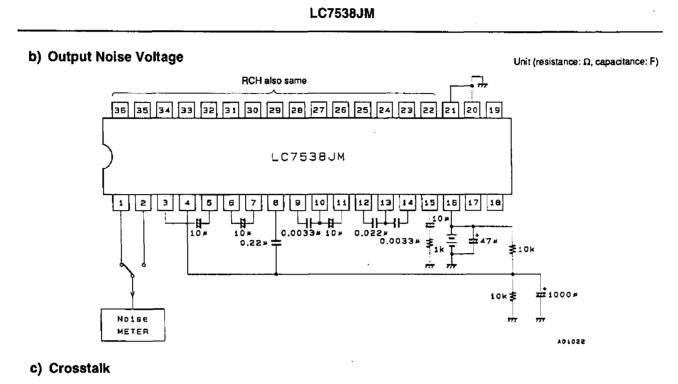

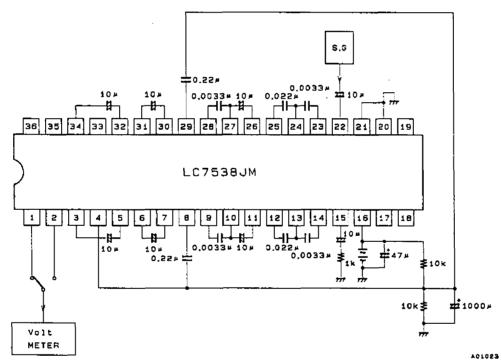

# **Test Circuit**

•

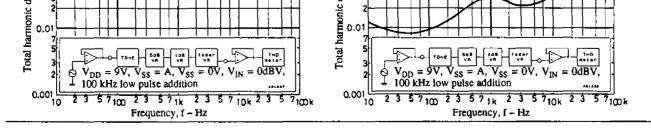

a) Total Harmonic Distortion

Unit (resistance: D, capacitance: F)

### LC7538JM

No. 4799-3/13

۰.

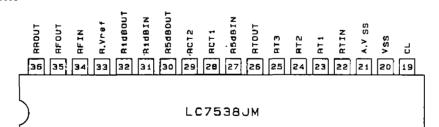

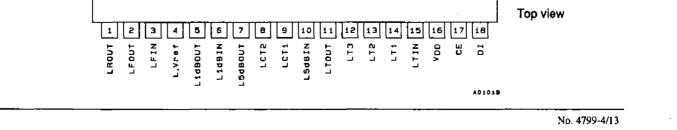

**Pin Assignment**

# **Pin Descriptions**

| Pin name | Pin No. | Description                                                                                                                                                                                                                                                                                                                                   | Remarks                     |  |  |  |  |  |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|

| LROUT    | 1       | These pins function as output pins for the fader. Output reduction for rear and                                                                                                                                                                                                                                                               | <del>ب</del> ۵۵,            |  |  |  |  |  |

| LFOUT    | 2       | front is performed separately for each. Attenuation capacity is unified for                                                                                                                                                                                                                                                                   |                             |  |  |  |  |  |

| RROUT    | 36      | both left and right. Step positioning is designed using an open circuit so that                                                                                                                                                                                                                                                               | _ <b>≭</b> L_ <sub>₿≸</sub> |  |  |  |  |  |

| RFOUT    | 35      | reception is performed using high impedance.                                                                                                                                                                                                                                                                                                  | VSS AUZARS                  |  |  |  |  |  |

| LFIN     | 3       | <ul> <li>When utilizing the fader function, these pins function as input pins.</li> </ul>                                                                                                                                                                                                                                                     |                             |  |  |  |  |  |

| RFIN     | 34      | Low impedance driven.                                                                                                                                                                                                                                                                                                                         | VS5                         |  |  |  |  |  |

| LVREF    | 4       | <ul> <li>These pins are common plns for fader volume, tone and main volume.<br/>The pattern impedance connected here should be lowered as much as possible.</li> <li>LVref and RVref are not connected to V<sub>SS</sub>.</li> <li>Connections for LVref and RVref to V<sub>SS</sub> should be established externally to</li> </ul>           |                             |  |  |  |  |  |

| RVREF    | 33      | <ul> <li>match all specifications. Notably, attention should be paid to capacity since capacitors are subject to residual resistance during volume output reduction when installed between LVref (RVref) and V<sub>SS</sub> as is the case with single power sources.</li> <li>Normally, high voltage applied from V<sub>DD</sub>.</li> </ul> |                             |  |  |  |  |  |

| L1dBOUT  | 5       | These pins are output pins for the 1 dB step attenuator located in the section main volume.                                                                                                                                                                                                                                                   |                             |  |  |  |  |  |

| R1dBOUT  | 32      |                                                                                                                                                                                                                                                                                                                                               |                             |  |  |  |  |  |

| L1dBIN   | 6       | <ul> <li>These pins are input pins for the 1 dB step attenuator located in the section<br/>main volume.</li> </ul>                                                                                                                                                                                                                            |                             |  |  |  |  |  |

| R1dBIN   | 31      | Low Impedance driven.                                                                                                                                                                                                                                                                                                                         |                             |  |  |  |  |  |

|          | 7       | These pins are output pins for the 5 dB step attenuator located in the section                                                                                                                                                                                                                                                                |                             |  |  |  |  |  |

| R5dBOUT  | 30      | main volume.                                                                                                                                                                                                                                                                                                                                  |                             |  |  |  |  |  |

| LCT1     | 9       |                                                                                                                                                                                                                                                                                                                                               |                             |  |  |  |  |  |

| LCT2     | 8       | These pins are for loudness control. Connect a high-band compensation capacitor between CT1 to 5dB IN and a low-band compensation capacitor                                                                                                                                                                                                   |                             |  |  |  |  |  |

| RCT1     | 28      | between CT2 to Vref.                                                                                                                                                                                                                                                                                                                          |                             |  |  |  |  |  |

| RCT2     | 29      | ]                                                                                                                                                                                                                                                                                                                                             |                             |  |  |  |  |  |

| L5dBIN   | 10      | <ul> <li>These pins are input pins for the 5 dB step attenuator located in the section<br/>main volume.</li> </ul>                                                                                                                                                                                                                            |                             |  |  |  |  |  |

| R5dBIN   | 27      | <ul> <li>Low impedance driven.</li> </ul>                                                                                                                                                                                                                                                                                                     | V55 /// A02102              |  |  |  |  |  |

| LTOUT    | 11      | - These pins are output pins for tone control.                                                                                                                                                                                                                                                                                                |                             |  |  |  |  |  |

| RTOUT    | 26      |                                                                                                                                                                                                                                                                                                                                               | Vref AVSS AC2165            |  |  |  |  |  |

Continued on next page.

No. 4799-5/13

## Continued from preceding page.

| Pin name           | Pin No. | Description                                                                                                                                                                                                                                   | Remarks                        |

|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| LT3                | 12      |                                                                                                                                                                                                                                               |                                |

| LT2                | 13      | These pins are for connecting bass and treble compensation for the tone                                                                                                                                                                       |                                |

| LT1                | 14      | circuit.                                                                                                                                                                                                                                      | <b>*</b>                       |

| RT3                | 25      | Connect a high-band compensation capacitor between T1 and T2.                                                                                                                                                                                 | □                              |

| RT2                | 24      | Connect a low-band compensation capacitor between 12 and 13.                                                                                                                                                                                  | <sup>v</sup> s5 <del>,,,</del> |

| RT1                | 23      |                                                                                                                                                                                                                                               | AG2168                         |

| LTIN               | 15      | These pins are tone control input pins.                                                                                                                                                                                                       |                                |

| RTIN               | 22      | • Low impedance driven.                                                                                                                                                                                                                       | VSS                            |

| V <sub>DD</sub>    | 16      | Supply voltage pin.                                                                                                                                                                                                                           |                                |

| A. V <sub>SS</sub> | 21      | • Ground pin for on-chip op amp.                                                                                                                                                                                                              | A02187                         |

| V <sub>SS</sub>    | 20      | Ground pin for internal logic.                                                                                                                                                                                                                | A02100                         |

| CE                 | 17      | <ul> <li>This is the chip enable pin. According to the timing of the switch from high to<br/>low, data is written to an internal latch and all analog switches operate.</li> <li>Data transfer with high-level switches to enable.</li> </ul> |                                |

| Di                 | 18      | • These are input pins for the clock and serial data for control.                                                                                                                                                                             |                                |

| CL                 | 19      |                                                                                                                                                                                                                                               |                                |

No. 4799-6/13

No. 4799-7/13

·

•

When data of  $-\infty$  is transferred to main volume control 1 dB step, S1 and S2 open and S3, S4 are turned on simultaneously.

LC7538JM

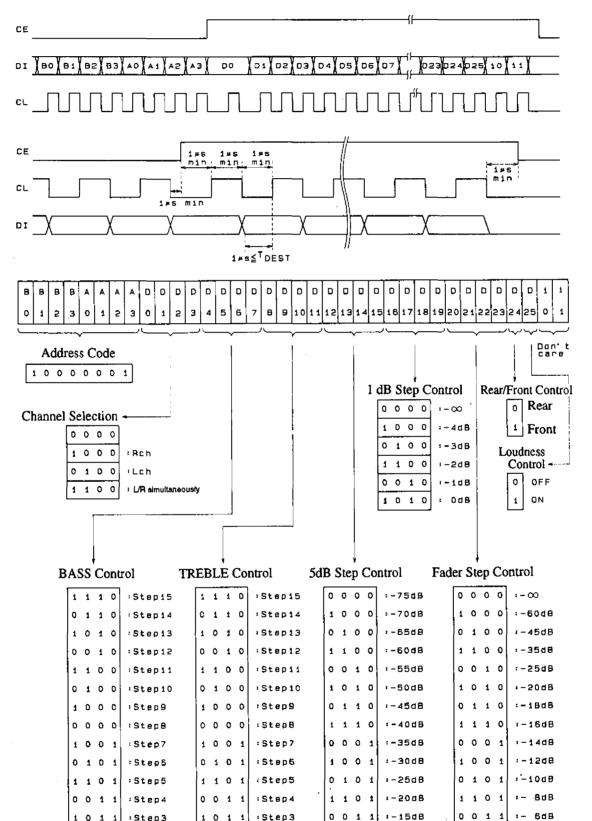

### **Control System Timing and Data Format**

Controlling of LC7538JM involves the input of regulating serial data to CE, CL and DI pins. Data format consists of 36 bits composed of an 8-bit address and 28-bit data.

|          |   |   |   |   |               |    |   |   |   |        |   |   |   |     |        |   |   |   |     |     | 01027        |

|----------|---|---|---|---|---------------|----|---|---|---|--------|---|---|---|-----|--------|---|---|---|-----|-----|--------------|

| <b>–</b> |   |   |   |   | 1             |    |   |   |   |        | 1 | 1 | 1 | 1   | : 0dB  | 1 | 1 | 1 | 1   | ı   | OdB          |

|          | 1 | 1 | 1 | 1 | Step1         | 1  | 1 | 1 | 1 | Step1  | 0 | 1 | 1 | 1   | *- 5d8 | ٥ | 1 | 1 | 1   | 1 - | 2 <b>d</b> B |

|          | 0 | 1 | 1 | 1 | Step2         | 0  | 1 | 1 | 1 | :Step2 | 1 | 0 | 1 | 1   |        |   |   |   |     |     | 4dB          |

|          | • | • | - | - | 1 . 91. 6 1 2 | 11 | • | • | - |        | - | - | _ | - ( |        | - |   |   | - 1 |     | •            |

No. 4799-9/13

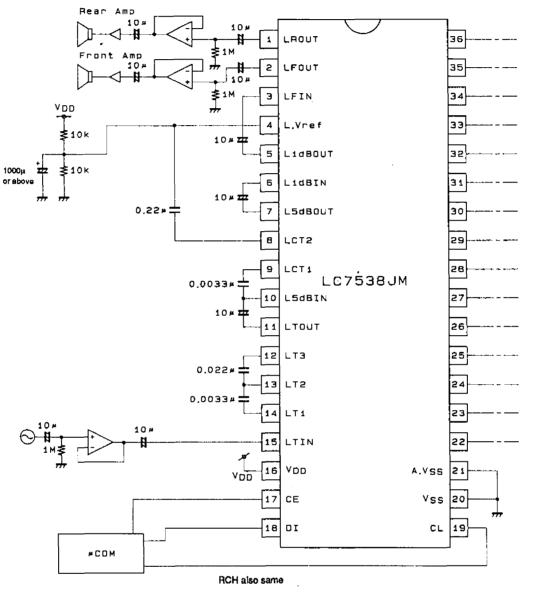

Sample Application Circuit

Unit (resistance:  $\Omega$ , capacitance: F)

A01028

Note: Bipolar electrolytic capacitors should be used as widely as possible where others are not recommended directly.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall; © Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use: ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or

- litigation on SÁNYO ELECTRIC CÓ., LTD., its affiliates, subsidiaries and distributors or any of

their officers and employees jointly or severally.

■ Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

No. 4799-10/13

No. 4799-11/13

No. 4799-12/13

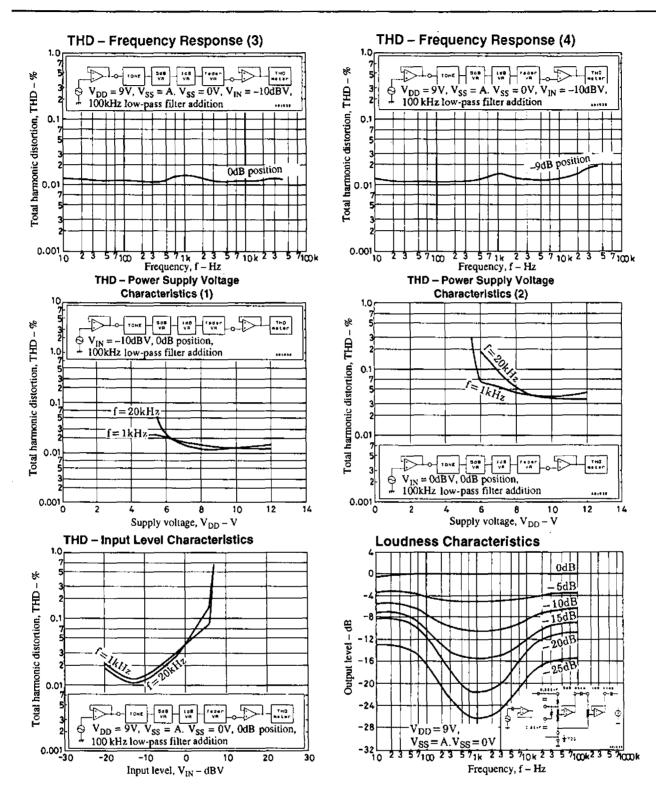

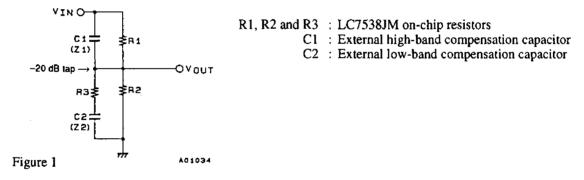

### Loudness External Constant Calculation Sample

First, refer to page 7 where the 5 dB step internal equivalent circuit for the LC7538JM is shown. Using this information, an external constant for loudness can be added to establish a simplified circuit for computation as shown in Figure 1. Computations gaining a 5 dB boost with f = 100 Hz using this configuration are shown in the following. (f = 100 Hz and 5 dB boost)

Within figure 1, when R and C are defined as:

R1 = R2 = 10 k $\Omega$ R3 = 1 k $\Omega$ C1 =Z1, C2 = Z2, then the following equation can be established:

$$VOUT = \frac{\frac{R2 (R3 + Z2)}{R2 + R3 + Z2}}{\frac{R1 \cdot Z1}{R1 + Z1} + \frac{R2 (R3 + Z2)}{R2 + R3 + Z2}} = -20 dB$$

$$VOUT = \frac{\frac{R2 (R3 + 10 \cdot Z2)}{R2 + R3 + 10 \cdot Z2}}{\frac{R1 \cdot 10 \cdot Z1}{R1 + 10 \cdot Z1} + \frac{R2(R3 + 10 \cdot Z2)}{R2 + R3 + 10 \cdot Z2}} = -15 dB$$

thereby resulting in,

$Z1 \neq 178.3 \text{ k}\Omega$  and  $Z2 = 176 \Omega$ .

Under such conditions where f = 1 kHz, specifications may be satisfied if C (capacitor) having these impedances is supplied externally. The end result is that C1 = 893 pF and C2 = 0.9  $\mu$ F.

Notes for Above Applications

- When the power supply is turned on, the internal analog switch becomes inexact. Until data is set, counter measures such as those required for muting are performed externally.

- In order to prevent crossover into the analog system of high-frequency digital signals transferred to the CL, DI and CE pins, transfer along these signal lines should occur along shielded lines, or the signal lines should be protected by using the grounding pattern or the circuit.

- For volume steps with large attenuation levels (over -20 dB), when the loudness circuit is off the high frequency region (above about 4 kHz) will be attenuated by about 3 dB relative to the low frequency region (about 400 Hz) due to the influence of the resistance of the loudness circuit analog switch. Therefore we recommend using tone control compensation together with the volume step described above.

- When sending data immediately after power on, send data as follows:

- When sending independent left and right data, send data at least four times.

X Leh data X Reh data X Leh data X Ach data X

- Alternatively, when sending data that drives the left and right channels at the same time, send the data at least twice.

LR data X LR data X

No. 4799-13/13