# **NEC**

# **Design Manual**

# **CB-9 Family VX/VM Type**

0.35  $\mu m$  CMOS Cell-Based IC

# [MEMO]

### NOTES FOR CMOS DEVICES -

### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### **③ STATUS BEFORE INITIALIZATION OF MOS DEVICES**

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

OPENCAD and V. sim are trademarks of NEC Corporation. Verilog is a trademark of Cadence Design Systems, Inc.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information in this document is current as of June, 2000. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data

books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products

and/or types are available in every country. Please check with an NEC sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

### MAJOR REVISIONS IN THIS EDITION

| Page                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Throughout                                                                                                                                                                                                                                       | <ul> <li>Change of family name from "CB-C9 Family VX/VM Type" to "CB-9 Family VX/VM Type".</li> <li>Modification of glossary entry (change from "mega-function" to "core")</li> </ul>                                                                                                                                          |  |

| pp. 50, 51  Table 3-6. DC Characteristics (V <sub>DD</sub> = 3.3 ± 0.3 V, T <sub>A</sub> = -40 to +85°C)  • Addition of TTL 5 V tolerant buffer (18 mA type, 24 mA type) specification values to Low-leve current and High-level output current. |                                                                                                                                                                                                                                                                                                                                |  |

| p. 65                                                                                                                                                                                                                                            | Table 4-1. Power Consumption by Each Input Buffer  • Addition of block type                                                                                                                                                                                                                                                    |  |

| p. 66                                                                                                                                                                                                                                            | Table 4-2. Power Consumption by Output Buffers  • Addition of PCI interface block specification values                                                                                                                                                                                                                         |  |

| pp. 69 to 71                                                                                                                                                                                                                                     | 4.3.4 Detailed estimation of internal circuit power consumption  • Modification of Power consumption in internal cells                                                                                                                                                                                                         |  |

| p. 113                                                                                                                                                                                                                                           | <ul> <li>Table 4-14. SSO Pin Conversion Coefficients</li> <li>Addition of 3.0 mA type specification values to TTL 5 V tolerant buffer (low noise).</li> <li>Addition of 3.0 mA type and 6.0 mA type specification values to 5 V buffer (low noise).</li> </ul>                                                                 |  |

| p. 126, 127                                                                                                                                                                                                                                      | <ul> <li>5.1.2 Core control pins</li> <li>Deletion of description about functional cells that cause no problems even during Hi-Z input from (2) Use of control pins (b) Countermeasures against high-impedance output.</li> <li>Modification of Figure 5-4. Example of Countermeasure against High-Impedance Output</li> </ul> |  |

| p. 153 in the previous edition                                                                                                                                                                                                                   | Deletion of 6.3.3 "Use prohibited" status of flip-flops                                                                                                                                                                                                                                                                        |  |

| pp. 167, 168                                                                                                                                                                                                                                     | 6.6.2 Prevention of High impedance  • Modification of description about cautions on bus line configuration.  • Modification of Figure 6-22. Configuration Examples of Circuits for Preventing High Impedance of Internal Bus                                                                                                   |  |

| p. 168                                                                                                                                                                                                                                           | Addition of 6.6.4 Cautions regarding occurrence of overcurrent at power application                                                                                                                                                                                                                                            |  |

| pp. 195 to 218<br>in the previous<br>edition                                                                                                                                                                                                     | Deletion of CHAPTER 8 TEST PATTERN DESIGN                                                                                                                                                                                                                                                                                      |  |

| p. 212                                                                                                                                                                                                                                           | 9.5.1 Signal standard for PCI local bus  • Addition of description about placement of additional power supply.                                                                                                                                                                                                                 |  |

| pp. 241 to 244<br>in the previous<br>edition                                                                                                                                                                                                     | Deletion of CHAPTER 11 CREATION OF DEBUGGER                                                                                                                                                                                                                                                                                    |  |

The mark ★ shows major revised points.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

### **NEC Electronics Italiana s.r.l.**

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845

Fax: 040-2444580

### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130 Tel: 65-253-8311

Fax: 65-250-3583

### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

### NEC do Brasil S.A.

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil Tel: 55-11-6465-6810

Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

J99.1

### **PREFACE**

This manual describes various restrictions and cautions concerning LSI design using NEC's CB-9 Family (VX/VM Type) of high-speed, highly integrated CMOS cell-based ICs.

LSI designers should read this manual carefully to help ensure smooth progress in LSI design.

Be sure to remain within the specifications described in this manual (including general items, cautions, and restrictions). Failure to do so may result in poor quality, poor performance, or operation faults in LSI products.

### **Related documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

### ● CB-9 Family VX/VM Type

| CB-9 Family VX/VM Type Design Manual                                                         | (This manual) |

|----------------------------------------------------------------------------------------------|---------------|

| CB-9 Family VX/VM Type Block Library (CMOS 3.3 V)                                            | (A12793E)     |

| CB-9 Family VX Type Block Library (CMOS 2.0 V)                                               | (A12794E)     |

| CB-9 Family VX/VM Type (TTL 3.3 V) Block Library                                             | (A14710E)     |

| CB-9 Family VX/VM Type Memory Macro (Compiled Type) Design Manual                            | (A12982E)     |

| CB-9 Family VX/VM Type Memory Macro (Fixed Type) Design Manual                               | (A13899E)     |

| CB-9 Family VX/VM Type Analog Macro (High-Speed D/A Converter) Design Manual                 | (A13820E)     |

| CB-9 Family VX/VM Type Analog Macro (PLL) Design Manual                                      | (A13947E)     |

| <ul> <li>CB-9 Family VX/VM Type Analog Macro (General-Purpose A/D, D/A Converter)</li> </ul> |               |

| Design Manual                                                                                | (A14021E)     |

| CB-9 Family VX/VM Type CPU, Peripheral Design Manual                                         | (A14304E)     |

| CB-9 Family VX/VM Type NX16550L Core User's Manual                                           | (A13258E)     |

| CB-9 Family VX/VM Type Core Library CPU Core, Memory Controller Design Manual                | (A13195E)     |

|                                                                                              |               |

### ● OPENCAD™

• Design For Test User's Manual (A14357E)

To obtain the latest documents when designing, contact an NEC sales office or a distributor.

### **CONTENTS**

| CHAPT | ER 1 GENERAL                                                                       | 19 |

|-------|------------------------------------------------------------------------------------|----|

| 1.1   | Features                                                                           | 19 |

|       | 1.1.1 Features of VX/VM types                                                      | 20 |

| 1.2   | Internal Configuration of Cell-Based ICs                                           | 23 |

|       | 1.2.1 Chip configuration                                                           | 23 |

|       | 1.2.2 Chip layout                                                                  | 24 |

| 1.3   | On-chip Transistor Configuration                                                   | 25 |

| 1.4   | Connection between 3.3-V Line and 5-V Line                                         | 26 |

| 1.5   | QFP Package                                                                        | 27 |

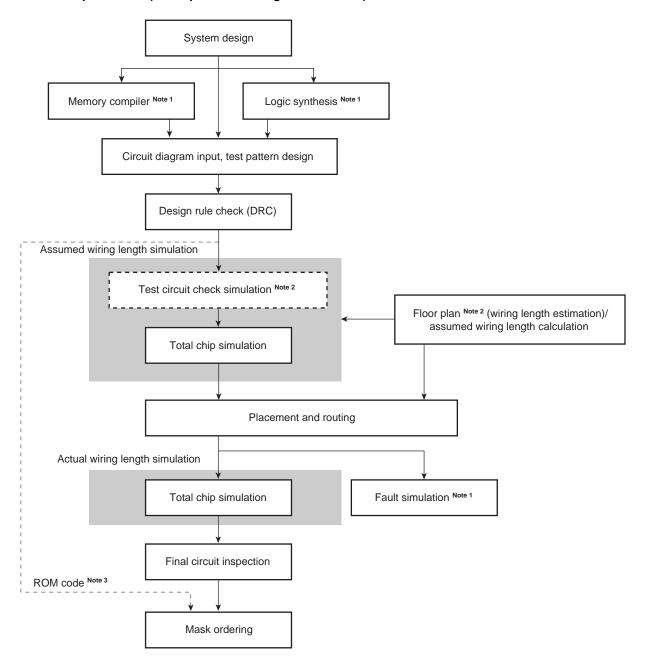

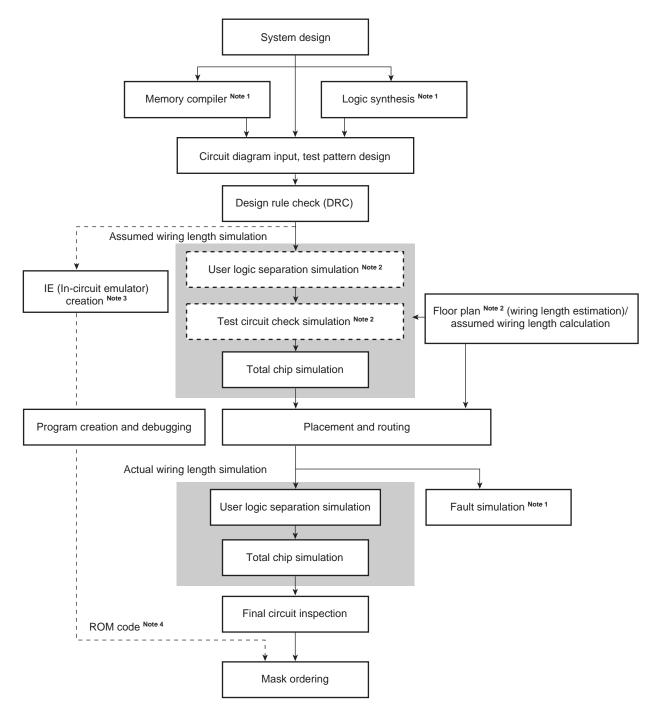

| 1.6   | Development Flow                                                                   | 28 |

|       | 1.6.1 Development flow (for chips with user logic + ROM/RAM)                       | 28 |

|       | 1.6.2 Development flow (for chips with CPU and CPU peripherals)                    | 29 |

|       | 1.6.3 Description of development flow                                              | 30 |

| CHAPT | ER 2 INTRODUCTION TO CELL-BASED ICs                                                | 31 |

| 2.1   | Estimation of Circuit Size                                                         | 32 |

|       | 2.1.1 Determination of step size                                                   | 32 |

|       | 2.1.2 Cautions concerning estimation of number of grid utilized                    | 35 |

|       | 2.1.3 Cautions concerning implementation of cores (memory and other large macros)  | 35 |

| 2.2   | Package Selection                                                                  | 35 |

| 2.3   | Power Consumption Check                                                            | 39 |

| 2.4   | Pin Layout                                                                         | 40 |

| 2.5   | I/O Interface                                                                      | 42 |

|       | 2.5.1 Input block types                                                            | 42 |

|       | 2.5.2 Output block types                                                           | 43 |

| СНАРТ | ER 3 PRODUCT SPECIFICATIONS                                                        | 45 |

| 3.1   | Terminology                                                                        | 45 |

| 3.2   | Absolute Maximum Ratings                                                           |    |

| 3.3   | Recommended Operating Conditions                                                   | 48 |

| 3.4   | DC Characteristics                                                                 |    |

| 3.5   | Pull-up/Pull-down Resistance Values                                                | 52 |

| 3.6   | AC Characteristics                                                                 | 53 |

| 3.7   | Pin Capacitance                                                                    | 54 |

| СНАРТ | ER 4 ESTIMATION METHODS FOR CHARACTERISTIC VALUES                                  | 57 |

| 4.1   | Estimation of Static Current Consumption                                           | 57 |

|       | 4.1.1 Estimation of static current consumption                                     | 57 |

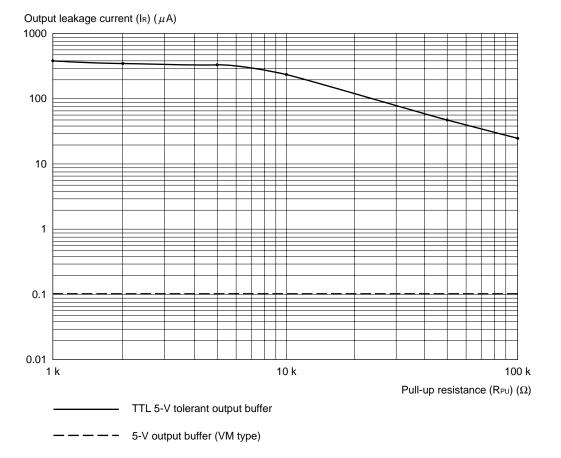

|       | 4.1.2 Output leakage current (IR)                                                  |    |

| 4.2   | Input Through Current                                                              |    |

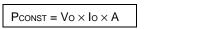

| 4.3   | Power Consumption                                                                  |    |

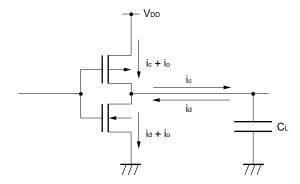

|       | 4.3.1 Cause of power consumption                                                   |    |

|       | 4.3.2 Estimation of entire chip's power consumption                                |    |

|       | 4.3.3 Estimation of the power consumption of functional cells and interface blocks | 64 |

|       | 4.3.4 Detailed estimation of internal circuit power consumption                    | 69 |

|      | 4.3.5 | Compensation method for changes in power supply and ambient temperature specifications | 72    |

|------|-------|----------------------------------------------------------------------------------------|-------|

|      | 4.3.6 | Determination of power consumption                                                     | 73    |

| 4.4  | Propa | ngation Delay Times                                                                    | 82    |

|      | 4.4.1 | Precision in delay times                                                               | 82    |

|      | 4.4.2 | Calculation of delay times                                                             | 83    |

|      | 4.4.3 | Variation in delay times                                                               | 85    |

| 4.5  | Outpu | ut Buffer Characteristics                                                              | 88    |

|      | 4.5.1 | Output buffer rise and fall times                                                      | 88    |

|      | 4.5.2 | Recommended load capacitance range for output buffers                                  | 93    |

|      | 4.5.3 | Maximum operating frequency of output buffers                                          | 94    |

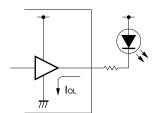

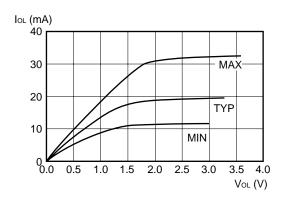

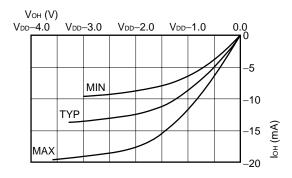

|      | 4.5.4 | Output buffer output currents (IoL, Ioн)                                               | 101   |

| 4.6  | Simul | taneous Switching Limits of Output Buffers                                             | . 109 |

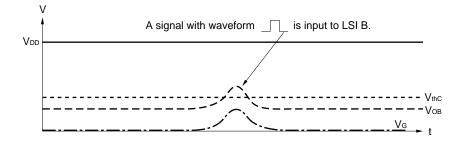

|      | 4.6.1 | Misoperation caused by simultaneous switching                                          | 109   |

|      | 4.6.2 | SSO factors                                                                            | 111   |

|      | 4.6.3 | Determining number of SSO                                                              | 111   |

|      | 4.6.4 | Method for Judging SSO limits                                                          | 112   |

|      | 4.6.5 | Cautions on pin layout                                                                 | 114   |

|      | 4.6.6 | Handling when SSO limit is exceeded                                                    | 114   |

|      |       |                                                                                        |       |

| CHAP | TER 5 | SYSTEM DESIGN                                                                          | . 115 |

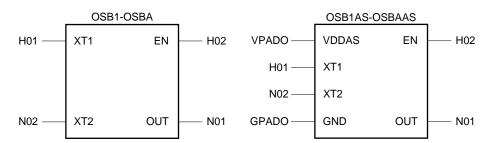

| 5.1  | Circu | it Design for Testing                                                                  | . 115 |

|      | 5.1.1 | Circuit for core separate tests                                                        | 115   |

|      | 5.1.2 | Core control pins                                                                      | 125   |

|      | 5.1.3 | User logic circuit design for testing                                                  | 127   |

| 5.2  | Circu | it Design for Debugger                                                                 | . 127 |

| 5.3  | Circu | it Design for Total Chip Simulation                                                    | . 127 |

| 5.4  | Desig | n of Clock Lines                                                                       | . 128 |

|      | 5.4.1 | Asynchronous circuits and synchronous circuits                                         |       |

|      | 5.4.2 | Clock skew                                                                             | 134   |

|      | 5.4.3 | Enable control                                                                         | 136   |

|      | 5.4.4 | Clock tree synthesis                                                                   | 137   |

|      | 5.4.5 | Setting and resetting latches and flip-flops                                           |       |

| 5.5  |       | Logic Circuit Design for Layout                                                        |       |

| 5.6  | Modu  | lar Design                                                                             | . 147 |

| _    |       |                                                                                        |       |

|      |       | USER LOGIC DESIGN                                                                      |       |

| 6.1  |       | Circuit Configuration                                                                  |       |

|      | 6.1.1 | Use of input and output buffers                                                        |       |

|      | 6.1.2 | Handling of unused pins                                                                |       |

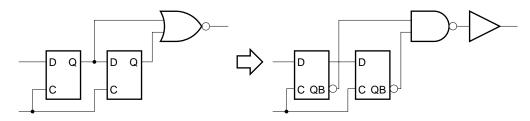

|      | 6.1.3 | Restriction on fan-out capacity                                                        |       |

| _    | 6.1.4 | Prohibition of wired logic                                                             |       |

| 6.2  |       | bition of Differential Circuits                                                        |       |

| 6.3  |       | atches and Loop Circuits                                                               |       |

|      | 6.3.1 | RS latches                                                                             |       |

|      | 6.3.2 | Loop circuits                                                                          |       |

| 6.4  |       | ons Concerning High-Speed Circuit Configurations                                       |       |

| 6.5  | -     | Time Margin                                                                            | . 154 |

|      |       |                                                                                        |       |

|            | 6.5.2 Delay time margin calculation method (asynchronous circuits)                         | 156 |

|------------|--------------------------------------------------------------------------------------------|-----|

|            | 6.5.3 Delay time margin calculation method (high-speed circuits)                           | 157 |

|            | 6.5.4 Minimum pulse width                                                                  | 159 |

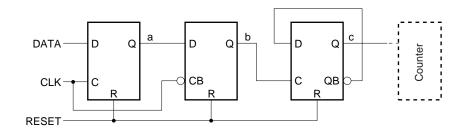

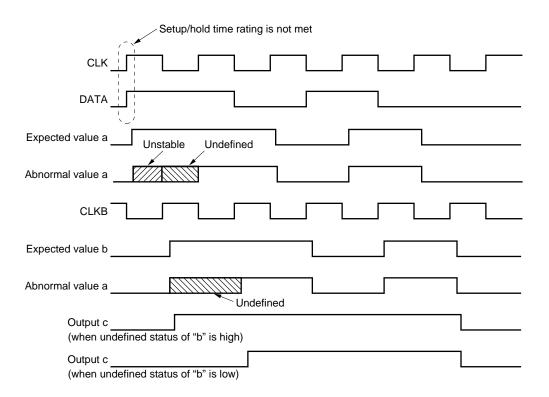

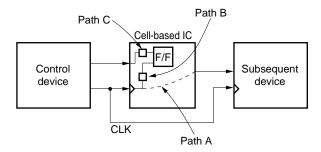

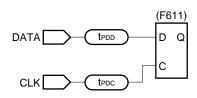

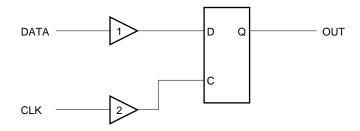

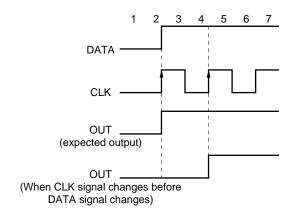

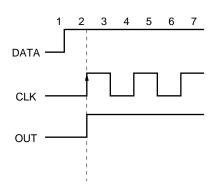

|            | 6.5.5 Metastable                                                                           | 160 |

|            | 6.5.6 Critical path                                                                        | 164 |

|            | 6.5.7 Conditions for securing operating margin                                             | 166 |

| 6.6        | Configuration of Internal Buses                                                            | 167 |

|            | 6.6.1 Internal bus configuration method                                                    | 167 |

|            | 6.6.2 Prevention of high impedance                                                         | 167 |

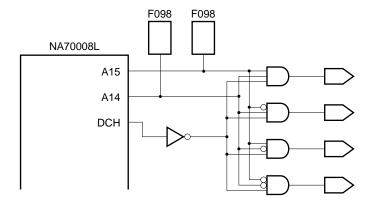

|            | 6.6.3 Restrictions when using bus holder (F098) with internal bus                          | 168 |

|            | 6.6.4 Cautions regarding occurrence of overcurrent at power application                    | 168 |

| 6.7        | Testability Considerations                                                                 | 169 |

|            | 6.7.1 Initialization of flip-flops                                                         | 169 |

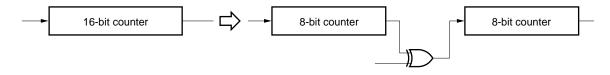

|            | 6.7.2 Division of counter                                                                  | 169 |

|            | 6.7.3 Addition of test pins and division of circuits                                       | 170 |

| 6.8        | Racing and Spike Noise                                                                     | 170 |

|            | 6.8.1 Racing (conflict)                                                                    | 170 |

|            | 6.8.2 Spike noise                                                                          | 172 |

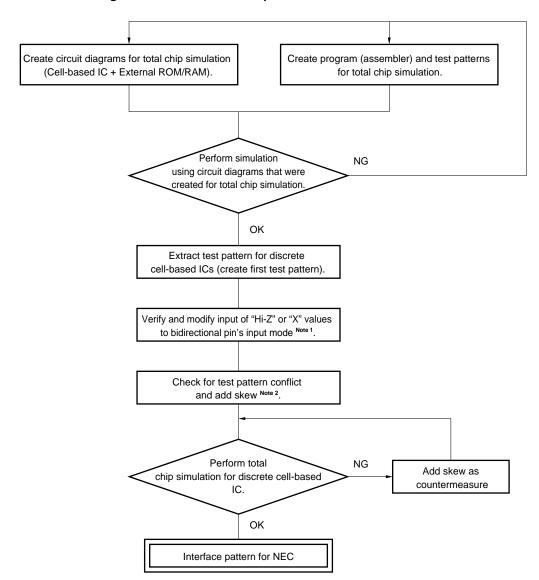

| 7.1<br>7.2 | Total Chip Simulation Flow                                                                 | 176 |

| 7.3        | Creation of Circuit Diagram for Total Chip Simulation                                      |     |

| 7.4        | Creation of Program and Test Pattern for Total Chip Simulation                             |     |

|            | 7.4.1 Program and test pattern for total chip simulation                                   |     |

|            | 7.4.2 Cautions concerning creation of programs and test patterns for total chip simulation |     |

|            | 7.4.3 Test program and test pattern examples                                               |     |

| 7.5        | Execution of Simulation Using Circuit Diagram for Total Chip Simulation                    |     |

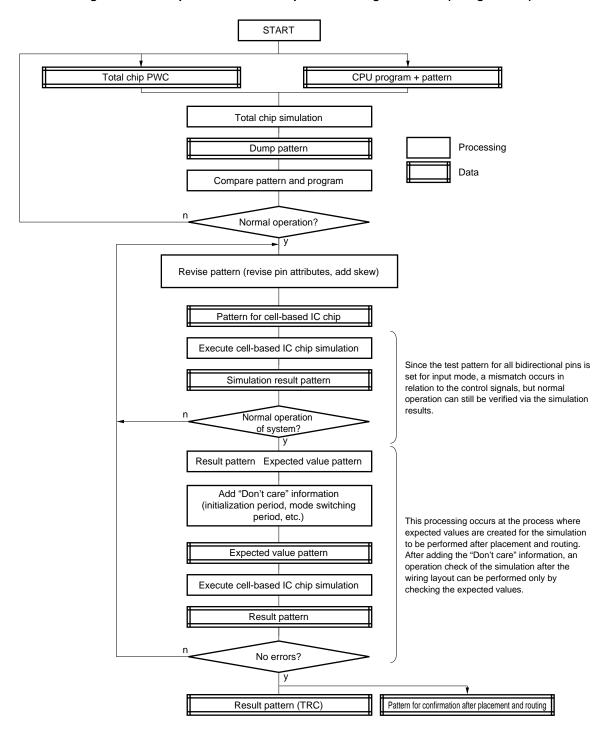

| 7.6        | Extract Test Pattern for Discrete Cell-Based IC                                            |     |

| 7.7        | Verify and Modify Input of "Hi-Z" or "X" Values to Bidirectional Pin's Input Mode          |     |

| 7.8        | Check for Test Pattern Conflict and Add Skew                                               |     |

| 7.9        | Total Chip Simulation Using Discrete Cell-Based IC                                         | 191 |

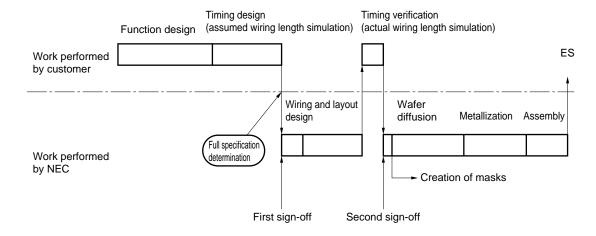

|            | ER 8 SIGN-OFF CONDITIONS AND DATA TO BE PASSED                                             |     |

| 8.1        | Basic Conditions for Sign-offs                                                             |     |

| 8.2        | Data Required for Interface                                                                | 194 |

|            | ER 9 MULTI-FUNCTION BLOCKS                                                                 |     |

| 9.1        | 3.3-V, 5-V Interface Blocks                                                                |     |

|            | 9.1.1 Input buffers                                                                        |     |

|            | 9.1.2 Output buffers                                                                       |     |

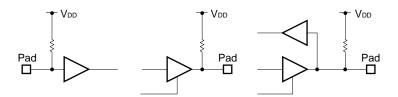

| 9.2        | Input/Output/Bidirectional Buffers with On-Chip Pull-up/Pull-down Resistors                |     |

| 9.3        | Oscillator Block                                                                           |     |

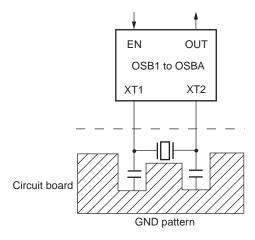

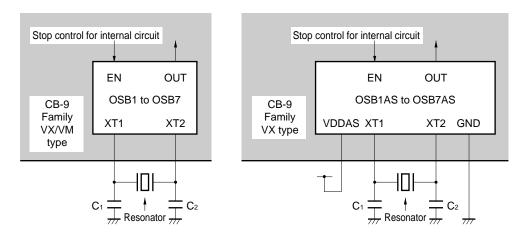

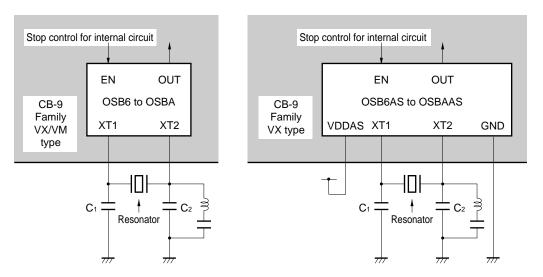

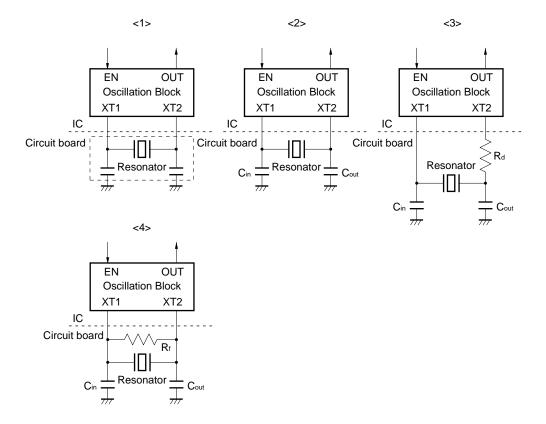

|            | 9.3.1 Overview of oscillator block                                                         | 202 |

|            | 9.3.2 Cautions on use of oscillator blocks                                                 | 203 |

|            | 9.3.3 Cautions on oscillator configuration                                                 | 204 |

|            | 9.3.4 Oscillator block configuration examples                                              | 205 |

|            | 9.3.5 Resonator and circuit configuration                                                  | 206 |

|            |                                                                                            |     |

| 9.4    | GTL ( | Under Development)                                  | 208 |

|--------|-------|-----------------------------------------------------|-----|

|        | 9.4.1 | Electrical characteristics                          | 208 |

|        | 9.4.2 | Pin layout                                          | 209 |

|        | 9.4.3 | Connection rules                                    | 210 |

|        | 9.4.4 | Creation of test patterns                           | 210 |

| 9.5    | PCI L | ocal Bus Buffer                                     | 211 |

|        | 9.5.1 | Signal standard for PCI local bus                   | 211 |

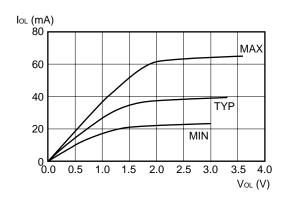

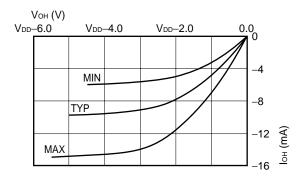

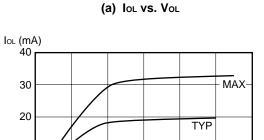

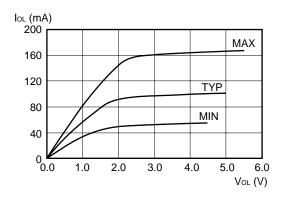

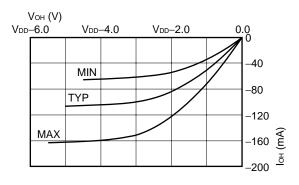

|        | 9.5.2 | PCI buffer's output current (IoL, IoH)              | 213 |

|        | 9.5.3 | Electrical characteristics                          | 214 |

| 9.6    | Scan  | Path Test Block                                     | 214 |

| APPENI | DIX A | LISTS OF INPUT/OUTPUT PINS AND POWER SUPPLY PINS IN |     |

|        |       | PACKAGES                                            | 215 |

| A.1    | VX T  | /pe                                                 | 215 |

|        | A.1.1 | When using 3.3-V single power supply pins           |     |

|        | A.1.2 | When using internal 2.0-V type power supply pins    |     |

| A.2    | VM T  | ype                                                 |     |

|        | ,     | / I' -                                              |     |

# LIST OF FIGURES (1/3)

| Figure | e No. Title                                                                                 | Page |

|--------|---------------------------------------------------------------------------------------------|------|

| 1-1    | Interface and Supply Voltages                                                               | 20   |

| 1-2    | Buffer Layout Example                                                                       |      |

| 1-3    | Equivalent Circuits                                                                         |      |

| 1-4    | Section View of QFP Package                                                                 |      |

| 1-5    | Section View of QFP with Heat Spreader                                                      |      |

| 1-6    | Section View of TAB in QFP                                                                  |      |

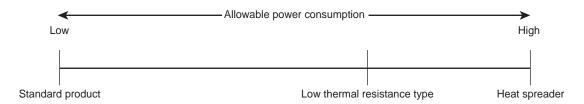

| 2-1    | Deletionship between Allewahle Dewer Consumption and Various OFDs                           | 20   |

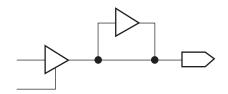

|        | Relationship between Allowable Power Consumption and Various QFPs  Buffers with Bus Holders |      |

| 2-2    | Bullers with Bus Holders                                                                    | 44   |

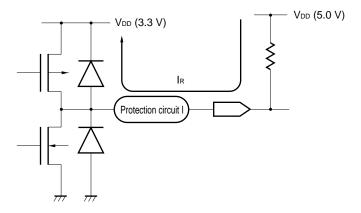

| 4-1    | Flow Route of Output Leakage Current (IR)                                                   |      |

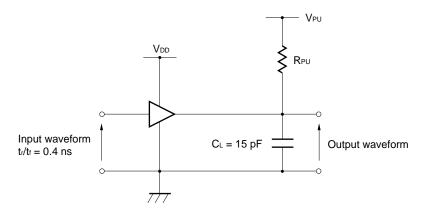

| 4-2    | Measurement Circuit                                                                         | 58   |

| 4-3    | Output Leakage Current                                                                      | 59   |

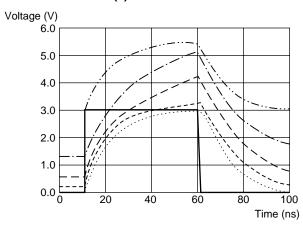

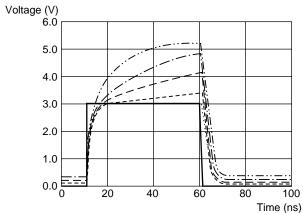

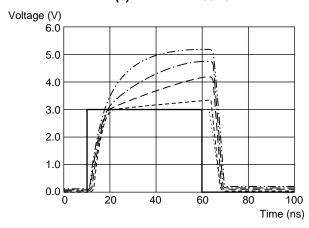

| 4-4    | 5-V Output Buffer Output Waveform                                                           | 60   |

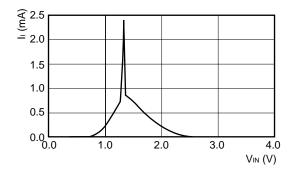

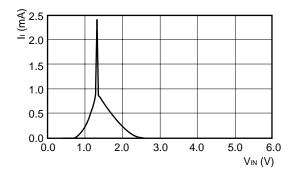

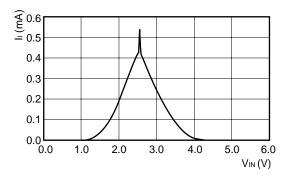

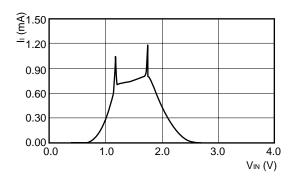

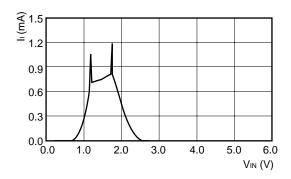

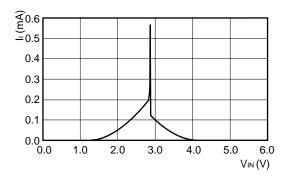

| 4-5    | LVTTL Input Through Current (3.3-V Input)                                                   | 61   |

| 4-6    | LVTTL Input Through Current (3.3-V Schmitt Input)                                           | 61   |

| 4-7    | TTL 5-V Tolerant Input Through Current (5-V Input)                                          | 61   |

| 4-8    | TTL 5-V Tolerant Input Through Current (5-V Schmitt Input)                                  | 61   |

| 4-9    | 5-V Input Through Current                                                                   | 61   |

| 4-10   | 5-V Input Through Current (Schmitt Input)                                                   | 61   |

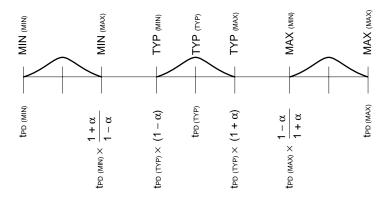

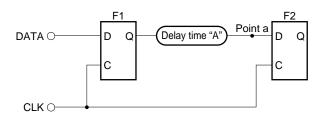

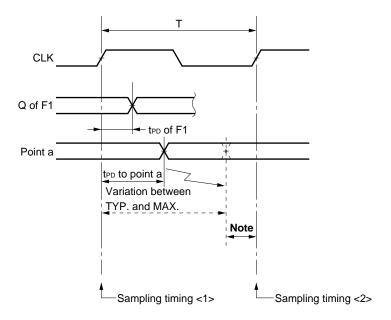

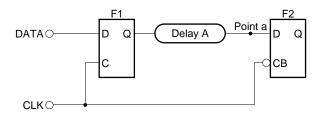

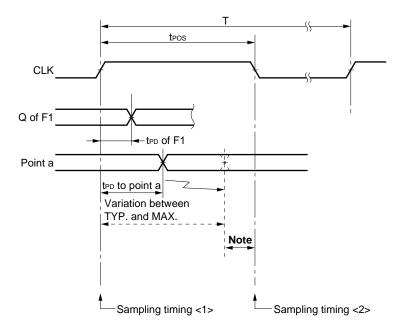

| 4-11   | tpd Variations                                                                              | 87   |

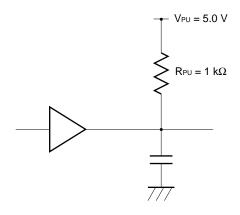

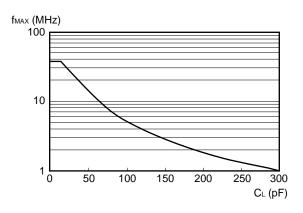

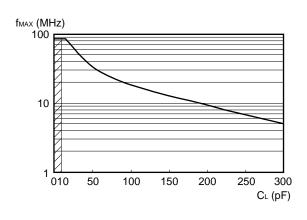

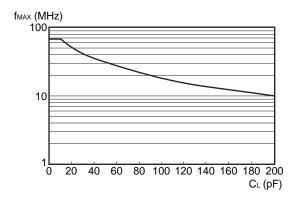

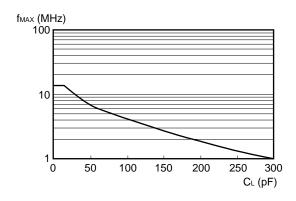

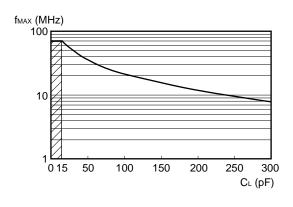

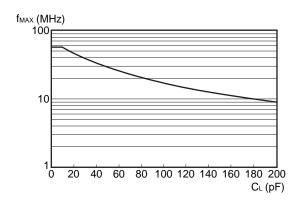

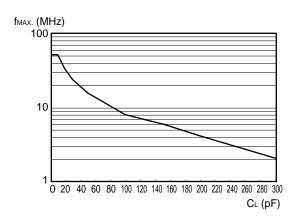

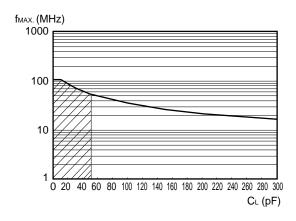

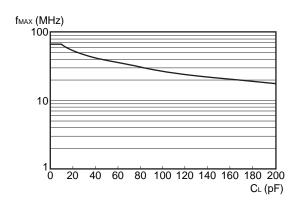

| 4-12   | fMAX. vs. C∟ Restriction (LVTTL Interface, Normal Type)                                     | 95   |

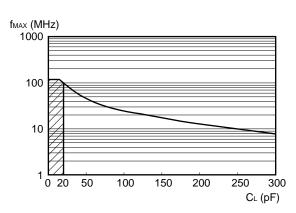

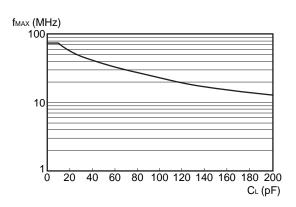

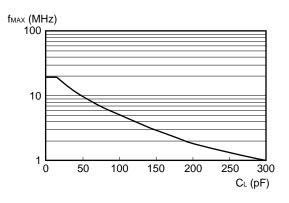

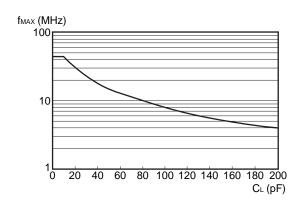

| 4-13   | fmax. vs. CL Restriction (LVTTL Interface, Low Noise)                                       | 96   |

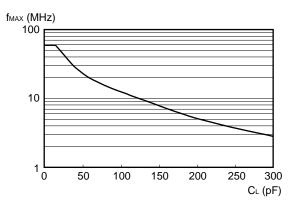

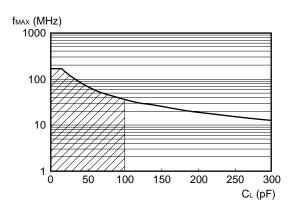

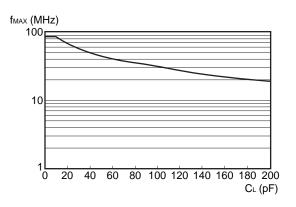

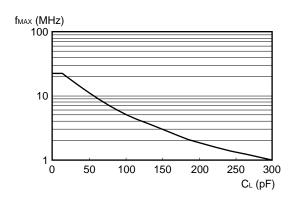

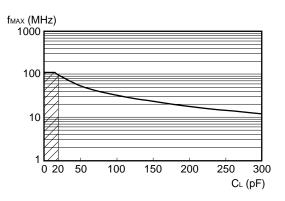

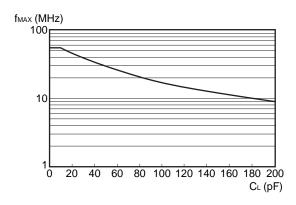

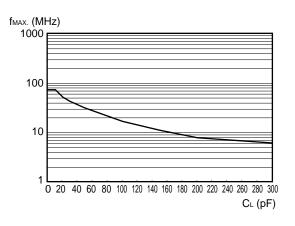

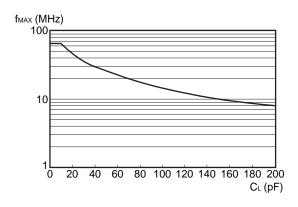

| 4-14   | fmax. vs. CL Restriction (TTL 5-V Tolerant Interface, Normal Type)                          | 97   |

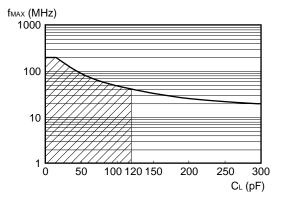

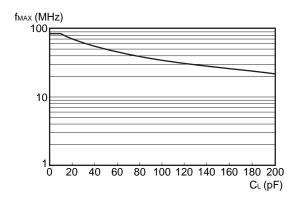

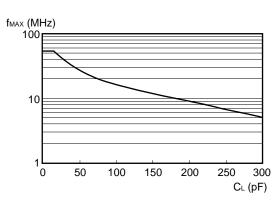

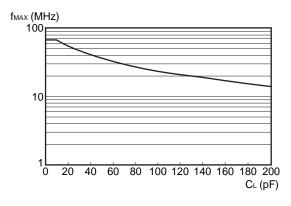

| 4-15   | fMAX. vs. CL Restriction (TTL 5-V Tolerant Interface, Low Noise)                            | 98   |

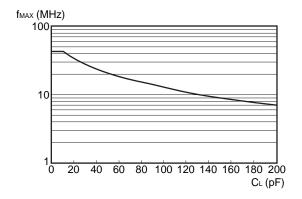

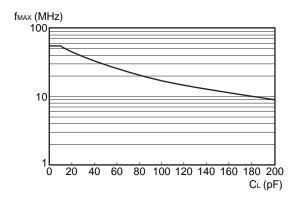

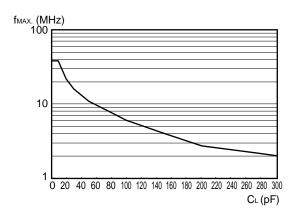

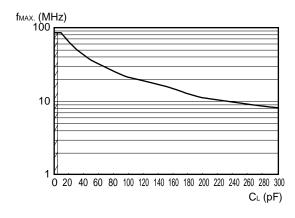

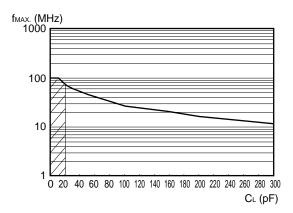

| 4-16   | fMAX. vs. C∟ Restriction (5-V Interface, Normal Type)                                       | 99   |

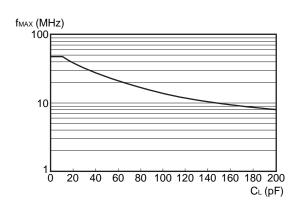

| 4-17   | fmax. vs. C <sub>L</sub> Restriction (5-V Interface, Low Noise)                             | 100  |

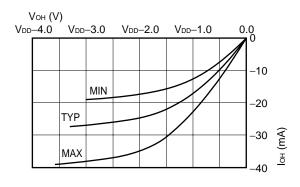

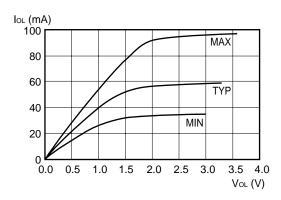

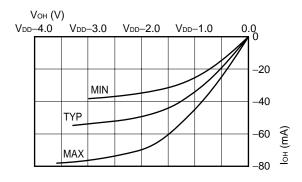

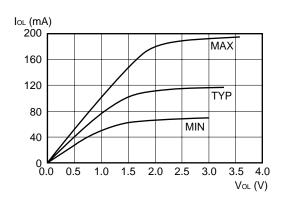

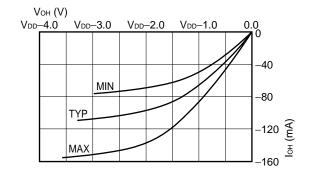

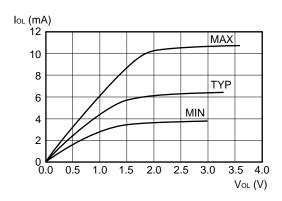

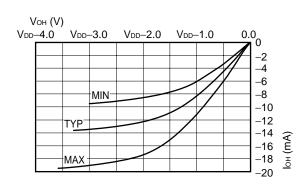

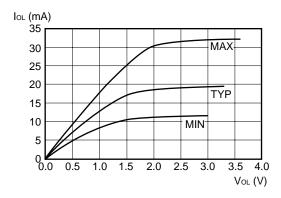

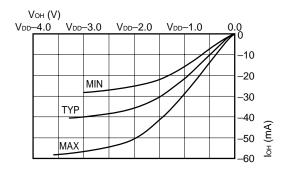

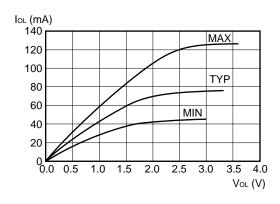

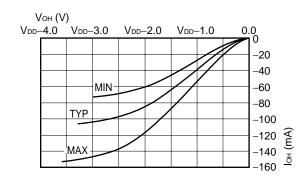

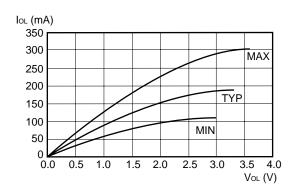

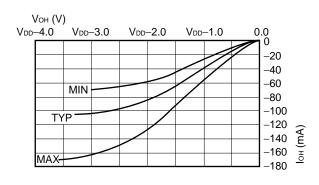

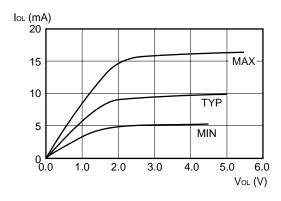

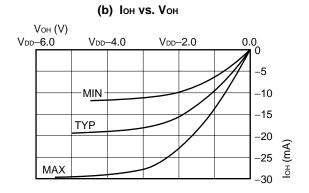

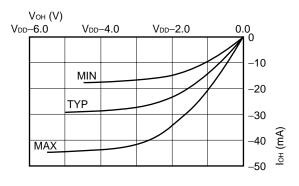

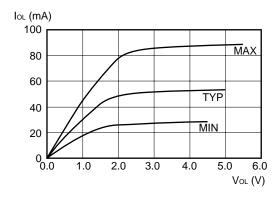

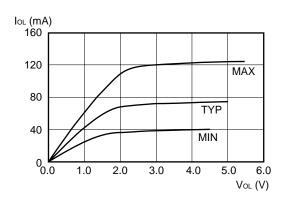

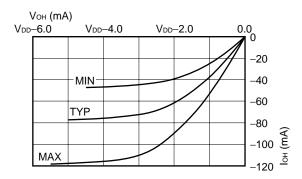

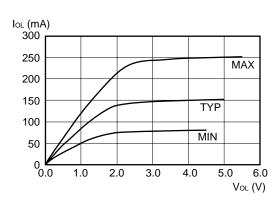

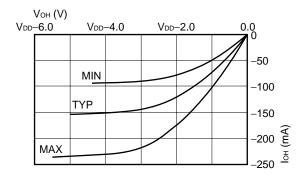

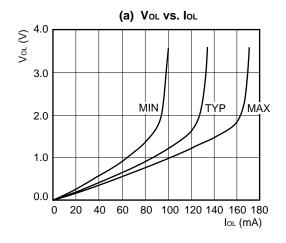

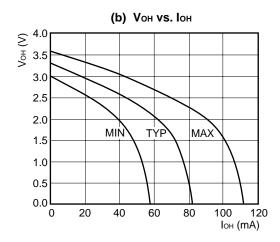

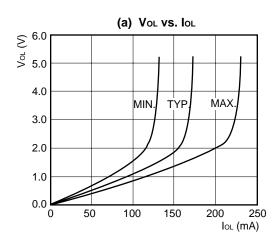

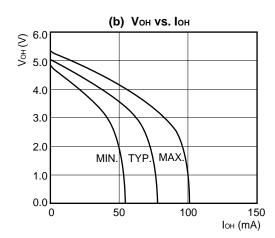

| 4-18   | lo vs. Vo                                                                                   | 102  |

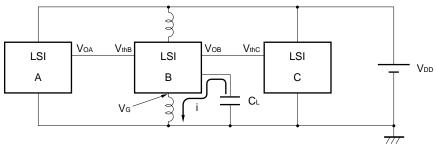

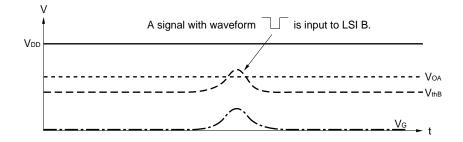

| 4-19   | Misoperation Due to Simultaneous Switching                                                  | 110  |

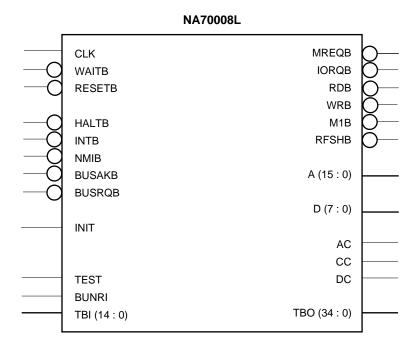

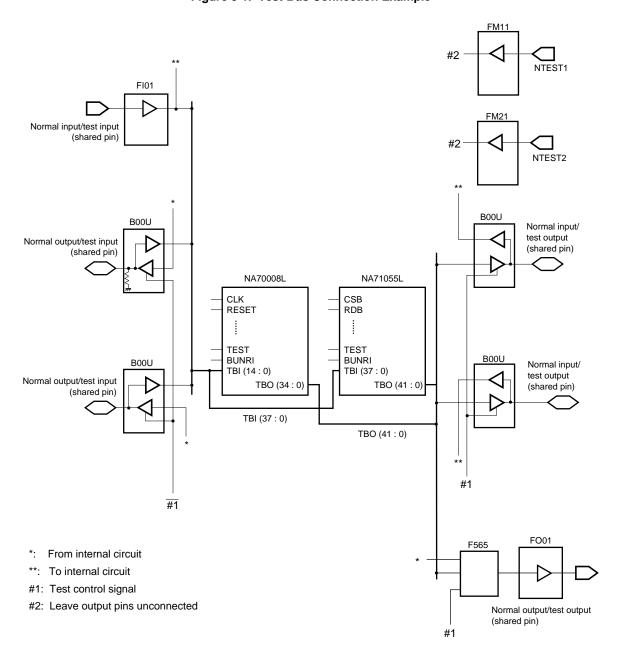

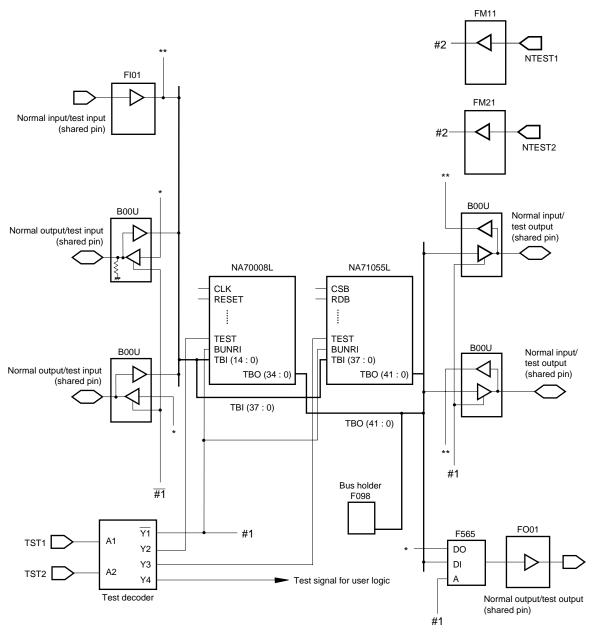

| 5-1    | Test Bus Connection Example                                                                 | 121  |

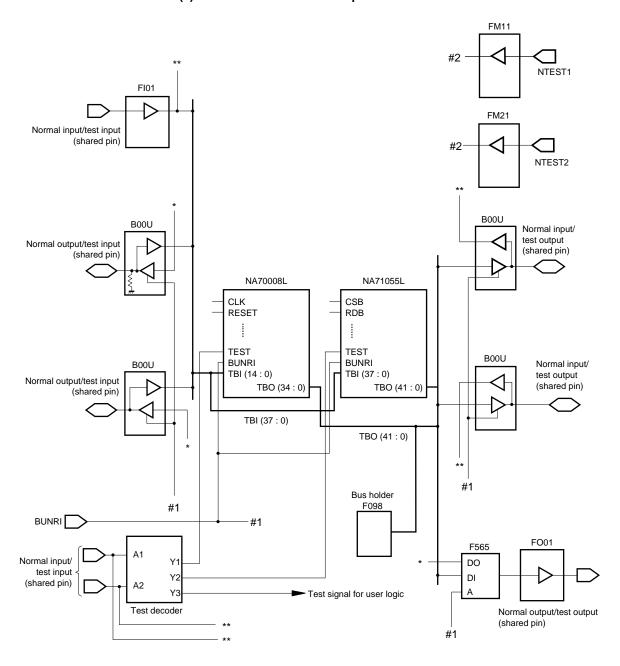

| 5-2    | Test Bus Control Circuit Connection Example                                                 | 123  |

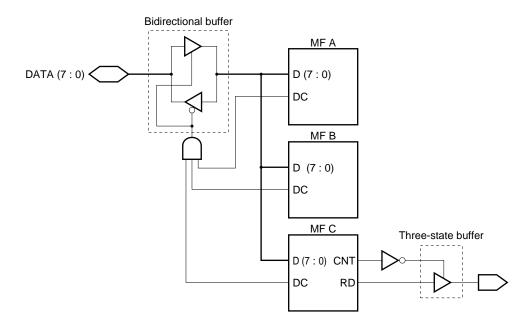

| 5-3    | Control of Bidirectional Buffer or Three-state Buffer                                       | 126  |

| 5-4    | Example of Countermeasure against High-Impedance Output                                     | 127  |

| 5-5    | Clock Skew                                                                                  |      |

| 5-6    | Clock Layout                                                                                | 130  |

| 5-7    | Example of Multi-phase Clock                                                                |      |

| 5-8    | Setup/Hold Times for Latches                                                                |      |

| 5-9    | Division of Combination Circuit                                                             |      |

| 5-10   | Addition Circuit (Using Three-Phase Clock)                                                  |      |

| 5-11   | Addition Circuit (Using Single-Phase Clock)                                                 |      |

| 5-12   | Common Circuit in 74LS Circuit Diagram                                                      |      |

### LIST OF FIGURES (2/3)

| Figure | No. Title                                                                        | Page |

|--------|----------------------------------------------------------------------------------|------|

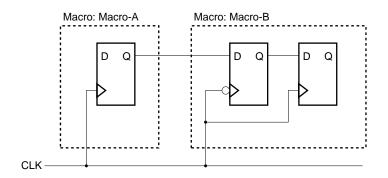

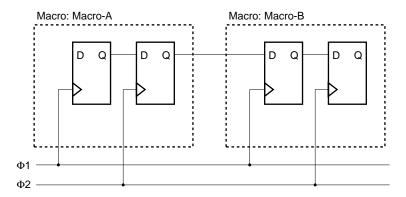

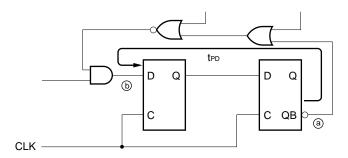

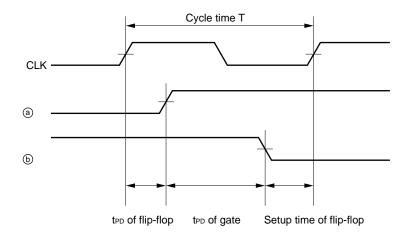

| 5-13   | Circuit Using Two-phase Clock                                                    | 134  |

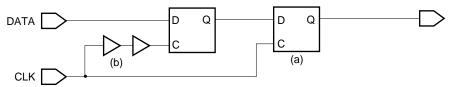

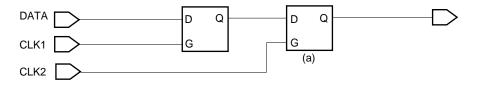

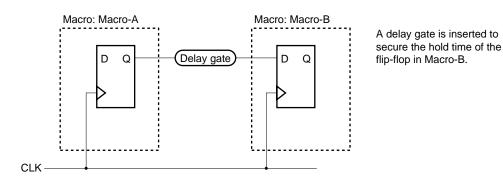

| 5-14   | Countermeasures for Clock Lines between Macros                                   |      |

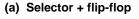

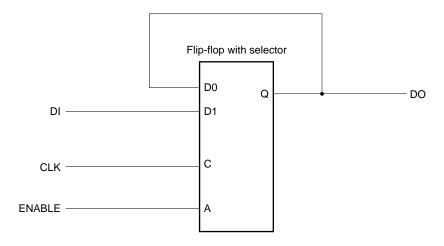

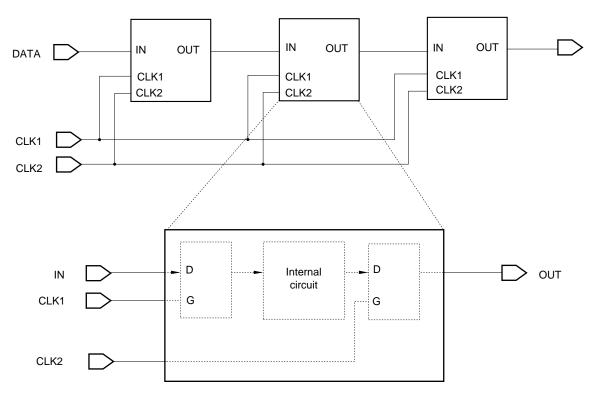

| 5-15   | Data Enable Flip-flop                                                            |      |

| 5-16   | Configuration Example Using Clock Enable                                         |      |

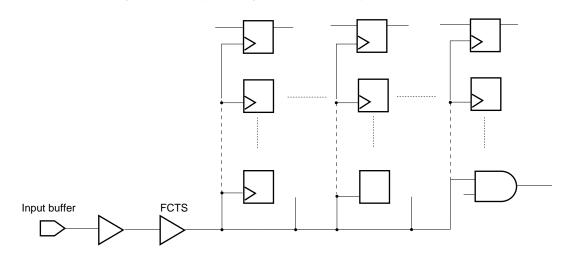

| 5-17   | Layout Image for Clock Tree Synthesis                                            |      |

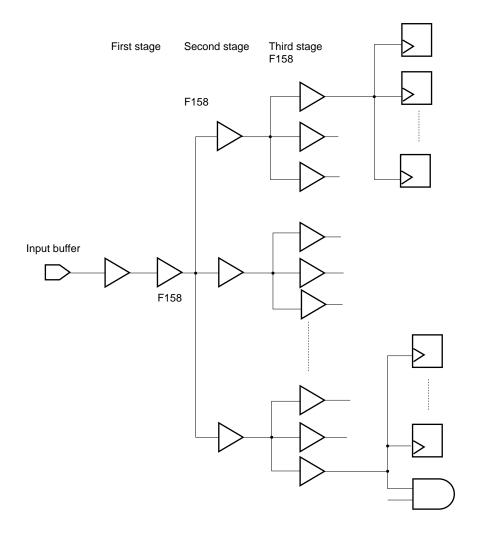

| 5-18   | Clock Tree Synthesis                                                             |      |

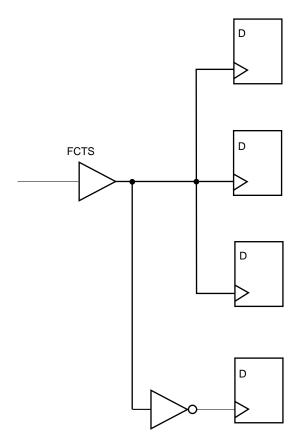

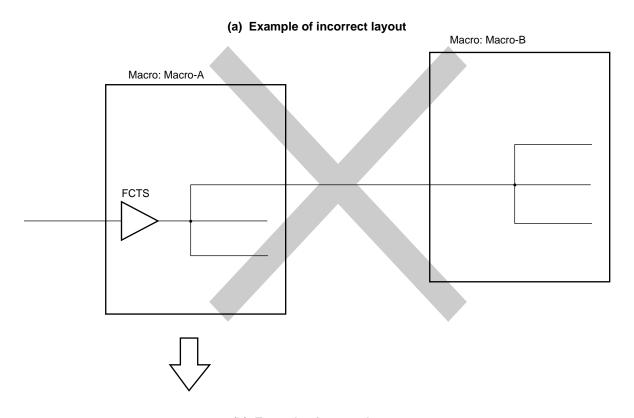

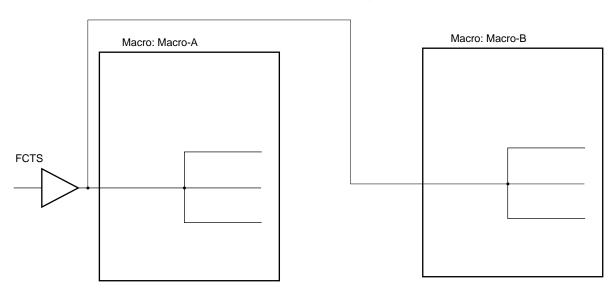

| 5-19   | FCTS Layout Restriction                                                          |      |

| 5-20   | FCTS Layout Diagram                                                              |      |

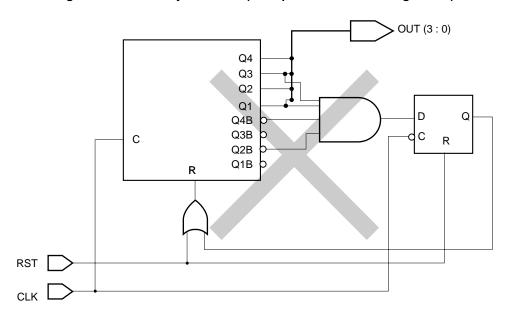

| 5-21   | Divide by 5 Counter (Example of Correct Configuration)                           |      |

| 5-22   | Divide by 5 Counter (Example of Incorrect Configuration)                         |      |

| 5-23   | Standardization of Interface between Macros                                      |      |

| 5-24   | Modular Design                                                                   |      |

|        | · ·                                                                              |      |

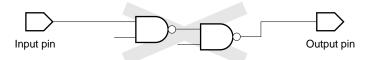

| 6-1    | Basic Circuit Configuration                                                      | 149  |

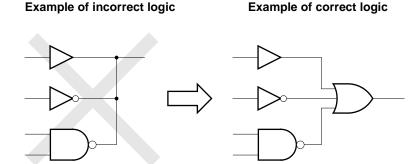

| 6-2    | Prohibition of Wired Logic                                                       | 150  |

| 6-3    | Prohibition of Differential Circuits                                             | 151  |

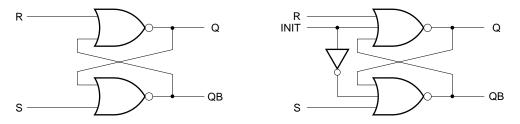

| 6-4    | Asynchronous RS Latch                                                            | 151  |

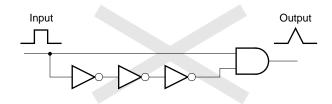

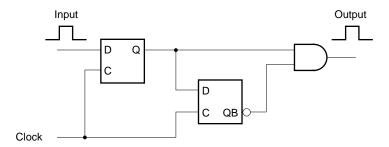

| 6-5    | Loop Circuit                                                                     | 152  |

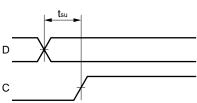

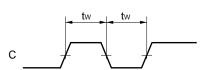

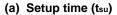

| 6-6    | Setup Time                                                                       | 155  |

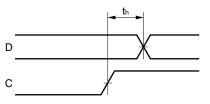

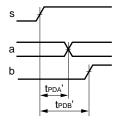

| 6-7    | Hold Time                                                                        | 155  |

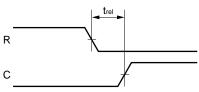

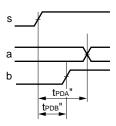

| 6-8    | Release Time                                                                     | 155  |

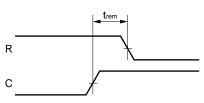

| 6-9    | Removal Time                                                                     | 155  |

| 6-10   | Minimum Pulse Width                                                              | 155  |

| 6-11   | Circuit Example for Delay Time Margin Calculation                                | 156  |

| 6-12   | Estimated Timing                                                                 | 156  |

| 6-13   | In-Phase Clock Circuit Example                                                   | 157  |

| 6-14   | Timing for In-Phase Clock                                                        | 157  |

| 6-15   | Reverse-Phase Clock Circuit Example                                              | 158  |

| 6-16   | Timing for Reverse-Phase Clock                                                   | 158  |

| 6-17   | Estimation of Minimum Pulse Width                                                | 159  |

| 6-18   | Reduction of Pulse Width                                                         | 159  |

| 6-19   | System that Includes Critical Paths                                              | 164  |

| 6-20   | Example of Critical Path between Input and Input                                 | 165  |

| 6-21   | Verification of Setup Time                                                       | 165  |

| 6-22   | Configuration Examples of Circuits for Preventing High Impedance of Internal Bus | 167  |

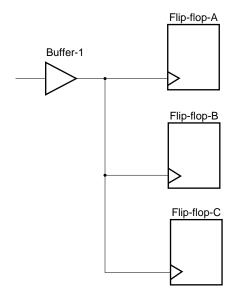

| 6-23   | Initialization of Flip-Flop                                                      | 169  |

| 6-24   | Division of Counter                                                              | 169  |

| 6-25   | Racing                                                                           | 171  |

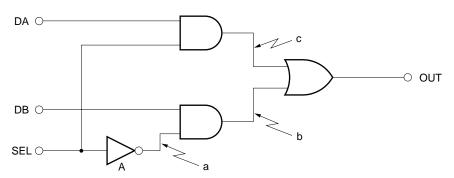

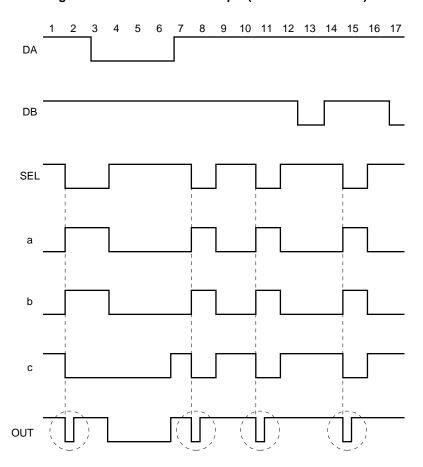

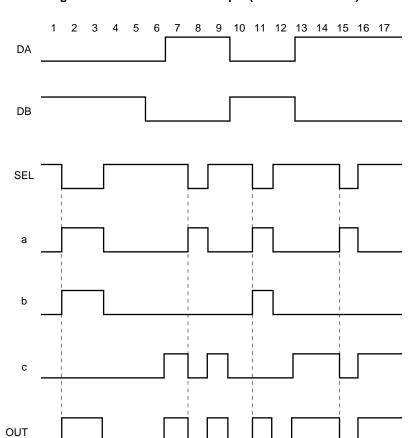

| 6-26   | Data Selector Circuit Example                                                    | 172  |

| 6-27   | Test Pattern Example (Before Modification)                                       | 173  |

| 6-28   | Test Pattern Example (After Modification)                                        | 174  |

# LIST OF FIGURES (3/3)

| Figure | No. Title                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------|------|

|        |                                                                                                  |      |

| 7-1    | Flow of Total Chip Simulation Pattern Generation                                                 | 176  |

| 7-2    | Creation of Circuit Diagram for Total Chip Simulation                                            | 178  |

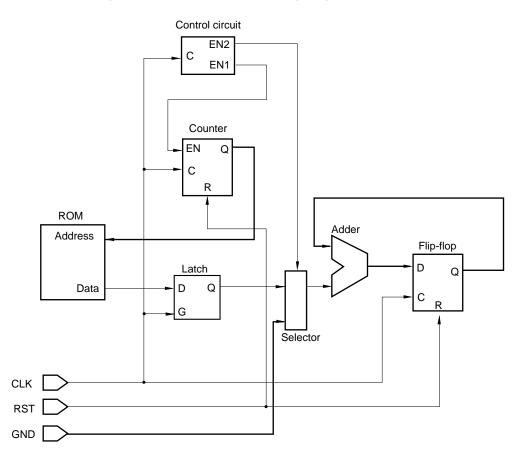

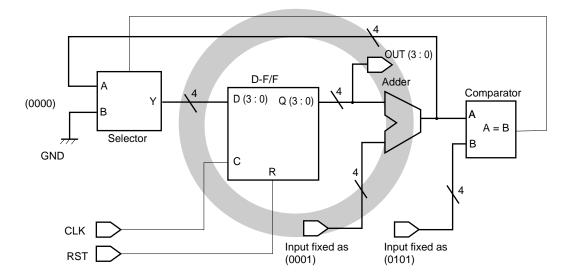

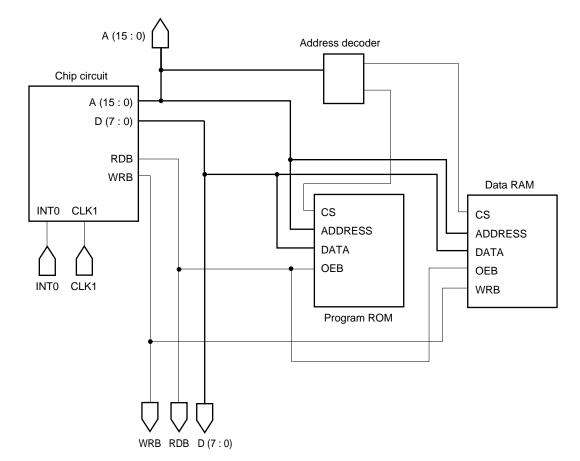

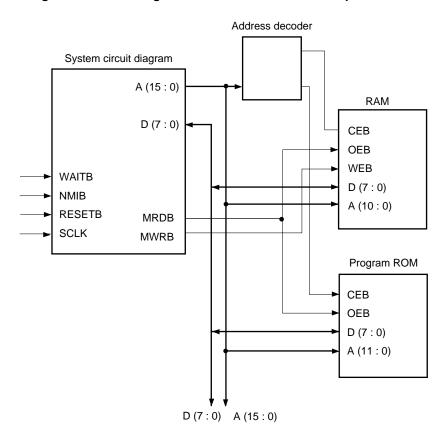

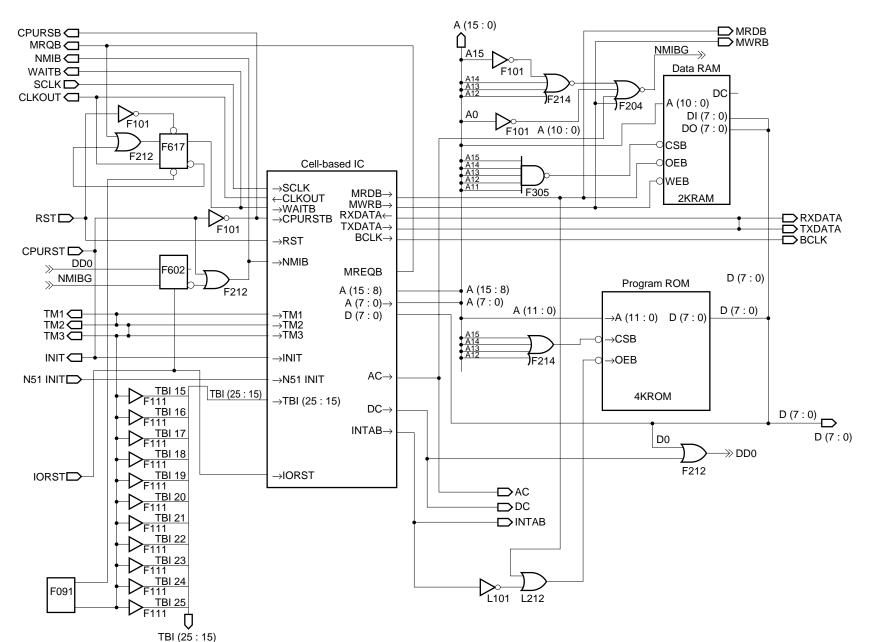

| 7-3    | Block Diagram of Circuit Used for Total Chip Simulation                                          | 180  |

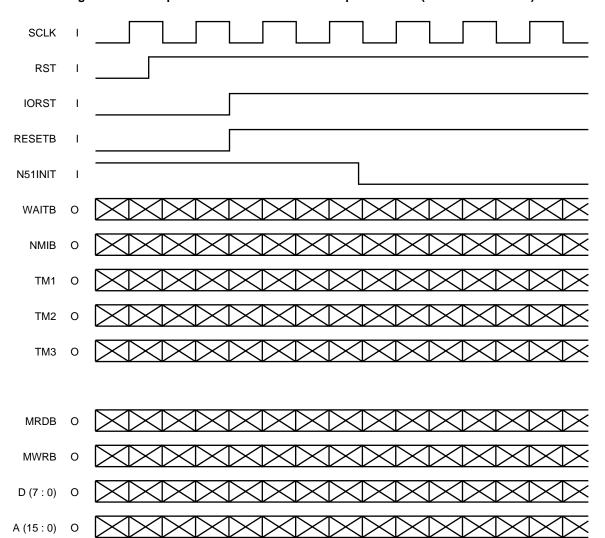

| 7-4    | Block Diagram of System Circuit                                                                  | 181  |

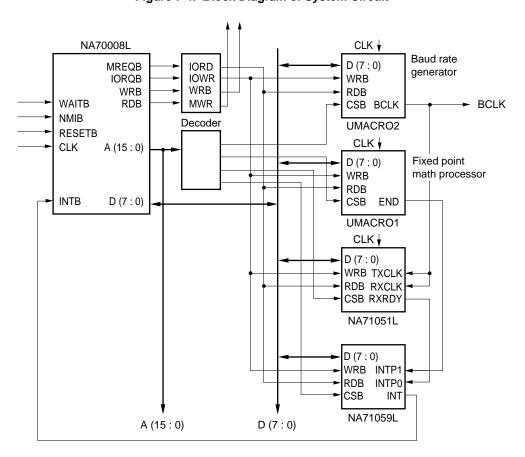

| 7-5    | Example of Test Pattern for Total Chip Simulation (with External ROM)                            | 182  |

| 7-6    | Circuit for Total Chip Simulation (with Added ROM and RAM for Simulation)                        | 183  |

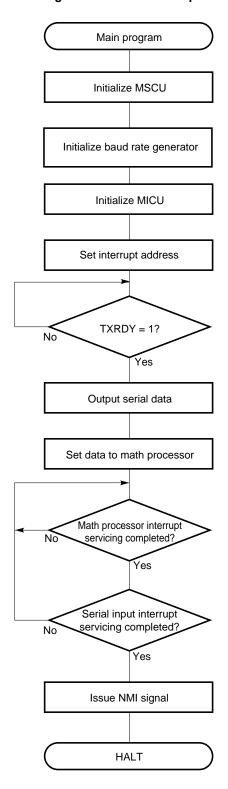

| 7-7    | Program Flow for Total Chip Simulation                                                           | 184  |

| 7-8    | Example of Execution Steps When Using OPENCAD (Using V.sim <sup>™</sup> )                        | 192  |

|        |                                                                                                  |      |

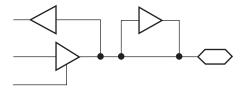

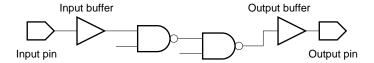

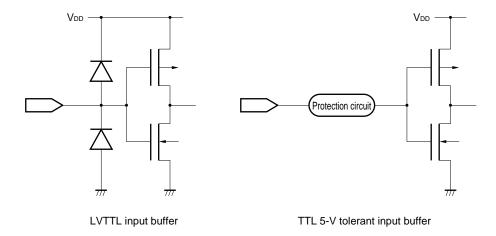

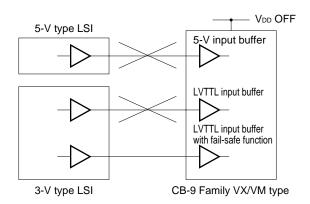

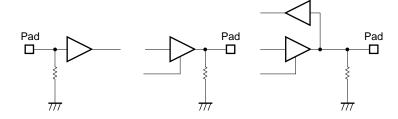

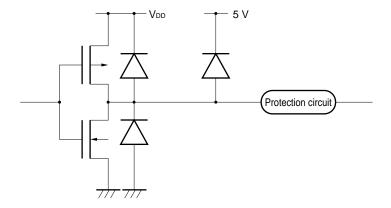

| 9-1    | Equivalent Circuit Diagrams of 3.3-V and 5-V Input Buffers                                       | 198  |

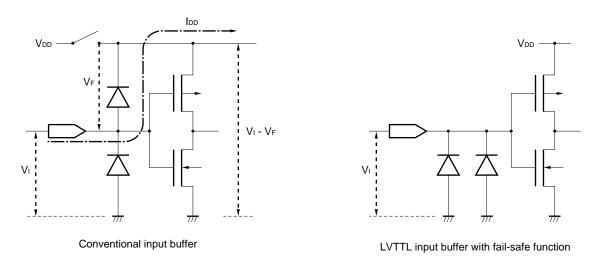

| 9-2    | Equivalent Circuit Diagrams and Connection Example of 3.3-V Input Buffer with Fail-safe Function | 198  |

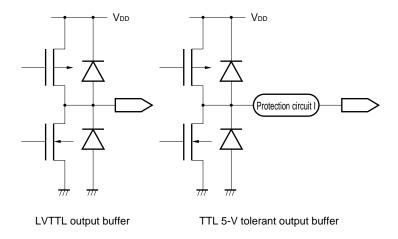

| 9-3    | Equivalent Circuit Diagrams of Output Buffers                                                    | 200  |

| 9-4    | Connection Examples of TTL 5-V Tolerant Output Buffer and 5-V Output Buffer                      | 200  |

| 9-5    | Oscillator Block Configuration Examples                                                          | 205  |

| 9-6    | Oscillator Configuration Diagrams                                                                | 207  |

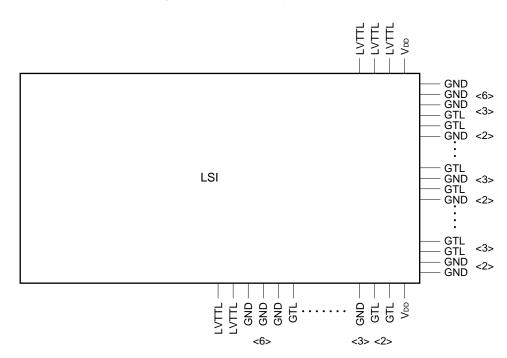

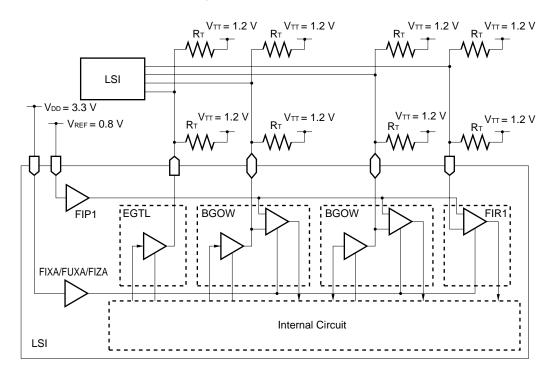

| 9-7    | GTL Pin Layout Example                                                                           | 209  |

| 9-8    | GTL Use Example                                                                                  | 210  |

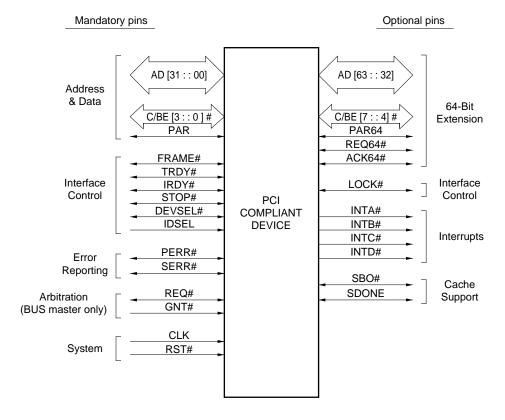

| 9-9    | PCI Pin List                                                                                     | 211  |

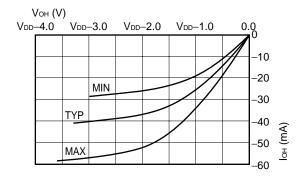

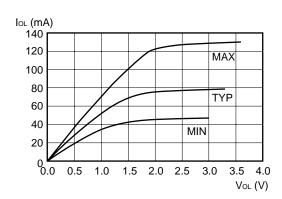

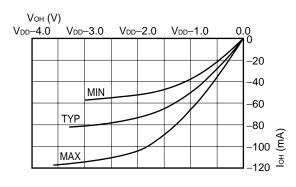

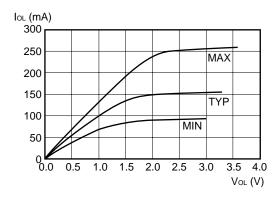

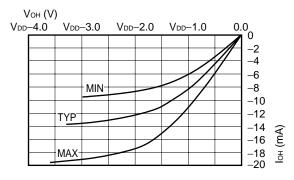

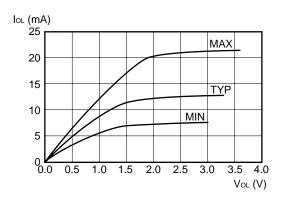

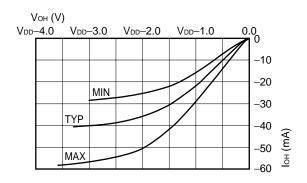

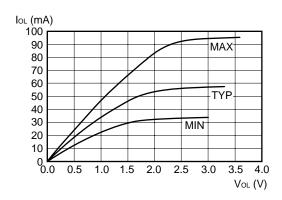

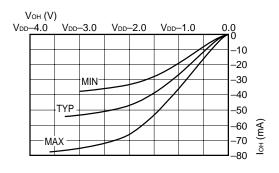

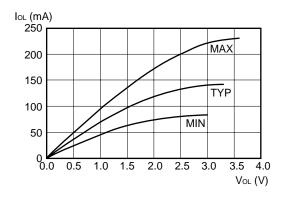

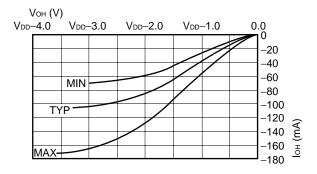

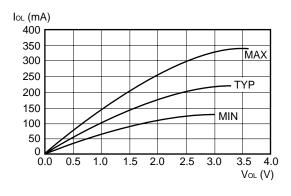

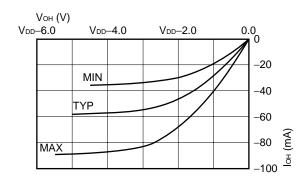

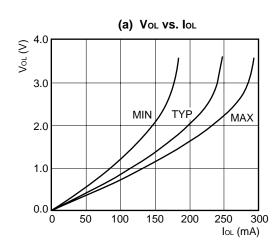

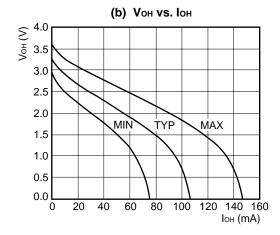

| 9-10   | Vo vs. lo                                                                                        | 213  |

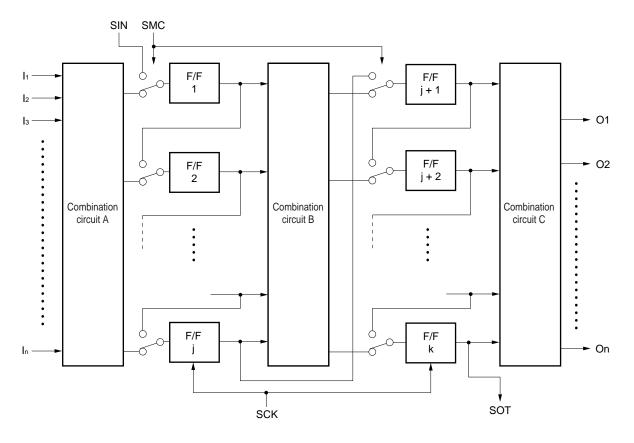

| 9-11   | Principles of Scan Path Test Method                                                              |      |

# LIST OF TABLES (1/2)

| Table | No. Title                                                                            | Page |

|-------|--------------------------------------------------------------------------------------|------|

| 1-1   | Abbreviated List of Specifications: CB-9 Family's VX/VM Types                        | 19   |

| 2-1   | Total Grid Counts and Grid Utilization Rates for Each Step Size                      | 34   |

| 2-2   | Package List                                                                         |      |

| 3-1   | Terms Used in Absolute Maximum Ratings                                               | 45   |

| 3-2   | Terms Used in Recommended Operating Range                                            | 46   |

| 3-3   | Terms Used in DC Characteristics                                                     | 46   |

| 3-4   | Absolute Maximum Ratings                                                             | 47   |

| 3-5   | Recommended Operating Conditions                                                     | 48   |

| 3-6   | DC Characteristics (V <sub>DD</sub> = 3.3±0.3 V, T <sub>A</sub> = -40 to +85°C)      | 49   |

| 3-7   | Pull-up/Pull-down Resistance Values (VDD = 3.3±0.3 V, TA = -40 to +85°C)             | 52   |

| 3-8   | Pull-up/Pull-down Resistance Values (VDD = 5.0±0.5 V, TA = -40 to +85°C)             | 52   |

| 3-9   | AC Characteristics (T <sub>A</sub> = -40 to +85°C)                                   | 53   |

| 3-10  | Package Capacitance (C <sub>P</sub> ) (V <sub>DD</sub> = 0 V, T <sub>A</sub> = 25°C) | 54   |

| 3-11  | Interface Block Capacitance (C <sub>B</sub> )                                        | 56   |

| 4-1   | Power Consumption by Each Input Buffer                                               | 65   |

| 4-2   | Power Consumption by Output Buffers                                                  | 66   |

| 4-3   | Power Consumption by GTL Input Section                                               | 67   |

| 4-4   | Maximum Allowable Power Consumption                                                  | 74   |

| 4-5   | List of Thermal Resistance Values                                                    | 77   |

| 4-6   | Propagation Delay Time Characteristics                                               | 85   |

| 4-7   | List of Coefficients for LVTTL Output Buffer tr and tr Calculations                  | 89   |

| 4-8   | List of Coefficients for TTL 5-V Tolerant Output Buffer tr and tr Calculations       | 90   |

| 4-9   | List of Coefficients for 5-V Output Buffer tr and tr Calculations                    | 91   |

| 4-10  | List of Coefficients for 3.3 V-to-2.0 V Output Buffer tr and tr Calculations         | 92   |

| 4-11  | Recommended Load Capacitance Ranges (pF) for Output Buffers                          | 93   |

| 4-12  | SSO Limitation Time Range (TYP.)                                                     | 112  |

| 4-13  | Limited Number of SSO Pins between 3 GND Pins (3.3-V Output Buffer, IoL = 12 mA)     | 112  |

| 4-14  | SSO Pin Conversion Coefficients                                                      | 113  |

| 5-1   | Circuit Design Characteristics                                                       | 128  |

| 5-2   | FCTS Clock Skew (VDD = 3.3 V, TA = -40 to +85°C)                                     | 142  |

| 5-3   | FCTS Clock Skew (VDD = 2.0 V, TA = -40 to +85°C)                                     | 142  |

| 5-4   | FCTS Clock Tree Block Predicted Delay Time Reference Values (VDD = 3.3 V: TYP.)      | 143  |

| 5-5   | FCTS Clock Tree Block Predicted Delay Time Reference Values (VDD = 2.0 V: TYP.)      | 143  |

| 5-6   | FCTS Specifications (VDD = 3.3 V)                                                    | 143  |

| 5-7   | FCTS Specifications (VDD = 2.0 V)                                                    | 143  |

| 5-8   | Example of Standard Bus Interfaces for Single-Chip Design                            | 148  |

### LIST OF TABLES (2/2)

| Table | No. Title                                                                                   | Page |

|-------|---------------------------------------------------------------------------------------------|------|

| 9-1   | Recommended Oscillation Frequency Ranges for Oscillator Blocks                              | 202  |

| 9-2   | Ceramic Resonator Evaluation List                                                           | 206  |

| 9-3   | Crystal Resonator Evaluation List                                                           | 207  |

| 9-4   | Electrical Characteristics of GTL                                                           | 208  |

| A-1   | List of Power Supply Pins in Packages (VX Type, 3.3-V Single Power Supply)                  | 215  |

| A-2   | List of Power Supply Pins in Packages (VX Type, When Using Internal 2.0-V Power Supply Pin) | 221  |

| A-3   | List of Power Supply Pins in Packages (VM Type)                                             | 226  |

# [MEMO]

### **CHAPTER 1 GENERAL**

### 1.1 Features

The CB-9 Family's VX/VM Types ( $\mu$ PD82 $\times\times\times$ ) use a 0.35- $\mu$ m process for high-precision fabrication of cell-based ICs that include a two-layer or three-layer wiring layout for low power consumption, high speed, and high integration.

Users may choose between two types based on power supply voltage: the VX Type (2.0-V or 3.3-V internal power supply, 3.3-V I/O power supply), which is the low-power version, or the VM Type (3.3-V internal power supply, 5-V or 3.3-V I/O power supply), which is the ordinary version.

Table 1-1. Abbreviated List of Specifications: CB-9 Family's VX/VM Types

| Туре          |                    | e                   | VX Type                                                                                                                                                         | VM Type              |  |

|---------------|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Power         |                    | Internal            | 2.0 V, 3.3 V                                                                                                                                                    | 3.3 V                |  |

| supply voltag | je <sup>Note</sup> | I/O                 | 3.3 V                                                                                                                                                           | 3.3 V, 5.0 V         |  |

| I/O interface |                    |                     | LVTTL, TTL 5-V tolerant maximum voltage                                                                                                                         | LVTTL, TTL, CMOS 5 V |  |

| Operating ter | mperature          | e <sup>Note</sup>   | -40 to +85°C                                                                                                                                                    |                      |  |

| Delay time    |                    | Internal gate       | 114 ps (VDD = 3.3 V, fan-outs = 2, $\ell$ = standard wiring length, power gate) 207 ps (VDD = 2.0 V, fan-outs = 2, $\ell$ = standard wiring length, power gate) |                      |  |

|               |                    | Input buffer        | 169 ps (VDD = 3.3 V, fan-outs = 2, $\ell$ = standard wirin 690 ps (VDD = 5.0 V, fan-outs = 2, $\ell$ = standard wirin                                           | 0 0 ,                |  |

|               |                    | Output buffer       | 864 ps (V <sub>DD</sub> = 3.3 V, load = 15 pF, lo <sub>L</sub> = 18 mA)<br>2045 ps (V <sub>DD</sub> = 5.0 V, load = 15 pF, lo <sub>L</sub> = 18 mA)             |                      |  |

| Power consu   | Power consumption  |                     | 0.3 $\mu$ W/MHz/gate (V <sub>DD</sub> = 3.3 V)<br>0.12 $\mu$ W/MHz/gate (V <sub>DD</sub> = 2.0 V)                                                               |                      |  |

| Technology (  | design ru          | ıle)                | 0.35-μm silicon gate CMOS                                                                                                                                       |                      |  |

| Packages      | QFP (f             | ine pitch)          | 100, 120, 144, 160, 176, 208, 240, 304                                                                                                                          |                      |  |

|               | QFP (v             | vith heat spreader) | 160, 176, 208, 240, 304                                                                                                                                         |                      |  |

|               | TQFP               |                     | 100, 120                                                                                                                                                        |                      |  |

|               | LQFP<br>PGA        |                     | 144, 160, 176, 208                                                                                                                                              |                      |  |

|               |                    |                     | 364, 528                                                                                                                                                        |                      |  |

| BGA           |                    |                     | 256, 352, 420, 500, 576, 696                                                                                                                                    |                      |  |

Note If the device includes cores, the guaranteed ranges may differ according to the cores that are included.

**Remark** Before starting design work, contact NEC for the latest information on available packages, which are continually being updated.

### 1.1.1 Features of VX/VM types

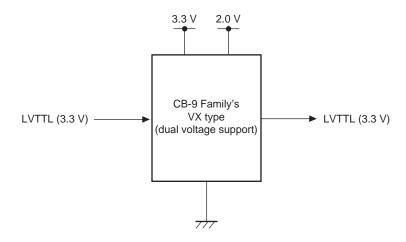

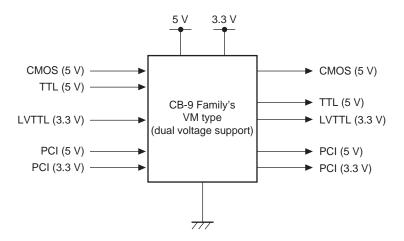

Unlike previous products, the CB-9 Family's VX/VM types enable the voltage of the I/O power supply and internal power supply to be set separately. The VX type can be operated using 2.0-V power internally while also using a 3.3-V I/O power supply, and the VM type can be operated using 3.3-V power internally while also using a 5-V I/O power supply. Both are suited for systems featuring low power consumption.

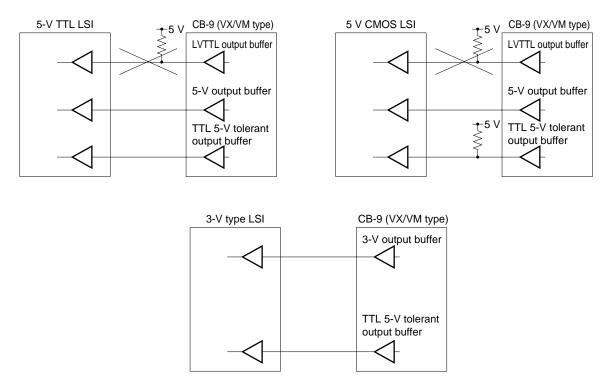

### (1) Interface levels and power supply voltages

The CB-9 Family's VX/VM types are available with a 3.3-V or 5-V I/O power supply. Select the type best suited to the target system. CMOS 5-V, TTL, PCI (5 V) can be used when using the 5-V power supply type, and TTL, LVTTL, PCI (3 V) can be used when using the 3.3-V power supply type.

Use a TTL 5-V tolerant buffer when using a TTL interface with the 3.3-V power supply type.

Figure 1-1. Interface and Supply Voltages (1/2)

# CMOS (5 V) TTL (5 V) LVTTL (3.3 V) PCI (5 V)Note PCI (5 V)Note PCI (3.3 V) PCI (3.3 V)

(a) 3.3-V single power supply

**Remark** Voltage values in parentheses indicate the interface standard.

Note When using a VX-type 5-V PCI, a separate 5-V power supply is required (see 9.5.1 Signal standard for PCI local bus).

Figure 1-1. Interface and Supply Voltages (2/2)

### (b) I/O: 3.3 V, internal: 2.0 V

### (c) I/O: 3.3 V or 5 V, internal: 3.3 V

**Remark** Voltage values in parentheses indicate the interface standard.

### (2) I/O buffer layout

The VM type uses the power supply lines shown in Figure 1-2, which means that the 5-V buffer and 3.3-V buffer can be laid out independently. However, latch-up may occur when 5-V buffer is placed next to TTL 5-V-tolerant buffer (refer to **2.4 (5) 5-V buffer**).

3.3-V buffer 3.3-V PCI

5-V buffer 5-V PCI

5-V power supply line

3.3-V power supply line

GND line

Figure 1-2. Buffer Layout Example

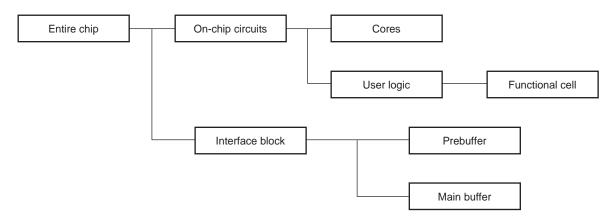

### 1.2 Internal Configuration of Cell-Based ICs

### 1.2.1 Chip configuration

Cell-based ICs generally include the following elements.

The meanings of these elements are described below.

| Elements         | Description                                                                                                     |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Core             | A function block and memory macro that includes a large number of gates, such as a CPU core or peripheral macro |  |  |  |  |  |  |

| User logic       | Circuits created by the user using functional cells                                                             |  |  |  |  |  |  |

| Functional cell  | A cell that contains basic functions such as OR, AND, and flip-flop                                             |  |  |  |  |  |  |

| Interface block  | A block used as an interface for external pins                                                                  |  |  |  |  |  |  |

| Prebuffer        | A buffer that is used to control the main buffer and that includes an interface block                           |  |  |  |  |  |  |

| Main buffer      | A buffer that is used as an interface for external devices and that includes an interface block                 |  |  |  |  |  |  |

| On-chip circuits | All circuits other than the interface block                                                                     |  |  |  |  |  |  |

**Remark** The interface block is a general term that refers to the input buffer, output buffer, and bidirectional buffer.

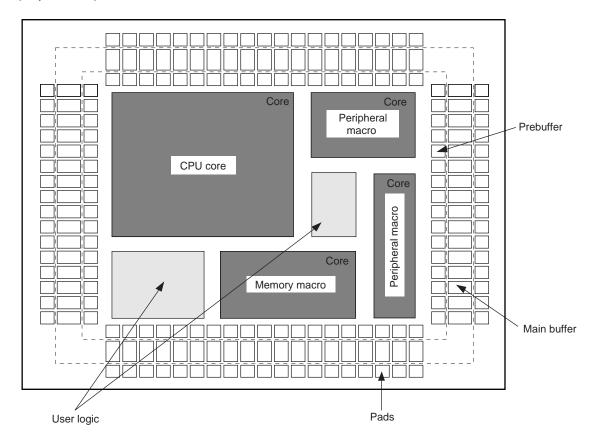

### 1.2.2 Chip layout

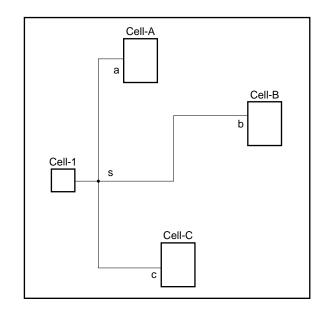

NEC's cell-based ICs use the building block method.

In the NA7105x and other products, the cores found in NEC's standard ICs can be combined with user logic on the same chip.

A chip layout example is shown below.

### 1.3 On-chip Transistor Configuration

CMOS circuits include a P-channel MOS transistor (P-ch.Tr) and an N-channel MOS transistor (N-ch.Tr). Ordinarily, either the P-ch.Tr or the N-ch.Tr remains off.

Consequently, almost no power supply current flows through the circuits when the device is in a steady (stationary) state, which keeps power consumption extremely low.

Almost all of the current consumption in CMOS devices occurs when switching circuits. Because an excessively large current flows during these switching operations, a high-speed high-capacity capacitor must be inserted between the power supply and the ground (GND) to sufficiently reduce the power supply's impedance.

When a large waveform is inserted to the CMOS circuits during the rising edge or falling edge period, a through current is fed between the P-ch.Tr and N-ch.Tr to enable both the P-ch.Tr and N-ch.Tr to remain on for a long period. Not only does this increase the current consumption, it can also cause operation faults.

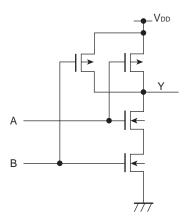

A dual-input NOR gate equivalent circuit diagram and a dual-input NAND gate equivalent circuit diagram are shown respectively in parts (a) and (b) of Figure 1-3. The N-ch.Tr has a generally lower ON-state resistance (about half that of P-ch.Tr), which means that a larger current can be conducted through N-ch.Tr.

Therefore, as shown in part (a) of Figure 1-3, the ON-state resistance is very large on the output's rising edge in NOR gates connected in series to P-ch.Tr, which reduces the load drive capacity.

In CMOS cell-based ICs, the NOR blocks are slower than NAND blocks and have poor fan-out characteristics. Consequently, NAND blocks should be used whenever possible to increase circuit speed and provide greater circuit stability.

For much the same reasons, a complex gate that includes many transistors connected in series tends to be slow and are thus ill-suited for high-speed circuits, but when used in parts of the chip where high speed is not required, they provide a good method for improving circuit stability and making effective use of cells.

Figure 1-3. Equivalent Circuits

### (a) Dual-input NOR equivalent circuit

# A P Y

### (b) Dual-input NAND equivalent circuit

### 1.4 Connection between 3.3-V Line and 5-V Line

Ultra-precise processing of transistors and reduction of power supply voltage are both essential factors in developing faster LSIs that consume less power. This is why lower power consumption has been sought in recent years in microcontrollers, memory devices, etc. Even among cell-based ICs, in the CB-9 Family, which are fabricated using cutting-edge transistor processing technologies, 3.3 V is the standard power supply voltage. However, 3.3 V is not yet the standard in all LSIs. Therefore, CB-9 Family products include an interface block to support connection of conventional LSIs with 5-V power supply voltage.

3.3-V input blocks are used to receive 3.3-V signals and therefore cannot be used to receive 5-V signals, which must be received by 5-V input blocks. The 5-V input blocks are designed to support the trend toward 3.3-V power supply voltage in peripheral circuits of conventional cell-based ICs by being able to receive 3.3-V signals. They also include 3.3-V input blocks with fail-safe functions that can be used for hot-line work.

In the output buffer, the output high level continues to be the same level as the V<sub>DD</sub> level in cell-based ICs, and both an LVTTL output buffer and a 5-V output buffer are provided. Unlike in previous products, the 5-V output buffer can pull up pins using 5-V voltage which is greater than the LSI's power supply voltage. This means that it can be connected to a 5-V bus line. For details of these blocks, see **9.1 3.3-V, 5-V Interface Blocks**.

### 1.5 QFP Package

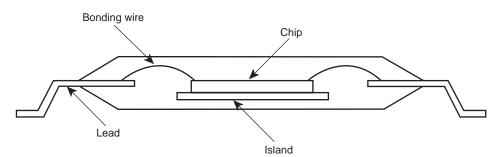

Figure 1-4 shows a section view of an ordinary QFP package. In such QFP packages, the chip is inserted on a metal plate called an "island". This structure includes very thin bonding wires (a few dozen  $\mu$ m thick) that connect the component leads to the chip.

QFP packages that have low thermal resistance use heat-discharging materials in their component leads and islands, however, their structure is same as ordinary QFP packages.

Figure 1-4. Section View of QFP Package

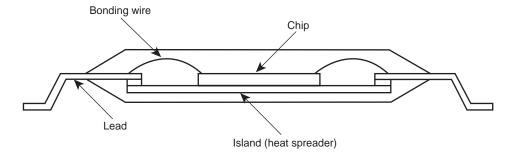

QFPs that include a heat spreader are made of the same materials as low thermal resistance type QFPs. The heat spreader-equipped QFP is characterized by its large island (the heat spreader) that provides greater heat dissipation (see Figure 1-5).

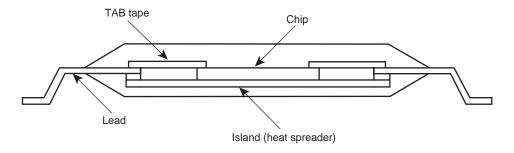

The "TAB in QFP" is a new type of QFP that has been introduced via the CB-9 Family. To enable many pins to be attached to a small chip, the gaps between the bonding pads on the chip had to be narrowed. However, narrowing these gaps makes it very difficult to connect bonding wire between the component leads and the pads. Therefore, TAB (Tape Automated Bonding) tape is used instead of bonding wire to connect the leads and pads, and hence the name "TAB in QFP" (see Figure 1-6). This type of package also features a large island that has heat dissipation effects similar to those of heat spreader packages.

Figure 1-5. Section View of QFP with Heat Spreader

Figure 1-6. Section View of TAB in QFP

### 1.6 Development Flow

### 1.6.1 Development flow (for chips with user logic + ROM/RAM)

Notes 1. This is an optional function that may not be usable depending on the tool used.

- 2. Necessary only when memory macros are mounted.

- 3. Necessary only when ROM macros are mounted.

### 1.6.2 Development flow (for chips with CPU and CPU peripherals)

Notes 1. This is an optional function that may not be usable depending on the tool used.

- 2. Necessary only when cores are mounted.

- 3. Necessary only when CPU cores are mounted.

- 4. Necessary only when ROM macros are mounted.

### 1.6.3 Description of development flow

| Item          |                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| System design |                                         | This includes the setting of system specifications before starting the detailed design in order to implement required functions more economically and efficiently.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Me            | mory compiler                           | This step is required only when the chip contains RAM or ROM. Specifying the bit width and the number of words enables the required RAM and/or ROM to be implemented more easily.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Log           | gic synthesis                           | Verilog HDL (Hardware Description Language) can be used to automatically generate gate-level circuits. Also, a netlist can be used to optimize logic circuit areas and delay times.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| DR            | C (Design Rule Check)                   | A check is performed to ensure compliance with all design rules.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Ass           | sumed wiring length simula              | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|               | User logic separation simulation Note 1 | If cores such as a CPU core or CPU peripheral macro are on chip, the gate conversion of the CPU core alone may result in a circuit having tens of thousands of gates. Accordingly, as a way of making the development process more effective, we recommend that the user logic block be implemented separately on a test circuit, which enables a separate simulation to be executed so as to identify and eliminate circuit errors before proceeding to the total chip simulation. |  |  |  |  |  |

|               | Test circuit check Note 2               | This check is performed to verify that the core's separate test circuits are correctly connected.  We recommend checking to confirm the core block's test can be used as a test circuit for a standard test pattern in the process of shipment inspection.                                                                                                                                                                                                                          |  |  |  |  |  |

|               | Floor planning                          | Floor planning determines how core and user logic blocks will be laid out on the chip. The optimum layout is one that minimizes the total wiring length while also minimizing dead space on the chip.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|               | Assumed wiring length calculation       | This calculates an estimated wiring length which is needed to perform simulations before deciding the final layout. The division of the circuit's second layer into blocks is taken into account while estimating the wiring length between blocks based on each block is assumed wiring length and the step size being used. If the user is performing the floor planning, the wire length can be calculated with the floor plan taken into account.                               |  |  |  |  |  |

|               | Total chip simulation                   | This simulates the actual operation mode of the entire chip. Consists mainly in checking the wire connections between macros.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Fau           | ult simulation                          | This simulation determines how many faults can be detected (i.e., the fault coverage) in all circuits using the user-generated test pattern and which part of the faults can not be detected.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|               | ual wiring length<br>nulation           | Using the wiring length of an actual layout (i.e., the actual wiring length), a separate simulation is performed on user logic and a total chip simulation is also performed. The simulation conditions are intended to reflect the actual operating conditions and the tester conditions.                                                                                                                                                                                          |  |  |  |  |  |

| IE :          | setup                                   | If the chip contains a CPU core, an in-circuit emulator is set up to aid the development of application software.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

- **Notes 1.** This is not required for a user logic + RAM/ROM chip.

- 2. If the chip includes a RAM macro, be sure to access RAM during test mode to check the test circuit. If the chip includes a ROM macro, be sure to set up a test pattern that will output all of the bits in the ROM code during test mode.

### CHAPTER 2 INTRODUCTION TO CELL-BASED ICs

When designing LSIs using cell-based ICs for all or part of a user-designed system, determine the specifications as follows to ensure appropriate cell-based IC circuit size and an optimum number of I/O pins.