# Dual PWM Fan Controller and Temperature Monitor for Servers

# Preliminary Technical Data

# ADM1029

#### FEATURES

Programmable and Automatic Fan Speed Control

- Fan Speed Measurement

- Supports Backup and Redundant Fans

- **Supports Hot Swapping of Fans**

Cascadable Fault Output Allows Linking of Multiple ADM1029s

**Remote and Local Temperature Monitoring**

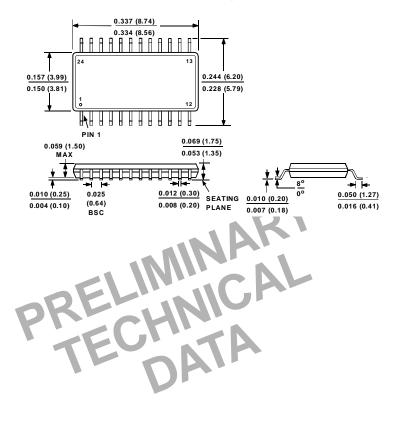

Small 24 pin QSOP Package

APPLICATIONS

Network Servers and Personal Computers Microprocessor-Based Office Equipment Test Equipment and Measuring Instruments

#### REV. Pr.F 4/2000

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### I<sup>2</sup>C is a registered trademark of Philips Corporation

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2000

# **Preliminary Technical Data**

#### **PRODUCT DESCRIPTION**

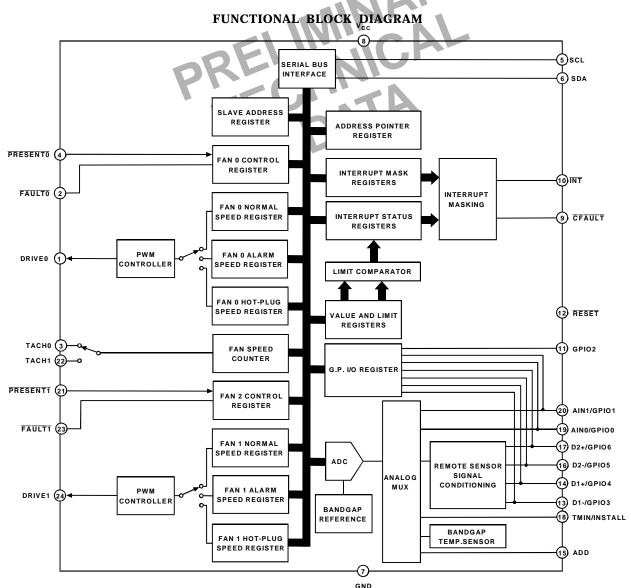

The ADM1029 is a versatile fan controller and monitor for use in personal computers, servers, network hubs, or any system where reliable control and monitoring of multiple cooling fans is required. Each ADM1029 can control the speed of one or two fans and can measure the speed of fans that have a tachometer output. The ADM1029 can also measure the temperature of one or two external sensing diodes or an internal temperature sensor, allowing fan speed to be adjusted to keep system temperature within acceptable limits. The ADM1029 has FAULT inputs for use with fans that can signal failure conditions, and inputs to detect if fans are connected or not.

The ADM1029 communicates with the host processor over an SMBus/I<sup>2</sup>C-compatible serial bus. It supports 8 different serial bus addresses, so that up to 8 devices can be connected to a single serial bus segment, controlling up to 16 fans.

The ADM1029 has an interrupt output  $(\overline{INT})$  that allows it to signal fault conditions to the host processor. It also has a separate, cascadable fault output  $(\overline{CFAULT})$  that allows the ADM1029 to signal a fault condition to other ADM1029s.

The ADM1029 has a number of useful features including automatic temperature control option implemented in hardware with no software requirement, automatic use of backup fans in the event of fan failure, and supports hot-swapping of failed fans.

| Parameter                                  | Min  | Тур       | Max        | Units | <b>Test Conditions/Comments</b>                                                           |

|--------------------------------------------|------|-----------|------------|-------|-------------------------------------------------------------------------------------------|

| POWER SUPPLY                               |      |           |            |       |                                                                                           |

| Supply Voltage, V <sub>CC</sub>            | 2.8  | 3.30      | 6          | V     |                                                                                           |

| Supply Current, I <sub>CC</sub>            |      | 1.4       | 2.0        | mA    | Interface Inactive, ADC Active                                                            |

| OKK                                        |      | 1.0       |            | mA    | ADC Inactive, DAC Active                                                                  |

|                                            |      | 32        | 100        | μA    | Shutdown Mode                                                                             |

| TEMPTO-DIGITAL CONVERTER                   |      |           | <b>T</b> P |       |                                                                                           |

| Internal Sensor Accuracy                   |      | $\pm 1$   | ±3         | °C    |                                                                                           |

| Resolution                                 |      | 1         |            | °C    |                                                                                           |

| External Diode Sensor Accuracy             |      | ±3        | $\pm 5$    | °C    | $0 \ ^{\mathrm{o}}\mathrm{C} \le \mathrm{T}_{\mathrm{A}} \le +100^{\mathrm{o}}\mathrm{C}$ |

| Resolution                                 |      | 1         |            | °C    |                                                                                           |

| Remote Sensor Source Current               | 60   | 90        | 130        | μA    | High Level                                                                                |

|                                            | 3.5  | 5.5       | 7.5        | μA    | Low Level                                                                                 |

| ANALOG-TO-DIGITAL CONVERTER                |      |           |            |       |                                                                                           |

| Total Unadjusted Error, TUE                |      |           | $\pm 2$    | %     | Note 3                                                                                    |

| Differential Non-Linearity, DNL            |      |           | ±1         | LSB   |                                                                                           |

| Power Supply Sensitivity                   |      | ±1        |            | %/V   |                                                                                           |

| Conversion Time (Analog Input or Int.Temp) |      | 11.6      |            | ms    |                                                                                           |

| Conversion Time (External Temperature)     |      | 185.6     |            | ms    |                                                                                           |

| Input Resistance (AIN0/1)                  | Hig  | n Resista | ance       |       |                                                                                           |

| FAN RPM-TO-DIGITAL CONVERTER               |      |           |            |       |                                                                                           |

| Accuracy                                   |      |           | $\pm 6$    | %     |                                                                                           |

| Full-Scale Count                           |      |           | 255        |       |                                                                                           |

| FAN0 and FAN1 Nominal Input RPM            |      | 8800      |            | RPM   | Divisor = 1, Fan Count = 153                                                              |

| (Note 4)                                   |      | 4400      |            | RPM   | Divisor = 2, Fan Count = 153                                                              |

|                                            |      | 2200      |            | RPM   | Divisor = 4, Fan Count = $153$                                                            |

|                                            |      | 1100      |            | RPM   | Divisor = 8, Fan Count = $153$                                                            |

| Internal Clock Frequency                   | 56.4 | 60.0      | 63.6       | kHz   |                                                                                           |

# **ADM1029—SPECIFICATIONS** ( $T_A = T_{MIN}$ to $T_{MAX}$ , $V_{CC} = V_{MIN}$ to $V_{MAX}$ , unless otherwise noted)

# ADM1029

# Specifications (Continued)

| Parameter                                                                               | Min       | Тур | Max | Units    | Test Conditions/Comments                           |

|-----------------------------------------------------------------------------------------|-----------|-----|-----|----------|----------------------------------------------------|

| DIGITAL OUTPUTS                                                                         |           |     |     |          |                                                    |

| Output High Voltage, V <sub>OH</sub>                                                    | 2.4       |     |     | V        | $I_{OUT} = 3.0 m A,$                               |

|                                                                                         |           |     |     |          | $V_{CC} = 2.85V - 3.60V$                           |

| Output Low Voltage, V <sub>OL</sub>                                                     |           |     | 0.4 | V        | $I_{OUT} = -3.0 m A,$                              |

|                                                                                         |           |     |     |          | $V_{CC} = 2.85V - 3.60V$                           |

| OPEN-DRAIN DIGITAL OUTPUTS                                                              |           |     |     |          |                                                    |

| (INT, CFAULT)                                                                           |           |     |     |          |                                                    |

| Output Low Voltage, V <sub>OL</sub>                                                     |           |     | 0.4 | V        | $I_{OUT} = -3.0 \text{mA}, V_{CC} = 3.60 \text{V}$ |

| High Level Output Current, I <sub>OH</sub>                                              |           | 0.1 | 100 | μA       | $V_{OUT} = V_{CC}$                                 |

| RESET And CI Pulse Width                                                                | 20        | 45  |     | ms       |                                                    |

| OPEN-DRAIN SERIAL DATA<br>BUS OUTPUT (SDA)                                              |           |     |     |          |                                                    |

| Output Low Voltage, V <sub>OL</sub>                                                     |           |     | 0.4 | V        | $I_{OUT} = -3.0 m A,$                              |

|                                                                                         |           |     |     | N        | $V_{CC} = 2.85V - 3.60V$                           |

| High Level Output Current, I <sub>OH</sub>                                              |           | 0.1 | 100 | μA       | $V_{OUT} = V_{CC}$                                 |

| SERIAL BUS DIGITAL INPUTS                                                               |           |     |     |          |                                                    |

| (SCL, SDA)                                                                              |           |     |     |          |                                                    |

| Input High Voltage, V <sub>IH</sub>                                                     | 2.2       |     |     | V        |                                                    |

| Input Low Voltage, VIL                                                                  |           |     | 0.8 | V        |                                                    |

| Hysteresis                                                                              |           | 500 |     | mV       |                                                    |

| DIGITAL INPUT LOGIC LEVELS                                                              | <b>PH</b> |     |     |          |                                                    |

| RESET, GPIO1-6, FAULTO/1, TACH0/1                                                       |           |     |     |          |                                                    |

| SHDN, PRESENT0/1                                                                        |           | N   |     |          |                                                    |

| Input High Voltage, V <sub>IH</sub>                                                     | 2.2       |     |     | V        | $V_{CC} = 2.85V - 5.5V$                            |

| Input Low Voltage, V <sub>IL</sub>                                                      |           | -   | 0.8 | V        | $V_{\rm CC} = 2.85 V - 5.5 V$                      |

| DIGITAL INPUT CURRENT                                                                   |           |     |     |          |                                                    |

| Input High Current, I <sub>IH</sub>                                                     | - 1       |     |     | μA       | $V_{IN} = V_{CC}$                                  |

| Input Low Current, III                                                                  |           |     | 1   | μA       | $V_{IN} = 0$                                       |

| Input Capacitance, C <sub>IN</sub>                                                      |           | 20  |     | pF       |                                                    |

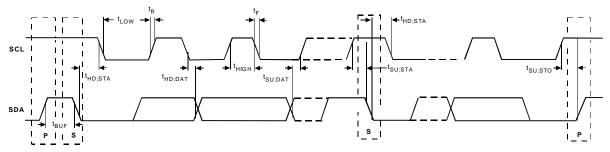

| SERIAL BUS TIMING                                                                       |           |     |     |          |                                                    |

| Clock Frequency, f <sub>SCLK</sub>                                                      |           |     | 400 | kHz      | See Figure 1                                       |

| Glitch Immunity, t <sub>SW</sub>                                                        |           |     | 50  | ns       | See Figure 1                                       |

| Bus Free Time, t <sub>BUF</sub>                                                         | 1.3       |     |     | μs       | See Figure 1                                       |

| Start Setup Time, t <sub>SU;STA</sub>                                                   | 600       |     |     | ns       | See Figure 1                                       |

| Start Hold Time, t <sub>HD,STA</sub>                                                    | 600       |     |     | ns       | See Figure 1                                       |

| SCL Low Time, t <sub>LOW</sub>                                                          | 1.3       |     |     | μs       | See Figure 1                                       |

| SCL High Time, t <sub>HIGH</sub>                                                        | 0.6       |     |     | μs       | See Figure 1                                       |

| SCL, SDA Rise Time, t <sub>r</sub>                                                      |           |     | 300 | ns       | See Figure 1                                       |

| $SCL, SDA Rise Time, t_r$                                                               |           |     |     | 1        |                                                    |

|                                                                                         |           |     | 300 | ns       | See Figure 1                                       |

| SCL, SDA Rise Time, $t_r$<br>SCL, SDA Fall Time, $t_f$<br>Data Setup Time, $t_{SU;DAT}$ | 100       |     | 300 | ns<br>ns | See Figure 1<br>See Figure 1                       |

#### NOTES

1 All voltages are measured with respect to GND, unless otherwise specified

<sup>2</sup> Typicals are at  $T_A=25^{\circ}C$  and represent most likely parametric norm. Shutdown current typ is measured with  $V_{CC}=3.3V$

3 TUE (Total Unadjusted Error) includes Offset, Gain and Linearity errors of the ADC and multiplexer.

<sup>4</sup> The total fan count is based on 2 pulses per revolution of the fan tachometer output. <sup>5</sup> Timing specifications are tested at logic levels of  $V_{IL} = 0.8V$  for a falling edge and  $V_{IH} = 2.2V$  for a rising edge.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Positive Supply Voltage (V <sub>CC</sub> )                           |

|----------------------------------------------------------------------|

| Voltage on Pin 13, 14, 15, 16, 17, 180.3V to (V <sub>CC</sub> +0.3V) |

| Voltage on Any Other Input or Output Pin0.3V to 6.5V                 |

| Input Current at any pin (Note 2) ±5mA                               |

| Package Input Current (Note 2) ±20mA                                 |

| Maximum Junction Temperature (T <sub>J</sub> max)150 °C              |

| Storage Temperature Range65°C to +150°C                              |

| Lead Temperature, Soldering                                          |

| Vapor Phase 60 sec+215°C                                             |

| Infra-Red 15 sec+200°C                                               |

| ESD Rating all pins 2000 V                                           |

|                                                                      |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Preliminary Technical Data**

### THERMAL CHARACTERISTICS

24-QSOP Package:

$\theta_{JA} = 105^{\circ}C/Watt, \ \theta_{JC} = 39^{\circ}C/Watt$

#### **ORDERING GUIDE**

| Model      | Temperature   | Package                | Package |  |

|------------|---------------|------------------------|---------|--|

|            | Range         | Description            | Option  |  |

| ADM1029ARQ | 0°C to +100°C | 24-Pin QSOP<br>Package | RQ-24   |  |

Figure 1. Diagram for Serial Bus Timing

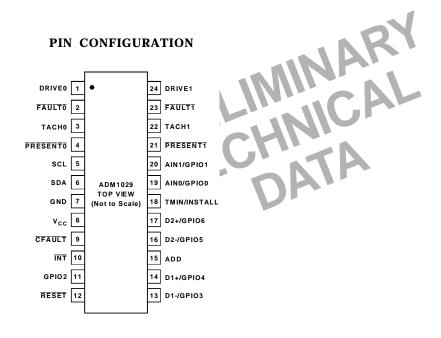

| PIN FUNCTION DESCRIPTION |                 |                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN NO.                  | MNEMONIC        | DESCRIPTION                                                                                                                                                                                                                                      |  |  |  |  |

| 1                        | DRIVE0          | Digital Output. Pulse-Width Modulated (PWM) output to control the speed of fan 0.                                                                                                                                                                |  |  |  |  |

| 2                        | FAULTO          | Digital I/O. When used with a fan having a fault output, a logic 0 input to this pin signals a fault on fan 0. Also used as a fault output.                                                                                                      |  |  |  |  |

| 3                        | TACH0           | Digital Input. Digital fan tachometer input for fan 0. Will accept logic signals up t $+5V$ even when $V_{CC}$ is lower than 5V.                                                                                                                 |  |  |  |  |

| 4                        | PRESENT0        | Digital Input. A shorting link in the fan connector holds this pin low when fan 0 is connected.                                                                                                                                                  |  |  |  |  |

| 5                        | SCL             | Digital Input. Serial Bus Clock.                                                                                                                                                                                                                 |  |  |  |  |

| 6                        | SDA             | Digital I/O. Serial Bus bidirectional data. Open-drain output.                                                                                                                                                                                   |  |  |  |  |

| 7                        | GND             | System Ground.                                                                                                                                                                                                                                   |  |  |  |  |

| 8                        | V <sub>CC</sub> | POWER (+2.8V to +5.5V). Typically powered from +3.3V power rail. Bypass with the parallel combination of 10 $\mu$ F (electrolytic or tantalum) and 0.1 $\mu$ F (ceramic) bypass capacitors.                                                      |  |  |  |  |

| 9                        | <u>CFAULT</u>   | Digital I/O. Cascade fault input/output used for fault signalling between ADM1029s.                                                                                                                                                              |  |  |  |  |

| 10                       | ĪNT             | Digital Output. Interrupt Request (open drain). The output is enabled when Bit 1 of the Configuration Register is set to 0. The default state is enabled.                                                                                        |  |  |  |  |

| 11                       | GPIO2           | Digital I/O. General-purpose logic I/O pin.                                                                                                                                                                                                      |  |  |  |  |

| 12                       | RESET           | Digital Input. Active low reset input.                                                                                                                                                                                                           |  |  |  |  |

| 13                       | D1-/GPIO3       | Analog Input/Digital I/O. Connected to cathode of external temperature sensing diode, or may be re-configured as a general-putpose logic input/output.                                                                                           |  |  |  |  |

| 14                       | D1+/GPIO4       | Analog Input/Digital I/O. Connected to anode of external temperature sensing diode, or may be re-configured as a general-putpose logic input/output.                                                                                             |  |  |  |  |

| 15                       | ADD             | 8-level Analog Input. Used to set the three LSBs of the serial bus address.                                                                                                                                                                      |  |  |  |  |

| 16                       | D2-/GPIO5       | Analog Input/Digital I/O. Connected to cathode of external temperature sensing diode, or may be re-configured as a general-putpose logic input/output.                                                                                           |  |  |  |  |

| 17                       | D2+/GPIO6       | Analog Input/Digital I/O. Connected to anode of external temperature sensing diode, or may be re-configured as a general-putpose logic input/output.                                                                                             |  |  |  |  |

| 18                       | TMIN/INSTALL    | 8-level Analog Input. The voltage on this pin defines if automatic fan speed control is enabled, the minimum temperature at which the fan(s) will turn on in automatic speed control mode, and also the number of fans that should be installed. |  |  |  |  |

| 19                       | AIN0/GPIO0      | Analog Input/Digital I/O. May be configured as a 0 to $+2.5V$ analog input or as a general-purpose digital I/O pin.                                                                                                                              |  |  |  |  |

| 20                       | AIN1/GPIO1      | Analog Input/Digital I/O. May be configured as a 0 to +2.5V analog input or as a general-purpose digital I/O pin.                                                                                                                                |  |  |  |  |

| 21                       | PRESENT1        | Digital Input. A shorting link in the fan connector holds this pin low when fan 1 is connected.                                                                                                                                                  |  |  |  |  |

| 22                       | TACH1           | Digital Input. Digital fan tachometer input for fan 1. Will accept logic signals up to $+5V$ even when $V_{\rm CC}$ is lower than 5V.                                                                                                            |  |  |  |  |

| 23                       | FAULTI          | Digital I/O. Dual Function pin. When used with a fan having a fault output, a logic 0 input to this pin signals a fault on fan 1. Also used as a fault output.                                                                                   |  |  |  |  |

| 24                       | DRIVE1          | Digital Output. Pulse-Width Modulated (PWM) output to control the speed of fan 1.                                                                                                                                                                |  |  |  |  |

#### FUNCTIONAL DESCRIPTION

#### SERIAL BUS INTERFACE

Control of the ADM1029 is carried out via the serial bus. The ADM1029 is connected to this bus as a slave device, under the control of a master device.

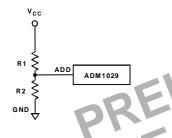

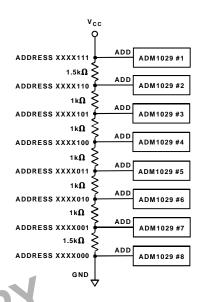

The ADM1029 has a 7-bit serial bus address. The four MSBs of the address are set to 0101. The three LSBs can be set by the user to give a total of 8 different addresses, allowing up to 8 ADM1029s to be connected to a single serial bus segment. To minimize device pin count and size, the three LSBs are set using a single pin (ADD, pin 13). This is an 8-level input whose input voltage is set by a potential divider. The voltage on ADD is sampled immediately after power up and digitized by the on-chip ADC to determine the value of the three LSBs. Since ADD is sampled only at power-up, any changes made while power is on will have no effect.

Figure 2. Setting The Serial Address

Table 1 shows resistor values for setting the 3 LSBs of the serial bus address. The same principle is used to set the voltage on pin 18 (TMIN/INSTALL), which controls the automatic fan speed control function, and also tells the ADM1029 how many fans should be installed, as described later.

If several ADM1029s are used in a system, their ADD inputs can tap off a single potential divider, as shown in Figure 3.

**Preliminary Technical Data**

### Figure 3. Setting Address Of Up To 8 ADM1029s

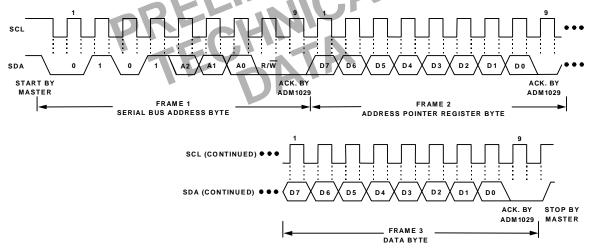

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a START condition, defined as a high to low transition on the serial data line SDA whilst the serial clock line SCL remains high. This indicates that an address/data stream will follow. All slave peripherals connected to the serial bus respond to the START condition, and shift in the next 8 bits, consisting of a 7-bit address (MSB first) plus a R/ $\overline{W}$  bit, which determines the direction of the data transfer, i.e. whether data will be written to or read from the slave device.

The peripheral whose address corresponds to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the Acknowledge Bit. All other devices on the bus now remain idle whilst the selected device waits for data to be read from or written to it. If the  $R/\overline{W}$  bit is a 0 then the master will write to the slave device. If the  $R/\overline{W}$  bit is a 1 the master will read from the slave device.

2. Data is sent over the serial bus in sequences of 9 clock

TABLE 1. Resistor Ratios for Setting Serial Bus Address, T<sub>MIN</sub> and Number of Fans Installed

|                  |                           | 0   |     |                      |        |          |                |         |

|------------------|---------------------------|-----|-----|----------------------|--------|----------|----------------|---------|

| 3 MSBs<br>of ADC | Ideal Ratio<br>R2/(R1+R2) | R1  | R2  | Actual<br>R2/(R1+R2) | Error  | TMIN     | Fans Installed | Address |

| 111              | n/a                       | 0   | 8   | 1                    | 0      | Disabled | 2              | 0101111 |

| 110              | 0.8125                    | 18k | 82k | 0.82                 | 0.75%  | 48°C     | 2              | 0101110 |

| 101              | 0.6875                    | 22k | 47k | 0.6812               | -0.63% | 40°C     | 2              | 0101101 |

| 100              | 0.5625                    | 12k | 15k | 0.5556               | -0.69% | 32°C     | 2              | 0101100 |

| 011              | 0.4375                    | 15k | 12k | 0.4444               | 0.69%  | 32°C     | 1              | 0101011 |

| 010              | 0.3125                    | 47k | 22k | 0.3188               | 0.63%  | 40°C     | 1              | 0101010 |

| 001              | 0.1875                    | 82k | 18k | 0.18                 | -0.75% | 48°C     | 1              | 0101001 |

| 000              | n/a                       | œ   | 0   | 0                    | 0      | Disabled | 1              | 0101000 |

# ADM1029

pulses, 8 bits of data followed by an Acknowledge Bit from the slave device. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, as a low to high transition when the clock is high may be interpreted as a STOP signal. The number of data bytes that can be transmitted over the serial bus in a single READ or WRITE operation is limited only by what the master and slave devices can handle.

3. When all data bytes have been read or written, stop conditions are established. In WRITE mode, the master will pull the data line high during the 10th clock pulse to assert a STOP condition. In READ mode, the master device will override the acknowldge bit by pulling the data line high during the low period before the 9th clock pulse. This is known as No Acknowledge. The master will then take the data line low during the low period before the 10th clock pulse, then high during the 10th clock pulse to assert a STOP condition.

Any number of bytes of data may be transferred over the serial bus in one operation, but it is not possible to mix read and write in one operation, because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation.

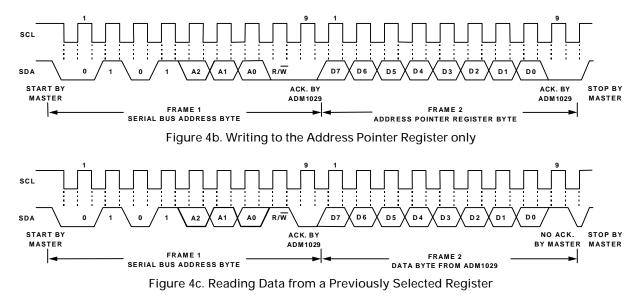

In the case of the ADM1029, write operations contain either one or two bytes, and read operations contain one byte, and perform the following functions:

To write data to one of the device data registers or read data from it, the Address Pointer Register must be set so that the correct data register is addressed, then data can be written into that register or read from it. The first byte of a write operation always contains an address that is stored in the Address Pointer Register. If data is to be written to the device, then the write operation contains a second data byte that is written to the register selected by the address pointer register.

This is illustrated in figure 4a. The device address is sent over the bus followed by  $R/\overline{W}$  set to 0. This is followed by two data bytes. The first data byte is the address of the internal data register to be written to, which is stored in the Address Pointer Register. The second data byte is the data to be written to the internal data register.

When reading data from a register there are two possibilities:

1. If the ADM1029's Address Pointer Register value is unknown or not the desired value, it is first necessary to set it to the correct value before data can be read from the desired data register. This is done by performing a write to the ADM1029 as before, but only the data byte containing the register address is sent, as data is not to be written to the register. This is shown in figure 4b.

A read operation is then performed consisting of the serial bus address,  $R/\overline{W}$  bit set to 1, followed by the data byte read from the data register. This is shown in figure 4c.

2. If the Address Pointer Register is known to be already at the desired address, data can be read from the corresponding data register without first writing to the Address Pointer Register, so figure 4b can be omitted.

Note:

Although it is possible to read a data byte from a data register without first writing to the Address Pointer Register, if the Address Pointer Register is already at the correct value, it is not possible to write data to a register without writing to the Address Pointer Register, because the first data byte of a write is always written to the Address Pointer Register.

#### ALERT RESPONSE ADDRESS

The ADM1029 has an interrupt (INT) output that is asserted low when a fault condition occurs. Several INT outputs can be wire OR'd to a common interrupt line. When the host processor receives an interrupt request, it would normally need to read the INT bit of each device status register to identify which device had made the interrupt request. However the ADM1029 supports the optional Alert Response Address function of the SMBus protocol. When the host processor receives an interrupt request it can send a general call address (0001100) over the bus. The device asserting INT will then send its own slave address back to the host processor, so the device asserting INT can be identified immediately.

If more than one device is asserting  $\overline{INT}$ , all devices will try to respond with their slave address, but an arbitration process ensures that only the lowest address will be received by the host.

After sending its slave address, the first device will then clear its  $\overline{INT}$  output. The host can then check if the  $\overline{INT}$  is still low and send the general call again if necessary until all devices asserting  $\overline{INT}$  have responded.

The ARA function can be disabled by setting bit 2 of the Configuration Register (address 01h).

# **Preliminary Technical Data**

#### TEMPERATURE MEASUREMENT SYSTEM

#### INTERNAL TEMPERATURE MEASUREMENT

The ADM1029 contains an on-chip bandgap temperature sensor, whose output is digitised by the on-chip ADC. The temperature data is stored in the Temp0 Value Register (address A0h). As both positive and negative temperatures can be measured, the temperature data is stored in two's complement format, as shown in Table 2. Theoretically, the temperature sensor and ADC can measure temperatures from  $-128^{\circ}$ C to  $+127^{\circ}$ C with a resolution of 1°C, but temperatures outside the operating temperature range of the device cannot be measured by the internal sensor.

#### EXTERNAL TEMPERATURE MEASUREMENT

The ADM1029 can measure the temperature of one or two external diode sensor or diode-connected transistor, connected to pins 13 and 14 and/or 16 and 17. The data from the temperature measurements is stored in the Temp1 and Temp2 Value Registers (addresses A1h and A2h).

If two external temperature measurements are not required, then pins 16 and 17 can be re-configured as general-purpose logic I/O pins, as explained later.

The forward voltage of a diode or diode-connected transistor, operated at a constant current, exhibits a negative temperature coefficient of about  $-2mV/^{\circ}C$ . Unfortunately, the absolute value of  $V_{be}$ , varies from device to device, and individual calibration is required to null this out, so the technique is unsuitable for mass-production.

The technique used in the ADM1029 is to measure the change in  $V_{be}$  when the device is operated at two different currents.

This is given by:

$\Delta V_{be} = KT/q \ x \ ln(N)$

where:

K is Boltzmann's constant

q is charge on the carrier

T is absolute temperature in Kelvins

N is ratio of the two currents

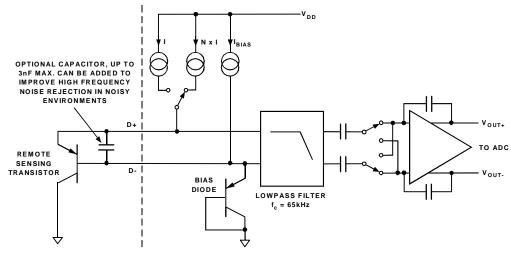

Figure 5 shows the input signal conditioning used to measure the output of an external temperature sensor. This figure shows the external sensor as a substrate transistor, provided for temperature monitoring on some microprocessors, but it could equally well be a discrete transistor.

If a discrete transistor is used, the collector will not be grounded, and should be linked to the base. If a PNP transistor is used the base is connected to the D- input and the emitter to the D+ input. If an NPN transistor is used, the emitter is connected to the D- input and the base to the D+ input.

Figure 5. Signal Conditioning for Remote Diode temperature Sensors

To prevent ground noise interfering with the measurement, the more negative terminal of the sensor is not referenced to ground, but is biased above ground by an internal diode at the D- input. As the sensor is operating in a noisy environment, C1 is provided as a noise filter. See the section on layout considerations for more information on C1.

To measure  $\Delta V_{be}$ , the sensor is switched between operating currents of I and N x I. The resulting waveform is passed through a 65kHz lowpass filter to remove noise, thence to a chopper-stabilized amplifier that performs the functions of amplification and rectification of the waveform to produce a DC voltage proportional to  $\Delta V_{be}$ . This voltage is measured by the ADC to give a temperature output in 8-bit two's complement format. To further reduce the effects of noise. digital filtering is performed by averaging the results of 16 measurement cycles. An external temperature measurement takes nominally 9.6ms.

The results of external temperature measurements are stored in 8 bit, twos-complement format, as illustrated in Table 2.

#### **OFFSET REGISTERS**

Digital noise and other error sources can cause offset errors in the temperature measurement, particularly on the remote sensors. The ADM1029 offers a way to minimize these effects. The offsets on the three temperature channels can be measured during system characterization and stored as two's complement values in three offset registers at addresses 30h to 32h. The offset values are automatically added to, or subtracted from, the temperature values, depending on whether the two's complement number corresponds to a positive or negative offset. Offset values from  $-15^{\circ}$ C to  $+15^{\circ}$ C are allowed.

The default value in the offset registers is zero, so if no offsets are programmed the temperature measurements are unaltered.

#### **TEMPERATURE** LIMITS

The contents of the Local and Remote Temperature Value Registers (addresses A0h to A2h) are compared to the contents of the High and Low Limit Registers at addresses 90h to 92h and 98h to 9Ah. How the ADM1029 responds to overtemperature/undertemperature conditions depends on the status of the Temp0 to Temp2 Control Registers (addresses 40h to 42h). The response of CFAULT, INT and fans speed to temperature events depends on the setting of these registers, as explained later.

#### TABLE 2. TEMPERATURE DATA FORMAT

| Temperature | <b>Digital Output</b> |

|-------------|-----------------------|

| -128 °C     | 1000 0000             |

| -125 °C     | 1000 0011             |

| -100 °C     | 1001 1100             |

| -75 °C      | 1011 0101             |

| -50 °C      | 1100 1110             |

| -25 °C      | 1110 0111             |

| 0 °C        | 0000 0000             |

| +10 °C      | 0000 1010             |

| +25 °C      | 0001 1001             |

| +50 °C      | 0011 0010             |

| +75 °C      | 0100 1011             |

| +100 °C     | 0110 0100             |

| +125 °C     | 0111 1101             |

| +127 °C     | 0111 1111             |

#### FAN INTERFACING

The ADM1029 can be interfaced to many types of fan. It can be used simply to control the speed of a two-wire fan. It can measure the speed of a fan with a tach output and it can accept a logic input from fans with a FAULT output. By means of a shorting link in the fan connector it can also determine if a fan is present or not and if fans have been hot-swapped.

The ADM1029 can control or monitor one or two fans. Bits 0 and 1 of the Fans Supported In System Register (03h) tell the ADM1029 how many fans it should be controlling/monitoring.

In the following descriptions "installed" means that the corresponding bit of register 03h is set and the ADM1029 *expects* to see a fan interfaced to it. It does not necessarily mean that the fan is actually, physically connected.

If a fan is installed then events such as a fault output and hot-swapping of the fan can cause  $\overline{INT}$  and  $\overline{CFAULT}$  to be asserted, unless they are masked for that particular event. If a fan is not installed, but is still physically connected to the ADM1029, then these events will be ignored as far as asserting  $\overline{INT}$  or  $\overline{CFAULT}$  goes, but will still be reflected in the corresponding Fan Status Register.

Setting bit 0 indicates that fan 0 is installed and is set to 1 at power up by default. Setting bit 1 indicates that fan 1 is installed and depends on the state of pin 18 (TMIN/IN-STALL) at power up.

If two fans are installed then bit 0 would be 1 by default and pin 18 would be tied high\* to set bit 0. If only one fan is installed then it would normally be fan 0 and pin 18 would be tied low\* to clear bit 1. However, both these bits can be modified by writing to the register, so it is perfectly possible to have fan 1 installed and not fan 0, or even no fans at all installed.

\*Note that pin 18 also sets TMIN for automatic fan speed control. If this function is used then pin 18 would be set to some other level according to Table 1.

#### FAULT INPUTS/OUTPUTS

The ADM1029 can be used with fans that have a fault output that indicates if the fan has stalled or failed. If one or both of the FAULT inputs (pin 2 or 23) goes low then both  $\overline{\text{INT}}$  and  $\overline{\text{CFAULT}}$  will be asserted.

Events on the fault inputs are also reflected in bits 2 and 3 of the corresponding Fan Status Registers at addresses 10h and 11h. Bit 2 reflects the inverse state of the FAULT pin (0 if FAULT high, 1 of FAULT low), whilst bit 3 is latched high if a FAULT input goes low. It must be cleared by writing a zero to it.

If the fan(s) being used do not have a FAULT output, then the FAULT input(s) on the ADM1029 should be tied to  $V_{\rm CC}$ .

The FAULT pins can also be configured as open-drain outputs by setting bit 5 of the corresponding Fan Control Register (18h or 19h). If a FAULT pin is configured as an output it will still function as an input. This means that when a fault input occurs it will be latched low by the fault output, even if the fault input is removed. The fault output can be used to drive a fan failure indicator such as a LED.

If the FAULT pin is used as an output, then any input to the FAULT pin should also be open-drain. This will avoid the fault input trying to source a high current into the FAULT pin if the fault input goes high whilst the fault output is low.

#### FAN PRESENT INPUTS

The fan PRESENT signal is implemented by a shorting link to ground in the fan connector. When the fan is plugged in, the correspnding PRESENT input (pin 4 or 21) on the ADM1029 is pulled low. If the fan is unplugged the PRESENT input will be pulled high. INT and CFAULT will be asserted (unless masked) and the event will be reflected in bits 0 and 1 of the corresponding Fan Status Register.

Appearance or disappearance of a  $\overrightarrow{\text{PRESENT}}$  input signal during normal operation signals to the ADM1029 that a fan has been hot plugged or unplugged.  $\overrightarrow{\text{INT}}$  and  $\overrightarrow{\text{CFAULT}}$  will be asserted (unless masked). When a fan is hot plugged, bit 7 of the corresponding Fan Status Register will be set.

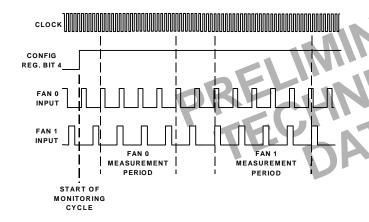

### FAN SPEED MEASUREMENT

The fan counter does not count the fan tach output pulses directly, because at low fan speeds it would take several seconds to accumulate a reasonably large and accurate count. Instead, the period of the fan revolution is measured by gating an on-chip oscillator into the input of an 8-bit counter.

The fan speed measuring circuit is initialized on the first rising edge of a fan tach pulse after monitoring is enabled by setting bit 4 of the Configuration Register. It then starts counting on the rising edge of the second tach pulse and counts for four fan tach periods, until the rising edge of the sixth tach pulse, or until the counter overranges if the fan tach period is too long. After the speed of the first fan has been measured, the speed of the second fan (if installed) will be measured in the same way. The measurement cycle will repeat until monitoring is disabled. The fan speed measurements are stored in the Fan Tach Value registers at addreses 70h and 71h.

If both fans are installed then Fan 0 will be measured first. If only one fan is installed then the ADM1029 will still try to measure both fans, starting with Fan 0, but the measurement on the non-installed fan will time out when the Fan 1 Tach Value count overranges.

The fan speed count is given by:

Count =  $f \times 4 \times 60/R/N$

Where:

f is oscillator frequency in Hz

factor 4 is because 4 tach periods are counted

factor 60 is to convert minutes to seconds

R = fan speed in r.p.m.

N is number of tach pulses per revolution

The frequency of the oscillator can be adjusted to suit the expected frequency range of the fan tach pulses, which depends on the fan speed and the number of tach pulses produced for each revolution of the fan, which is either 1, 2 or 4. The oscillator frequency is set by bits 7 and 6 of the Fan Speed Registers (68h for Fan 0 and 69h for Fan 1).

#### **TABLE 3. OSCILLATOR FREQUENCIES**

| Bit 7 | Bit 6 | Oscillator Frequency (Hz) |

|-------|-------|---------------------------|

| 0     | 0     | Measurement disabled      |

| 0     | 1     | 470                       |

| 1     | 0     | 940                       |

| 1     | 1     | 1880                      |

Figure 6. Fan Speed Measurement

#### FAN SPEED LIMITS

Fans in general will not overspeed if run from the correct voltage, so the failure condition of interest is underspeed due to electrical or mechanical failure. For this reason only low-speed limits are programmed into the Tach Limit Registers for the fans. These registers are at address 78h for fan 0 and 79h for fan 1. It should be noted that, since fan period rather than speed is being measured, the fan speed count will be larger the lower the fan speed. Therefore a fan failure fault will occur when the measurement *exceeds* the limit value.

To get the most accurate fan failure indication, the oscillator frequency should be chosen to give as large a limit value as possible without the counter overranging. A count close to 3/4 full-scale or 191 is the optimum value.

For example, if a fan produces two tach pulses per revolution and the fan failure speed is to be 600 r.p.m. the oscillator frequency should be set to 940Hz. This will give a count at the fail speed of:

$940 \times 4 \times 60/600/2 = 188$

If the oscillator frequency was only 470Hz then the count would be only 94, whilst an oscillator frequency of 1880Hz cannot be used because the count would be 376 and the counter would overrange.

#### REV. PrF

# ADM1029

FAN MONITORING CYCLE TIME

Five complete tach periods are required to carry out a fan speed measurement Therefore, if the start of a fan measurement just misses a rising edge, the measurement can taken almost six tach periods for each fan.

The worst-case monitoring cycle time is when both fans are under speed and the fan speed counter counts up to its maximum value. The actual count takes 256 oscillator pulses over 4 tach periods, plus a further two tach periods or 128 oscillator pulses before the count starts. The total monitoring cycle time is therefore:

$t_{MEAS} = 384/f_{OSC(FAN 0)} + 384/f_{OSC(FAN 1)}$

In order to read a valid result from the Fan Tach Value Registers, the total monitoring time allowed after starting the monitoring cycle should be greater than this.

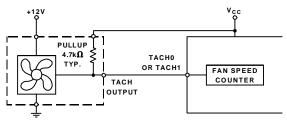

### TACH SIGNAL CONDITIONING

Signal conditioning in the ADM1029 accommodates the slow rise and fall times typical of fan tachometer outputs. The maximum input signal range is 0 to +5V even if  $V_{CC}$  is less than 5V. In the event that these inputs are supplied from fan outputs which exceed 0 to +5V, either resistive attenuation of the fan signal or diode clamping must be included to keep inputs within an acceptable range.

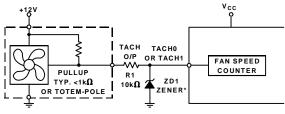

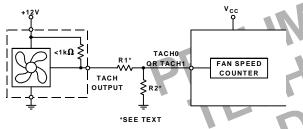

Figures 7a to 7d show circuits for most common fan tach outputs.

If the fan tach output has a resistive pullup to  $V_{CC}$  then it can be connected directly to the fan input, as shown in figure 7a.

Figure 7a. Fan With Tach Pullup To +V<sub>CC</sub>.

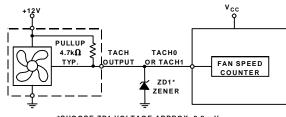

If the fan output has a resistive pullup to +12V (or other voltage greater than 6.5V) then the fan output can be clamped with a zener diode, as shown in figure 7b. The zener voltage should be chosen so that it is greater than  $V_{\rm IH}$  but less than 6.5V, allowing for the voltage tolerance of the zener. A value of between 3V and 5V is suitable.

\*CHOOSE ZD1 VOLTAGE APPROX. 0.8 x  $V_{CC}$

Figure 7b. Fan with Tach. Pullup to Voltage >6.5V e.g. 12V) Clamped with Zener Diode

If the fan has a strong pullup (less than  $1k\Omega$ ) to +12V, or a totem-pole output, then a series resistor can be added to limit the zener current, as shown in figure 7c. Alternatively,

Preliminary Technical Data

a resistive attenuator may be used, as shown in figure 7d.

R1 and R2 should be chosen such that:

$$2V \ < \ V_{PULLUP} \ x \ R2/(R_{PULLUP} \ + \ R1 \ + \ R2) \ < \ 5V$$

The fan inputs have an input resistance of nominally  $160k\Omega$  to ground, so this should be taken into account when calculating resistor values.

With a pullup voltage of 12V and pullup resistor less than  $1k\Omega$ , suitable values for R1 and R2 would be  $100k\Omega$  and  $47k\Omega$ . This will give a high input voltage of 3.83V.

\*CHOOSE ZD1 VOLTAGE APPROX. 0.8 x  $\rm V_{CC}$

Figure 7c. Fan with Strong Tach. Pullup to  $>V_{CC}$  or Totem-Pole Output, Clamped with Zener and Resistor

Figure 7d. Fan with Strong Tach. Pullup to >V<sub>cc</sub> or Totem-Pole Output, Attenuated with R1/R2

#### FAN SPEED CONTROL

Fan speed is controlled using pulse-width modulation (PWM). The PWM outputs (pins 1 and 20) give a pulse output with a programmable frequency (default 250Hz) and a duty-cycle defined by the contents of the relevant fan speed register, or by the automatic fan speed control when this mode is enabled. The speed at which a fan runs is determined by fault conditions and the settings of various control and mask registers.

A fan can only be driven if it is defined as being supported by the controller in register 02h. The ADM1029 supports up to 2 fans, so bits 0 and 1 of this register are permanently set. This register is read-only.

A fan will only be driven if it is defined as being supported by the system in register 03h. If bit 0 of this register is set it indicates that Fan 0 is installed. This is the power-on default. If bit 1 is set it indicates that Fan 1 is installed. This bit is set by the state of pin 18 at power-up. This register is read/write and the default/power-on setting can be overwritten. If a fan is not supported in register 03h it will not be driven, even if it is physically installed.

The PWM outputs are open-drain outputs. They require pullup resistors and must be amplified and buffered to drive the fans.

#### Normal Speed

The normal fan speed is set by the four LSBs of the Fan 0 and Fan 1 Normal/Alarm Speed Registers (addresses 60h, 61h). These bits also set the minimum speed at which a fan will run in automatic control mode. The power-on default for these bits is 0101 (5h). This corresponds to 33% PWM duty-cycle, which is the lowest speed at which most fans will run reliably.

Fan(s) will run at normal speed if there is no fault condition, automatic fan speed is disabled and there are no other overriding conditions.

#### **Alarm Speed**

Alarm speed is set by the four MSBs of the Fan 0 and Fan 1 Normal/Alarm Speed Registers (addresses 60h, 61h). Fan(s) will run at alarm speed if any of the following conditions occurs, assuming the condition has not been masked in one of the fan mask registers:

- Setting bit 0 of register 07h forces Fan 0 to run at alarm speed.

- Setting bit 1 of register 07h forces Fan 1 to run at alarm speed.

If monitoring is disabled by clearing bit 4 of the Configuration Register, all fans controlled by the ADM1029 will run at alarm speed.

When a GPIO pin is configured as an input by setting bit 0 of the corresponding GPIO Control Register and bit 4 of the GPIO Control Register is also set, all fans controlled by the ADM1029 will go to alarm speed when the logic input is asserted (high or low depending on the polarity bit, bit 1 of the corresponding GPIO Control Register).

- If bit 7 of a Fan Control Register is set (18h Fan 0, 19h Fan 1) the corresponding fan will go to alarm speed when CFAULT is pulled low by an external source.

- If a tach measurement exceeds the set limit, all fans controlled by the ADM1029 will run at alarm speed.

- If a fan fault input pin is asserted (low), all fans controlled by the ADM1029 will run at alarm speed.

- If bit 1 of a Temp. Control Register is set (40h Local Sensor, 41h Remote 1, 42h Remote 2), all fans controlled by the ADM1029 will go to alarm speed if the corresponding temperature high limit is exceeded.

- If bit 5 of a Temp. Control register is set, all fans controlled by the ADM1029 will go to alarm speed if a temperature input crosses the corresponding temperature low limit, the direction depending on the setting of bit 3 of the Temp. control register. (0 = alarm when input goes below low limit, 1 = alarm when input goes above low limit).

- If bit 1 of an AIN Control Register is set (50h AIN0, 51h AIN1), all fans controlled by the ADM1029 will go to alarm speed if the corresponding AIN high limit is exceeded.

- If bit 5 of an AIN Control register is set, all fans controlled by the ADM1029 will go to alarm speed if an analog input crosses the corresponding AIN low limit,

the direction depending on the setting of bit 3 of the AIN control register. (0 = alarm when input goes below low limit, 1 = alarm when input goes above low limit).

- If a thermal override occurs while the ADM1029 is in sleep mode, all fans controlled by the ADM1029 will run at alarm speed.

#### **Hot Plug Speed**

Hot plug speed is set by the four LSBs of the Fan 0 and Fan 1 Hot Plug Speed Registers (addresses 68h and 69h). The PWM frequency is set by bits 4 and 5 of these registers, while bits 6 and 7 set the number of pulse per revolution for fan speed measurement.

Fan(s) will run at hot plug speed if any of the following conditions occurs, assuming the condition has not been masked on one of the fan mask registers:

- If a fan is unplugged then the other fan (if any) controlled by the ADM1029 will run at hot plug speed.

- Setting bit 0 of register 08h forces Fan 0 to run at hot plug speed.

- Setting bit 1 of register 08h forces Fan 1 to run at hot plug speed.

- When a GPIO pin is configured as an input by setting bit 0 of the corresponding GPIO Control Register and bit 5 of the GPIO Control Register is also set, all fans controlled by the ADM1029 will go to hot plug speed when the logic input is asserted (high or low depending on the polarity bit, bit 1 of the corresponding GPIO Control Register).

- If bit 6 of a Fan Control Register is set (18h for Fan 0, 19h for Fan 1) the corresponding fan will go to hot plug speed when CFAULT is pulled low by an external source.

Note: If operating conditions and register settings are such that both alarm speed and hot plug speed would be triggered, which one takes priority is determined by bit 5 of the Fan 0 and Fan 1 Status Registers (addresses 10h and 11h). If this bit is set then hot plug speed takes priority. If it is cleared then alarm speed takes priority.

#### **Full Speed**

Fans will run at full speed if the corresponding bits in the Fan Full Speed Register (address 09h) are set, bit 0 for Fan 0 and bit 1 for Fan 1.

#### **Fan Mask Registers**

The effect of various conditions on fan speed can be enabled or disabled by mask registers. In all these registers, setting bit 0 of the register enables Fan 0 to go to alarm speed or hot plug speed if the corresponding event occurs, while setting bit 1 enables Fan 1. Clearing these bits masks the effect of the corresponding event on fan speed.

Registers 20h and 21h are Fan Fault to Fan Mask Registers. Bits 0 and 1 of register 20h enable (bit set) or mask (bit clear) the effect of a Fan 0 fault (underspeed or fault input) on Fan 0 and Fan 1 speed. Similarly, Bits 0 and 1 of register 21h enable (bit set) or mask (bit clear) the effect of a Fan 1 fault on Fan 0 and Fan 1 speed.

Registers 38h to 3Eh are GPIO to Fan Mask registers.

Bits 0 and 1 of these registers enable or mask the effect of an AIN fault on Fan 0 and Fan 1 speed.

Registers 48h to 4Ah are Temp. to Fan Mask Registers. Bits 0 and 1 of these registers enable or mask the effect of Temp 0 (local sensor), Temp 1 and Temp 2 faults on Fan 0 and Fan 1 speed. These registers also determine which temperature channel controls which fan in automatic fan speed control mode, as described later.

Registers 58h and 59h are AIN to Fan Mask Registers. Bits 0 and 1 of these registers enable or mask the effect of an AIN fault on Fan 0 and Fan 1 speed.

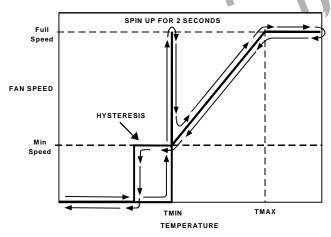

#### AUTOMATIC FAN SPEED CONTROL

The ADM1029 offers a simple method of controlling fan speed according to temperature without intervention from the host processor.

Operation of the automatic fan speed control is controlled by 10 registers.

Setting Bit 4 of the Configuration Register (address 01h) enables monitoring, which is necessary for automatic fan speed control.

Automatic fan speed control can be set up so that different temperature sensors can control either or both fans.

Bits 0 and 1 of the three Temp. to Fan Mask Registers (addresses 48h to 4Ah) determine which temperature channel controls which fan(s). As there are six bits there are theoretically 64 possibilities for which temperature sensors control which fans, but only a subset of these are supported, as explained in the description of the Temp. to Fan Mask Registers.

If more than one temperature channel is set to control a fan the channel calculating the highest speed takes priority and the fan speed is set according to the temperature measured by that channel.

The TMIN registers (addresses 80h to 82h) contain minimum temperature values for the three temperature channels. This is the temperature at which a fan will start to operate when the temperature sensed by the controlling sensor exceeds TMIN.

TMIN can be set by writing a two's complement temperature value to the TMIN registers, or a power-up default value can be programmed, as decribed later.

The temperature range over which automatic fan speed control will operate for a particular temperature sensor is defined by the four LSB's of the three TRANGE/THYST registers. (addresses 88h to 8Ah).

# TABLE 4. AUTOMATIC FAN SPEED CONTROL TEM-PERATURE RANGES

| Temperature Range (°C) |

|------------------------|

| 5                      |

| 10                     |

| 20                     |

| 40                     |

| 80                     |

|                        |

When the temperature exceeds TMIN, the fan is spun up for two seconds with 100% PWM duty-cycle. It is then run at the speed set by the Fan (X) Speed 1 Registers (60h and 61h). As the temperature increases, the PWM duty-cycle will increase until it reaches 100% when the temperature reaches TMIN + TRANGE.

The four MSBs of the TRANGE/THYST registers contain a temperature hysteresis value, which can be set programmed from 0000 to 1111 (0 to 15°C). If the temperature falls, the fan will not turn off until the temperature has fallen to TMIN – THYST. This prevents the fan from cycling on and off continuously when the temperature is close to TMIN.

Figure 8. Automatic Fan Speed Control Transfer Function

Automatic fan control can also be enabled in hardware by pin 18 (TMIN/INSTALL). This is an 8-level input with multiple functions, which is sampled only at power-up.

If only one fan is installed, the voltage on pin 18 should be less than  $V_{CC}/2$ , which clears bit 1 of register 03h. Within this voltage range, four voltage levels define the minimum temperature at which the fan will operate in automatic speed control mode.

If two fans are installed, the voltage on pin 18 should be between  $V_{CC}/2$  and  $V_{CC}$ , which sets bit 1 of register 03h. Within this voltage range, four voltage levels define the minimum temperature at which the fans will operate in

# **Preliminary Technical Data**

automatic speed control mode.

Resistor values for setting the voltage on pin 18 are given in Table 1. If automatic fan speed control is not used Pin 18 can simply be strapped to ground  $\text{orV}_{CC}$  depending on how many fans are installed.

When automatic fan speed control is enabled at power-up by the TMIN/INSTALL pin, bit 4 of the Configuration register is set to enable monitoring, and bits 0 and 1 of all Temp. to Fan Mask Registers are set, so any temperature channel will control all fans that are installed. Note:

If automatic fan speed control is enabled and an event occurs that would cause a fan to go to alarm or hot plug speed (e.g. temperature fault), that event will override the automatic fan speed control. If the event affects only one fan, the other fan will remain under automatic control.

#### **RESET INPUT**

Pin 12 is an active-low system RESET. Taking this pin low will generate a system reset, which will reset all registers to their default values.

#### ANALOG INPUTS

Pins 19 and 20 of the ADM1029 are dual-function pins. They may be configured as general-purpose logic I/O pins by setting bits 0 and/or 1 of the GPIO Present/AIN register (address 05h) or as 0 to +2.5V analog inputs by clearing these bits.

In the analog input mode, pins 19 and 20 have an input range of 0 to +2.5V. By suitable input scaling, the analog input may be configured to measure other voltage ranges such as system power supply voltages. If more than one ADM1029 is used in a system, several such voltages may be monitored.

The measured values of AIN0 and AIN 1 are stored in the AIN0 and AIN1 Value registers (addresses B8h and B9h) and are compared to high and low limits stored in the AIN0 and AIN1 High and Low Limit Registers (addresses A8h, A9h and B0h, B1h).

The response of the ADM1029 to an out-of-limit measurement on AIN0 or AIN1 depend on the status of the <u>AIN0 and AIN1 control registers</u>. The response of <u>CFAULT</u>, <u>INT</u> and fan speed to temperature events depends on the setting of these registers, as detailed in the register tables later in this data sheet.

#### ANALOG MONITORING CYCLE

The ADM1029 performs a sequential "round-robin", monitoring cycle on all analog inputs and temperature inputs that are enabled. A conversion on AIN0 or AIN1 takes typically 11.6ms, whilst an external temperature conversion takes 185.6ms.

Conversion is enabled by setting bit 4 of the Configuration register and disabled by clearing this bit.

#### GENERAL PURPOSE LOGIC INPUT/OUTPUTS

The ADM1029 has six dual-function pins (see Pin Function description) that may be configured as general-pur-

pose logic I/O pins by setting the appropriate bit(s) of the GPIO Present Register (address 05h) or as their alternate functions by clearing these bits.

When configured as GPIO pins, each GPIO pin has a Control Register associated with it (registers 28h to 2Eh) that may be used to configure the operation of the pin.

The GPIO pins may be configured as inputs or outputs. When used as inputs, they may be configured to:

- be active high or active low.

- set/clear a bit in the Control Register when GP input is asserted/de-asserted.

- Latch a bit in the control register when GP input is asserted (must be cleared by software).

- assert  $\overline{\text{CFAULT}}$  when GP input asserted.

- assert  $\overline{\text{INT}}$  when GP input asserted.

- set fan(s) to alarm speed when GP input asserted.

- set fan(s) to hot-plug speed when GP input asserted.

When used as outputs, they may be configured to:

- be active high or low

- be asserted if a High Temperature Limit is exceeded.

- be asserted if a temperature measurement falls below a low limit.

- be asserted if a fan fault is detected.

- be asserted if a fan tach limit is exceeded.

- be asserted if an AIN high limit is exceeded.

- be asserted if an analog input falls below a low limit.

### CFAULT OUTPUT

The Cascade Fault output ( $\overline{CFAULT}$ ), is an open-drain, active low output, intended to communicate fault conditions to other ADM1029's in a system, without the intervention of the host processor. The other ADM1029's may then adjust their fans' speed to compensate, depending on the settings of various registers.

CFAULT is asserted if any of the following conditions occurs:

- A hot plug event.

- Setting bit 5 of the Configuration Register (address 01h) forces CFAULT to be asserted.

- When a GPIO pin is configured as an input by setting bit 0 of the corresponding GPIO Control Register and bit 2 of the GPIO Control Register is also set, CFAULT will be asserted when the logic input is asserted (high or low depending on the polarity bit, bit 1 of the corresponding GPIO Control Register).

- If bit 0 of a Temp. Control Register is set (40h Local Sensor, 41h Remote 1, 42h Remote 2), CFAULT will be asserted if the corresponding temperature high limit is exceeded.

- If bit 4 of a Temp. Control register is set,  $\overline{CFAULT}$  will be asserted if a temperature input crosses the corresponding temperature low limit, the direction depending on the setting of bit 3 of the Temp. control register. (0 =  $\overline{CFAULT}$  when input goes below low limit, 1 =

CFAULT when input goes above low limit).

- If bit 0 of a Fan Control Register (18h or 19h) is set,  $\overline{CFAULT}$  will be asserted when a tach measurement for the corresponding fan exceeds the set limit.

- If bit 0 of a Fan Control Register (18h or 19h) is set,  $\overline{CFAULT}$  will be asserted, when the fan fault input pin for the coresponding fan is asserted (low).

- If bit 0 of an AIN Control Register is set (50h AIN0, 51h AIN1), CFAULT will be asserted if the corresponding AIN high limit is exceeded.

- If bit 4 of an AIN Control register is set,  $\overline{CFAULT}$  will be asserted if an analog input crosses the corresponding AIN low limit, the direction depending on the setting of bit 3 of the AIN control register. (0 =  $\overline{CFAULT}$  when input goes below low limit, 1 =  $\overline{CFAULT}$  when input goes above low limit).

#### INTERRUPT (INT) OUTPUT

The INT output is an open-drain output with selectable polarity, intended to communicate fault conditions to the host processor. The polarity is set to active low by clearing bit 7 of the Configuration Register (address 01h) or to active high by setting this bit.

**INT** is asserted if any of the following conditions occurs:

A hot plug event.

Setting bit 6 of the Configuration Register (address 01h) forces INT to be asserted.

- When a GPIO pin is configured as an input by setting bit 0 of the corresponding GPIO Control Register and bit 3 of the GPIO Control Register is also set, INT will be asserted when the logic input is asserted (high or low depending on the polarity bit, bit 1 of the corresponding GPIO Control Register).

- If bit 2 of a Temp. Control Register is set (40h Local Sensor, 41h Remote 1, 42h Remote 2), INT will be asserted if the corresponding temperature high limit is exceeded.

- If bit 6 of a Temp. Control register is set,  $\overline{\text{INT}}$  will be asserted if a temperature input crosses the corresponding temperature low limit, the direction depending on the setting of bit 3 of the Temp. control register. (0 =  $\overline{\text{INT}}$  when temperature goes below low limit, 1 =  $\overline{\text{INT}}$  when temperature goes above low limit).

- If bit 1 of a Fan Control Register (18h or 19h) is set,  $\overline{INT}$  will be asserted when a tach measurement for the corresponding fan exceeds the set limit .

- If bit 1 of a Fan Control Register (18h or 19h) is set,  $\overline{INT}$  will be asserted when the fan fault input pin for the corresponding fan is asserted (low).

- If bit 2 of an AIN Control Register is set (50h AIN0, 51h AIN1),  $\overline{INT}$  will be asserted if the corresponding AIN high limit is exceeded.

- If bit 6 of an AIN Control register is set, INT will be

# ADM1029

asserted if the corresponding analog input crosses its AIN low limit, the direction depending on the setting of bit 3 of the AIN control register. ( $0 = \overline{INT}$  when input goes below low limit,  $1 = \overline{INT}$  when input goes above low limit).

#### FREE-WHEELING FAN TEST

Where two fans are tightly coupled in a duct, a fan that is turned off or failed may "windmill" and freewheel at close to normal speed. To detect such a failed fan, it is necessary to power up one fan at a time and check the tach output. With no other airflow to drive it, a failed fan will not rotate. To carry out this test, all fans in the system are turned off. The test is then initiated on each ADM1029 in turn by setting bit 1 of the Configuration register (address 0Bh). The ADM1029 will spin up each fan it controls in turn, and measure the tach output. If the tach output is below the limit programmed in the Fan Tach Limit Register (address 31h for fan 1 and 32h for fan 2), then the Fanfail bit will be set in the Configuration register (bit 2 for fan 1 and bit 3 for fan 2). This test takes about 10 seconds for each ADM1029.

#### LAYOUT CONSIDERATIONS

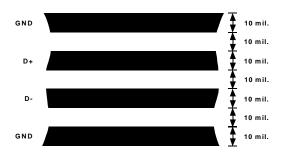

Digital boards can be electrically noisy environments, and care must be taken to protect the analog inputs from noise, particularly when measuring the very small voltages from a remote diode sensor. The following precautions should be taken:

- 1. Place the ADM1029 as close as possible to the remote sensing diode. Provided that the worst noise sources such as clock generators, data/address buses and CRTs are avoided, this distance can be 4 to 8 inches.

- 2. Route the D+ and D- tracks close together, in parallel, with grounded guard tracks on each side. Provide a ground plane under the tracks if possible.

- 3. Use wide tracks to minimize inductance and reduce noise pickup. 10 mil track minimum width and spacing is recommended.

Figure 9. Arrangement of Signal Tracks

4. Try to minimize the number of copper/solder joints, which can cause thermocouple effects. Where copper/ solder joints are used, make sure that they are in both the D+ and D- path and at the same temperature.

Thermocouple effects should not be a major problem as 1°C corresponds to about 240 $\mu$ V, and thermocouple voltages are about 3 $\mu$ V/°C of temperature difference.

## **Preliminary Technical Data**

Unless there are two thermocouples with a big temperature differential between them, thermocouple voltages should be much less than  $200\mu$ V.

- 5. Place  $0.1\mu F$  bypass and 1000pF input filter capacitors close to the ADM1029.

- 6. If the distance to the remote sensor is more than 8 inches, the use of twisted pair cable is recommended. This will work up to about 6 to 12 feet.

- 7. For really long distances (up to 100 feet) use shielded twisted pair such as Belden #8451 microphone cable. Connect the twisted pair to D+ and D- and the shield to GND close to the ADM1029. Leave the remote end of the shield unconnected to avoid ground loops.

Because the measurement technique uses switched current sources, excessive cable and/or filter capacitance can affect the measurement. When using long cables, the filter capacitor may be reduced or removed.

Cable resistance can also introduce errors.  $1\Omega$  series resistance introduces about 0.5°C error.

CAL

## **REGISTER MAP**

| Address | Name                          | Default Value | Description                                                                                                                                                    |

|---------|-------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00      | Main Status Register          | 00h           | Contains the status of various fault conditions.                                                                                                               |

| 01      | Config Register               | 0000 0000     | Configures the operation of the device.                                                                                                                        |

| 02      | Fan Supported By controller   | 03h           | Contains the number of fans the device can support.                                                                                                            |

| 03      | Fans supported in system      | 0000 00?1     | Contains the number of fans actually supported by the device.                                                                                                  |

| 04      | GPIOs Supported By Controller | 7Fh           | Contains the number of GPIO pins the device can support.                                                                                                       |

| 05      | GPIO Present / AIN            | 0????111      | Used to configure GPIO pins as GPIO or as their alternate function.                                                                                            |

| 06      | Temp Devices Installed        | 0000 0??1     | Contains number of temperature sensors installed.                                                                                                              |

| 07      | Set Fan X Alarm Speed         | 00h           | Writing to appropriate bit(s) makes fan(s) run at alarm speed.                                                                                                 |

| 08      | Set Fan X Hot Plug Speed      | 00h           | Writing to appropriate bit(s) makes fan(s) run at hot-<br>plug speed.                                                                                          |

| 09      | Set Fan X Full Speed          | 00h           | Writing to appropriate bit(s) makes fan(s) run at full-speed.                                                                                                  |

| 0B      | S/W RESET                     | 00h           | Writing A6h to this register causes a a software reset.                                                                                                        |

| 0 D     | Manufacturer's ID             | 41h           | This register contains the manufacturer's ID code for the device.                                                                                              |

| 0 E     | Major/Minor Revision          | 00h           | Contains the manufacturer's code for major and mino revisions to the device in two nibbles                                                                     |

| 0 F     | Manufacturer's Test Register  | 00h           | This register is used by the manufacturer for test<br>purposes. It should not be read from or written to in<br>normal operation.                               |

| 10      | Fan0 Status                   | 0000 0?0?     | Contains status information for FAN 0                                                                                                                          |

| 11      | Fan1 Status                   | 0000 0?0?     | Contains status information for FAN 1                                                                                                                          |

| 18      | Fan0 Control                  | BFh           | Sets operation of INT, CFAULT etc. for FAN 0 fau                                                                                                               |