**OBJECTIVE SPECIFICATION**

82S400/400A - I • 82S401/401A - I

### DESCRIPTION

The 82S400 and 82S401, with typical access time of 45ns, are ideal for cache buffer applications and for systems requiring very high speed main memory. The 82S400A and 82S401A are devices selected for speed compatibility with industry standard 1024-bit RAMs having 45ns access time.

Both devices require a single +5V power supply, feature very low current pnp input structures, and include on-chip decoding and a chip enable input for ease of memory expansion. They feature either open collector or tri-state outputs for optimization of word expansion in bused organizations.

# **APPLICATIONS**

- High speed main frame

- Cache memory

- Buffer storage

- Writable control store

### **FEATURES**

- Address access time:

82S400/401: 70ns max

82S400A/401A: 45ns max

- Write cycle time: 70ns max

- Power dissipation: 0.12mW/bit typ

- Input loading: -150μA max

- On-chip address decoding

- Output options:

82S400: Open collector

- 82S401: Tri-state

Non-inverting output

- Blanked output during Write

- Fully TTL compatible

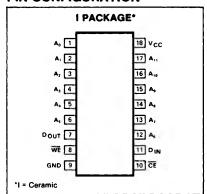

### PIN CONFIGURATION

# **TRUTH TABLE**

|           |     | WE |     | DOUT        |             |  |  |

|-----------|-----|----|-----|-------------|-------------|--|--|

| MODE      | CE  |    | DIN | 82S400      | 82\$401     |  |  |

| Read      | 0   | 1  | Х   | Stored data | Stored data |  |  |

| Write "0" | 1 0 | 0  | 0   | 1           | High-Z      |  |  |

| Write "1" | 0   | 0  | 1   | 1           | High-Z      |  |  |

| Disabled  | 1   | ×  | ×   | 1           | High-Z      |  |  |

X = Don't care

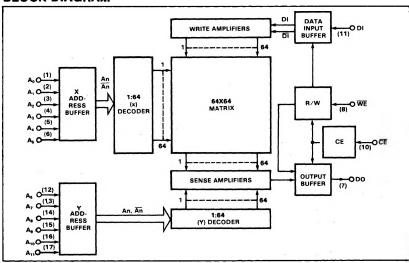

## **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

|                                    | PARAMETER1                                            | RATING                  | UNIT |

|------------------------------------|-------------------------------------------------------|-------------------------|------|

| Vcc                                | Power supply voltage                                  | +7                      | Vdc  |

| VIN                                | Input voltage                                         | +5.5                    | Vdc  |

| V <sub>ОН</sub><br>V <sub>О</sub>  | Output voltage<br>High (82S400)<br>Off-state (82S401) | <br>+5.5<br>+5.5        | Vdc  |

| T <sub>A</sub><br>T <sub>STG</sub> | Temperature range<br>Operating<br>Storage             | 0 to +75<br>-65 to +150 | °C   |

**OBJECTIVE SPECIFICATION**

82S400/400A - I • 82S401/401A - I

# DC ELECTRICAL CHARACTERISTICS $0^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +75 $^{\circ}$ C, 4.75V $\leq$ V<sub>CC</sub> $\leq$ 5.25V

|                                      |                                                |     | LIMITS           |      |      |  |

|--------------------------------------|------------------------------------------------|-----|------------------|------|------|--|

| PARAMETER                            | TEST CONDITIONS                                | Min | Typ <sup>2</sup> | Max  | UNIT |  |

| Input voltage                        |                                                |     |                  |      | V    |  |

| VIL Low <sup>1</sup>                 | $V_{CC} = Min$                                 | )   |                  | .85  | 1    |  |

| V <sub>IH</sub> High <sup>1</sup>    | V <sub>CC</sub> = Max                          | 2.0 | 1                |      | 1    |  |

| V <sub>IC</sub> Clamp <sup>1,3</sup> | V <sub>CC</sub> = Min, I <sub>IN</sub> = -12mA |     | -1.0             | -1.5 | ì    |  |

| Output voltage                       | V <sub>CC</sub> = Min                          |     |                  |      | V    |  |

| Vol Low1,4                           | I <sub>OL</sub> = 16mA                         |     | 0.35             | 0.45 |      |  |

| V <sub>OH</sub> High (82S401)1,5     | I <sub>OH</sub> = -2mA                         | 2.4 | }                |      |      |  |

| Input current                        |                                                |     |                  |      | μА   |  |

| I <sub>IL</sub> Low                  | $V_{IN} = 0.45V$                               |     | -25              | -150 | 1    |  |

| l <sub>lH</sub> High                 | $V_{IN} = 5.5V$                                |     | 1 1              | 25   |      |  |

| Output current                       | V <sub>CC</sub> = Max                          |     |                  |      |      |  |

| IOLK Leakage (82S400)6               | $V_{OUT} = 5.5V$                               | l   | 1 1              | 40   | μΑ   |  |

| IO(OFF) Hi-Z state (82S401)          |                                                | Ţ   | 1                | 60   | μΑ   |  |

| •                                    | $V_{OUT} = 0.45V$                              |     | -1               | -60  |      |  |

| los Short circuit (82S40             | $V_{OUT} = 0V$                                 | -20 |                  | -100 | mA   |  |

| Icc Vcc supply current8              | V <sub>CC</sub> = Max                          | }   |                  |      | - mA |  |

|                                      | 0< T <sub>A</sub> < 25° C                      |     | 120              | 155  |      |  |

|                                      | T <sub>A</sub> ≥ 25°C                          |     | 105              | 130  |      |  |

| Capacitance                          | V <sub>CC</sub> = 5.0V                         |     |                  |      | pF   |  |

| Cin Input                            | $V_{IN} = 2.0V$                                |     | 4                |      |      |  |

| Cout Output                          | $V_{OUT} = 2.0V$                               | - 4 | 7                |      |      |  |

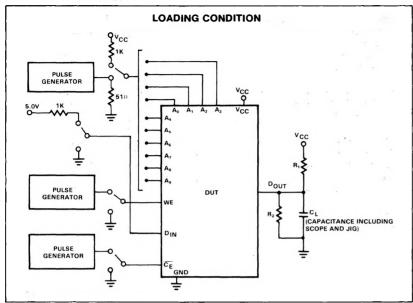

# **AC ELECTRICAL CHARACTERISTICS** $0^{\circ} \le T_{A} \le +75^{\circ} C$ , $4.75V \le V_{CC} \le 5.25V$ , $R_{1} = 270\Omega$ , $R_{2} = 600\Omega$ , $C_{L} = 30pF$

|                                    |                                                | то               | FROM                        | N82S400A/401A |                  |          | N82S400/401 |                  |          | T    |

|------------------------------------|------------------------------------------------|------------------|-----------------------------|---------------|------------------|----------|-------------|------------------|----------|------|

|                                    | PARAMETER                                      |                  |                             | Min           | Typ <sup>2</sup> | Max      | Min         | Typ <sup>2</sup> | Max      | UNIT |

| TAA                                | Access time                                    | Output           | Address                     |               |                  | 45       | *           | 45               | 70       | ns   |

| TCE                                |                                                | Output           | Chip enable                 | 1             |                  | 30       |             | 30               | 45       |      |

| T <sub>CD</sub><br>T <sub>WD</sub> | Disable time                                   | Output<br>Output | Chip enable<br>Write enable |               |                  | 30<br>30 |             | 30<br>30         | 45<br>45 | ns   |

| Twr                                | Recovery time                                  | Output           | Write enable                |               |                  | 30       |             | 30               | 45       | ns   |

| Twsa<br>Twha                       | Setup and hold time<br>Setup time<br>Hold time | Write enable     | Address                     | 5             |                  |          | 10          | 5                |          | ns   |

| Twsd<br>Twhd                       | Setup time<br>Hold time                        | Write enable     | Data in                     | 35<br>5       |                  |          | 50<br>10    | 35<br>5          |          |      |

| Twsc<br>Twhc                       | Setup time<br>Hold time                        | Write enable     | CE                          | 5             |                  |          | 10          | 5                |          |      |

| Twp                                | Pulse width <sup>9</sup><br>Write enable       |                  |                             | 35            |                  |          | 50          | 35               |          | ns   |

### NOTES

- 1. All voltage values are with respect to network ground terminal.

- 2. All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> 25° C.

- 3. Test each input one at a time.

- 4. Measured with a logic low stored. Output sink current is supplied through a resistor to Vcc.

- 5. Measured with VIL applied to CE and a logic high stored.

- 6. Measured with V<sub>IH</sub> applied to CE.

- 7. Duration of the short circuit should not exceed 1 second.

- Icc is measured with the write enable and memory enable inputs grounded, all other inputs at 4.5V, and the output open.

- 9. Minimum required to guarantee a Write Into the slowest bit.

- 10. The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warm-up. Typical thermal resistance values of the package at maximum temperature are:

- $\Theta_{JA}$  junction to ambient at 400fpm air flow 50°C/watt

- $\Theta_{JA}$  junction to ambient still air 90° C/watt

- θ<sub>JA</sub> junction to case 20°C/watt

**OBJECTIVE SPECIFICATION**

82S400/400A - I • 82S401/401A - I

# **TEST LOAD CIRCUIT**

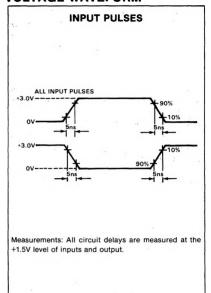

# **VOLTAGE WAVEFORM**

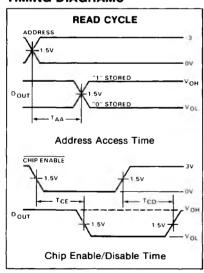

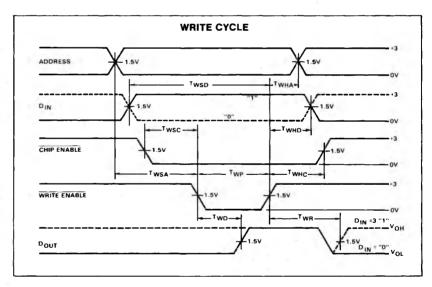

# **TIMING DIAGRAMS**

Twp

# **TIMING DEFINITIONS**

Twr Delay between end of Write Enable pulse and when Data Output becomes valid (assuming Address still valid—not as shown).

TCE Delay between beginning of Chip Enable low (with Address valid) and when Data Output becomes valid.

T<sub>CD</sub> Delay between when Chip Enable becomes high and Data Output is in off state.

T<sub>AA</sub> Delay between beginning of valid

Address (with Chip Enable low) and when Data Output becomes valid.

Required delay between beginning of valid Chip Enable and beginning of Write Enable pulse.

TWHD Required delay between end of Write Enable pulse and end of valid Input Data.

Twsc

TWP

TWSA

Width of Write Enable pulse.

Required delay between beginning of valid Address and beginning of Write Enable pulse.

Twsp Required delay between beginning of valid Data Input and end of Write Enable pulse.

Delay between beginning of Write Enable pulse and when Data Output is in off state.

TWHC Required delay between end of Write Enable pulse and end of Chip Enable.

Twha Required delay between end of Write Enable pulse and end of valid Address.