## ADVANCE SPECIFICATION

### DESCRIPTION

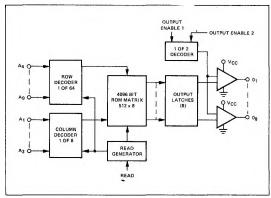

The 2530 is a high speed 4,096-bit Static Read-Only Memory available in a 512x8 organization. This device has TTL compatible inputs and outputs and requires +5V and -12V power supplies. A READ input controls the entry of data from the ROM into output latches. Three-state outputs allow OR tying for implementing larger memories. Two OUTPUT-ENABLES control the eight output devices without affecting address circuitry.

## **FEATURES**

- 512x8 ORGANIZATION

- 625ns TYPICAL ACCESS TIME

- STATIC OPERATION

- ADDRESS LATCHES

- TTL/DTL COMPATIBLE INPUTS

- TTL/DTL COMPATIBLE THREE STATE OUTPUTS

- V<sub>CC</sub> = +5V, V<sub>GG</sub> = −12V

- 24-PIN SILICONE DIP

- SIGNETICS P-MOS SILICON GATE PROCESS TECHNOLOGY

APPLICATIONS

MICRO-PROGRAMMING

CODE-CONVERSION

#### BIPOLAR COMPATIBILITY

All inputs of the 2530 can be driven directly by standard bipolar integrated circuits, (TTL, DTL, etc.). The data output buffers are capable of sinking a minimum of 1.6mA sufficient to drive one standard TTL load.

#### STANDARD TRUTH TABLES

The 2530NX/CM3530 is an ASCII-EBCDIC and EBCDIC-ASCII code converter. Use this device for evaluation or for applications requiring this conversion. Other standards will be announced as they become available.

#### PART IDENTIFICATION

| PART  | OP. TEMP. RANGE | PACKAGE             |  |  |

|-------|-----------------|---------------------|--|--|

| 2530N | 0-70°C          | 24-Pin Silicone DIP |  |  |

| 25301 | 0-70°C          | 24-Pin Ceramic DIP  |  |  |

# SILICON GATE MOS 2500 SERIES

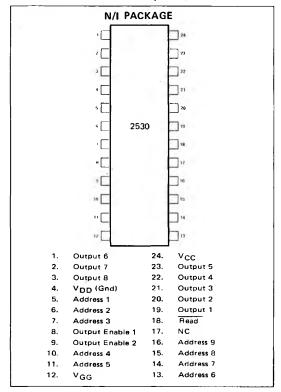

# PIN CONFIGURATION (Top View)

## **BLOCK DIAGRAM**

# **CUSTOM TRUTH TABLES**

See page 7-196.

# **MAXIMUM GUARANTEED RATINGS (1)**

Operating Ambient Temperature

0°C to 70°C -65°C to +150°C Package Power Dissipation<sup>2</sup> @ 70°C

730mW +0.3 to -20V

Input<sup>3</sup> and Supply Voltages with respect to VCC

Storage Temperature

# DC CHARACTERISTICS

$T_{\Delta}=0^{\circ}$  to  $+70^{\circ}$ C,  $V_{CC}=+5V$ ;  $V_{GG}=-12V\pm5\%$ ; unless otherwise noted. (See notes 4,5,6,7)

| SYMBOL          | TEST                     | MIN | TYP | MAX  | UNIT | CONDITIONS                                     |

|-----------------|--------------------------|-----|-----|------|------|------------------------------------------------|

| ILI             | Input Load Current       |     | 10  | 500  | nA   | $V_{1N} = -5.5V$ $T_A = 25^{\circ}C$           |

| ILO             | Output Leakage Current   |     | 10  | 1000 | nA   | V <sub>OUT</sub> = 0V<br>T <sub>A</sub> = 25°C |

|                 |                          | ĺ   |     |      |      | ACE = ACC                                      |

| <sup>I</sup> CC | VCC Power Supply Current |     | 30  | 45   | mA_  | (8)                                            |

| IGG             | VGG Power Supply Current |     | 30  | 45   | mA   | (8)                                            |

| VIL             | Input Logic "0"          | -5  |     | 1.05 | V    |                                                |

| VIH             | Input Logic "1"          | 3.2 |     | 5.3  | V    |                                                |

|                 |                          |     | }   |      |      |                                                |

# **AC CHARACTERISTICS**

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ;  $V_{CC} = 5V \pm 5\%$ ,  $V_{GG} = -12V \pm 5\%$  unless otherwise noted.

| SYMBOL              | TEST                              | MIN | TYP | MAX | UNIT | CONDITIONS                                                      |

|---------------------|-----------------------------------|-----|-----|-----|------|-----------------------------------------------------------------|

| V <sub>OH</sub>     | Output Logic "zero"               |     |     | 0.8 | V    | One TTL Load                                                    |

| VOH                 | Output Logic "one"                | 3.0 |     |     | V    | One TTL Load                                                    |

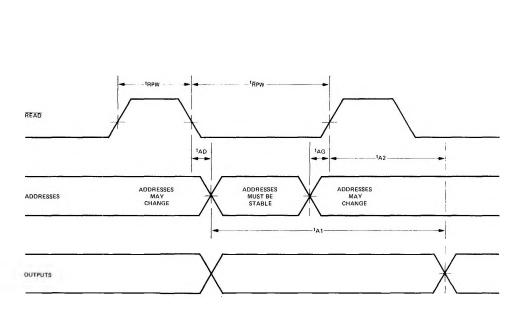

| t <sub>RPW</sub> 11 | Read Pulse Width                  | 250 | 200 |     | ns   |                                                                 |

| tRPW10              | Read Pulse Width                  | 500 | 400 |     | ns   |                                                                 |

| <sup>t</sup> AD     | Address Delay Time (12)           |     |     | 50  | ns   |                                                                 |

| <sup>t</sup> AG     | Address-Read Pulse Gap (12)       |     |     | 50  | ns   |                                                                 |

| <sup>t</sup> A1     | Address to Output Delay           |     | 625 | 700 | ns   | (9)                                                             |

| <sup>t</sup> A2     | End of Read Pulse to Output Delay |     | 200 | 250 |      | (9)                                                             |

| CIN                 | Address Input Capacitance         |     |     | 10  | pF   | - f = 1MHz,                                                     |

| <sup>t</sup> OE     | Output Enable to Output Delay     |     | 100 | 250 | ns   | V <sub>AC</sub> = 25mV p-p<br>V <sub>IN</sub> = V <sub>CC</sub> |

#### NOTES:

- 1. Stresses above those listed under "Maximum Guaranteed Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. For operating at elevated temperatures the device must be derated based on a +150°C maximum junction temperature and a thermal resistance of 110° C/W junction to ambient.

- 3. All inputs are protected against static charge

- 4. Parameters are valid over operating temperature range unless specified.

- 5. All voltage measurements are referenced to ground.

- 6. Manufacturer reserves the right to make design and process changes and improvements.

- 7. Typical values are at +25°C and nominal supply voltages.

- 8. Outputs Open, t<sub>RPW</sub> = 250ns, t<sub>RPW</sub> = 500ns.

- 9. t<sub>A</sub> = 0°C to +70°C

- 10. During tape data is clocked into the output latches and the address decoders are precharged in preparation for the next cvcle.

- 11, During tape addresses are decoded and sent to the memory matrix; and the stored memory data is moved to the data inputs of the output RS latches. This data is clocked into the output latches at the end (rising edge) of the READ pulse. After tA2, data appears at the output terminals.

- 12. Addresses must be stable within 50ns after the READ line falls and must remain stable until at least 50ns before the READ line goes high.

# **TIMING DIAGRAM**

Note: All times measured from 50% points, for all input waveforms tr =  $t_f$ <10nsec.