10113B, F: -30 to +85°C, CERDIP

# DIGITAL 10,000 SERIES ECL

#### DESCRIPTION

The 10113 is a four gate array designed to provide the positive logic Exclusive OR function in high performance applications. This device contains a temperature compensated internal bias which insures that the threshold point remains in the center of the transition region over temperature. Input pulldown resistors eliminate the need to tie unused inputs to VEE.

Open emitter outputs are provided to enable bussing of multiple outputs together. If the four outputs of the 10113 are wire-ORed together the device performs a 4-bit compare function (outputs low for compare).

The outputs are all gated by the enable input. If this enable input is high all outputs will be forced low.

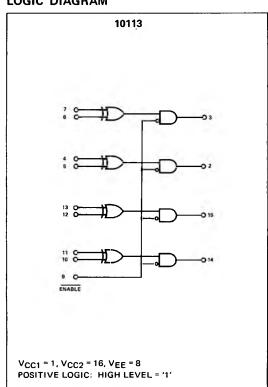

#### LOGIC DIAGRAM

#### **FEATURES**

- PERFORMS 4-BIT COMPARE FUNCTION (IF OUT-PUTS ARE WIRE- ORed TOGETHER)

- HIGH FUNCTIONAL DENSITY FOUR EXCLU-SIVE OR GATES/PACKAGE

- FAST PROPAGATION DELAY FOR EXCLUSIVE OR: 2.5 ns TYP

- LOW POWER DISSIPATION: 165 mW/PACKAGE TYP (NO LOAD)

- HIGH FANOUT CAPABILITY CAN DRIVE FOUR 50  $\Omega$  LINES

- HIGH Z INPUTS INTERNAL 50 kΩ PULLDOWNS

- HIGH IMMUNITY FROM POWER SUPPLY VARIA-TIONS: VEE = -5.2 V ±5% RECOMMENDED

- OPEN EMITTER LOGIC AND BUSSING CAPABILITY

- OUTPUT ENABLE GATING MAKES POWERFUL LOGIC FUNCTION

#### **APPLICATIONS**

- QUAD EXCLUSIVE-OR (For parity, error correcting, and other logic functions).

- FOUR-BIT COMPARATOR (For logic, test equipment, error detection applications).

- GATED FOUR-BIT COMPARATOR (Enable input permits wire-ORing multiples of four bits)

### TRUTH TABLE

| E9 | IN 7 | IN 6 | OUT 3 |

|----|------|------|-------|

| L  | L    | L    | L     |

| L  | L    | н    | н     |

| L  | н    | L    | н     |

| L  | н    | н    | L     |

| н  | φ    | φ    | L     |

$\phi$  = Don't Care.

#### **TEMPERATURE RANGE**

-30 to +85°C Operating Ambient

#### **PACKAGE TYPES**

- B: 16-Pin Silicone DIP

- F: 16-Pin CERDIP

# **ELECTRICAL CHARACTERISTICS**

(at Listed Voltages and Ambient Temperatures).

|             | TEST VOLTAGE VALUES |         |          |          |      |  |  |  |  |  |  |  |  |

|-------------|---------------------|---------|----------|----------|------|--|--|--|--|--|--|--|--|

| @ Test      |                     | (Volte) |          |          |      |  |  |  |  |  |  |  |  |

| Temperature | VIH max             | VIL min | VIHA min | VILA max | VEE  |  |  |  |  |  |  |  |  |

| -30°C       | -0.890              | -1.890  | -1.205   | -1.500   | -5.2 |  |  |  |  |  |  |  |  |

| +25^C       | -0.810              | -:1.850 | 1.106    | -1.475   | -5.2 |  |  |  |  |  |  |  |  |

| +86°C       | -0.700              | -1.825  | -1.035   | -1.440   | -5.2 |  |  |  |  |  |  |  |  |

| Characteristic S                            |        | Pin             | 10113 Test Limits |        |       |       |        |        |        |             | TEST VOLTAGE APPLIED TO PINS LISTED BELOW: |         |           |           |        | ĺ      |

|---------------------------------------------|--------|-----------------|-------------------|--------|-------|-------|--------|--------|--------|-------------|--------------------------------------------|---------|-----------|-----------|--------|--------|

|                                             |        | - Under<br>Test | -30°C             |        | +25°C |       | +85°C  |        |        | <del></del> |                                            |         |           |           |        |        |

|                                             | Symbol |                 | Min               | Mex    | Mir   |       | Mex    | Min    | Мэк    | Unit        | VIH max                                    | VIL min | VIHA min  | VILA mex  | VEE    | Gnd    |

| Power Supply Drain Current                  | ΙE     | 8               | -                 | -      | -     |       | 40     | -      |        | mAdc        | -                                          | -       | -         | -         | 8      | 1,16   |

| Input Current                               | linH   | 6.7             | -                 | -      | -     |       | 265    | -      |        | μAric       | 6,7                                        | -       | -         | -         | 8      | 1,16   |

|                                             |        | 9               | -                 | 2-1    | -     |       | 720    | -      |        | μAdc        | 9                                          | -       |           | -         | 8      | 1,16   |

|                                             | linL   | •               |                   | -      | 0.5   | П     | _      | - '    | -      | µAdc        |                                            |         |           | -         | 8      | 1,16   |

| Logic "1" Output Voltage Vo                 | Voн    | 3               | -1.060            | -0 890 | -09   | 30 -  | -0.810 | -0.890 | -0.700 | Vdc         | 6                                          | -       | -         |           | 8      | 1,16   |

|                                             |        | 3               | -1.060            | -0 890 | -09   | - 00  | -0,810 | -0 890 | -0.700 | Vdc         | , ,                                        | -       | -         | -         | 8      | 1,16   |

| Logic "0" Output Valtage VOL                | VOL    | 3               | -1.890            | -1,675 | -1.89 | 50 -  | -1 660 | -1.825 | -1.615 | Vdc         | -                                          | -       | _         | -         | 8      | 1,16   |

|                                             | 1      | 3               | -1.890            | -1,675 | -1.8  | 50 -  | -1.650 | -1.825 | -1,615 | Vdc         | 6,7                                        | -       | -         | -         | 8      | 1,16   |

| Logic "1" Threshold Voltage VOH             | VOHA   | 3               | -1.080            | (      | -0.98 | 30    | _      | -0.910 |        | Vdc         | 1-1                                        | (44)    | 6         |           | 8      | 1,16   |

|                                             | L      | 3               | -1.080            |        | -0.98 | 30    | -      | -0.910 |        | Vdc         | -                                          | -       | 7         | -         | 8      | 1,16   |

| Logic "0" Threshold Voltage                 | VOLA   | 3               |                   | -1.655 | _     | T-    | 1.630  |        | -1.595 | Vdc         | 7                                          | -       | 6         | -         | 8      | 1,16   |

|                                             |        | 1 3 )           | 120               | -1,665 |       | - ) - | -1,630 |        | -1.595 | Vdc         | 5-0                                        | 1ec     |           | 6         | - 8    | 1.16   |

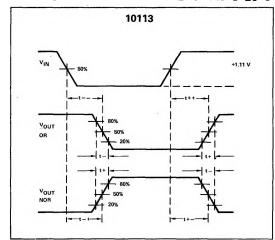

| Switching Times <sup>†</sup><br>(60 Ω load) |        |                 |                   |        | Min   | Тур   | Max    |        | ,      | Unit        | +1.11 V                                    |         | Pulse In  | Pulse Out | -3.2 V | +2.0 \ |

| <del></del>                                 | 1++    | 3               |                   | ì      | 1     | 2.5   |        |        | i      | ns          | -                                          |         | 6         | 3         | 8      | 1,16   |

|                                             | 1+-    | 1 1 1           |                   | ł      | ł     | 1     | 1      | 1      |        | l i         | 7                                          | -       | -         | -         | 1 .    | 1 .    |

|                                             | t=+    | 1 1 1           |                   |        | l     | 1     | i      |        |        | 1 1         | 7                                          | -       |           | -         | 1 1    | 1 1    |

|                                             | t      | '               |                   |        | l .   | ,     |        |        |        | 1           | -                                          | -       | -         | -         | ' '    | , ,    |

|                                             | t+-    | 2,3,14.15       |                   |        |       | 2.7   |        |        |        |             | 4,7,11,13                                  | -       | 9         | 2,3,14,15 |        |        |

|                                             | t-+    | 1 1             |                   | ľ      | ĺ     | 2.7   |        | ľ      |        | ĺι          | 1-0                                        | -       | ~         | -         | 1 1    | 1 1    |

| Rise Time (20% to 80%)                      | 1+     | 1 1 1           |                   |        | l     | 2.5   | 1      |        |        | 1 1 -       | -                                          | _       | Any Input | -         |        | 1      |

| Fall Time (20% to 80%)                      | 1-     | 1 7 1           |                   | l      | l     | 2.5   | 1      | I      |        | , T         | 7 <del>-0</del> 1                          | -       | Any Input |           |        | ١ ٢    |

<sup>\*</sup>Individually test each input applying VIH or VII to input under test

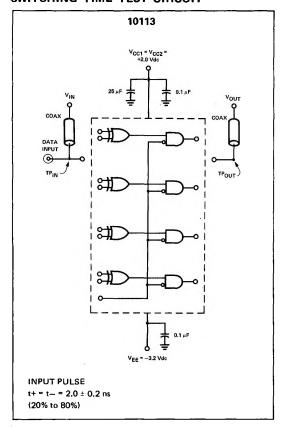

#### SWITCHING TIME TEST CIRCUIT

## PROPAGATION DELAY WAVEFORMS @ 25°C

#### NOTES:

- 1. Each ECL 10,000 series device has been designed to meet the DC specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a linear printed circuit board and transverse air flow greater than 500 fpm is maintained. Voltage levels will shift approximately 4 mV with an air flow of 200 linear fpm, Outputs are terminated through a 50-ohm resistor to -2.0 volts.

- 2. For AC tests, all input and output cables to the scope are equal lengths of 50-ohm coaxial cable. Wire length should be < 1/4 inch from  $\mathrm{TP}_{in}$  to input pin and  $\mathrm{TP}_{out}$  to output pin. A 50-ohm termination to ground is located in each scope Input, Unused outputs are connected to a 50-ohm resistor to ground.

- 3. Test procedures are shown for only one input or set of input conditions. Other inputs are tested in the same manner.

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

<sup>\*\*</sup>Any Output †Unused outputs connected to a 50-ohm resistor to ground,